Special Report: Powering Industrial Applications (pg 37)

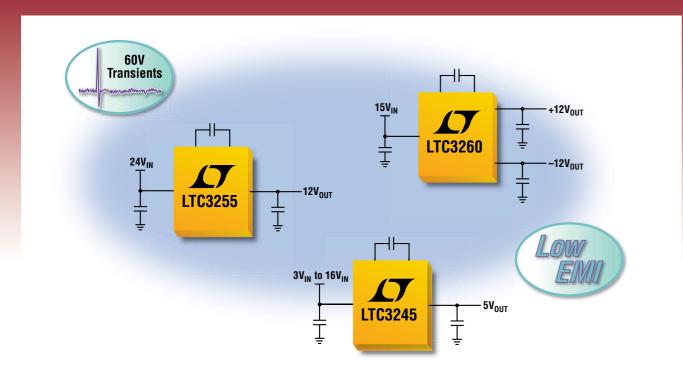

### Charge Pumps Go High Voltage

#### Buck, Buck-Boost, Inverting-No Inductor

Our new family of high voltage charge pumps simplifies the design of DC/DC power supplies by eliminating the need for an inductor and requiring only a capacitor as the external storage element. These devices provide output currents up to 250mA and conversion topologies including buck, inverting and buck-boost. Their wide input voltage range of 2.7V to 48V and 60V transient ride-through and wide operating temperature range (up to 150°C) make them ideal for automotive, industrial and medical applications.

#### **▼** High Voltage Charge Pumps

| Part<br>Number | V <sub>IN</sub> Range | Quiescent<br>Current | Max I <sub>out</sub> | LDO<br>Follower | Topology           |  |

|----------------|-----------------------|----------------------|----------------------|-----------------|--------------------|--|

| LTC®3255       | 4V to 48V             | 16µА                 | 50mA                 |                 | Buck               |  |

| LTC3245        | 2.7V to 38V           | 18µА                 | 250mA                |                 | Buck-Boost         |  |

| LTC3260        | 4.5V to 32V           | 100μΑ                | 2 x 50mA             | <b>✓</b>        | Dual: Inverter/LDO |  |

| LTC3261        | 4.5V to 32V           | 60μΑ                 | 100mA                |                 | Inverter           |  |

#### **▼** Info & Free Samples

www.linear.com/hvchargepumps 1-800-4-LINEAR

T, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

**Empowering Global Innovation**

#### WWW.POWERSYSTEMSDESIGN.COM

Visit us online for exclusive content; Industry News, Products, Reviews, and full PSD archives and back issues

<sup>2</sup> **VIEW**point

The new industrial revolution By Alix Paultre, Editorial Director, Power Systems Design

4 POWERline

Farsen's TITAN battery-free bistable RFID relay triggers wirelessly

POWERplayer

Network Convergence Design Strategies By George Kairys, Molex

8 MARKETwatch

Life to Return to the Power Supply Industry in 2014 By Jonathon Eykyn, IHS Technology

9 DESIGNtips

Power supply failure survey - Part II By Dr. Ray Ridley, Ridley Engineering

#### **COVER STORY**

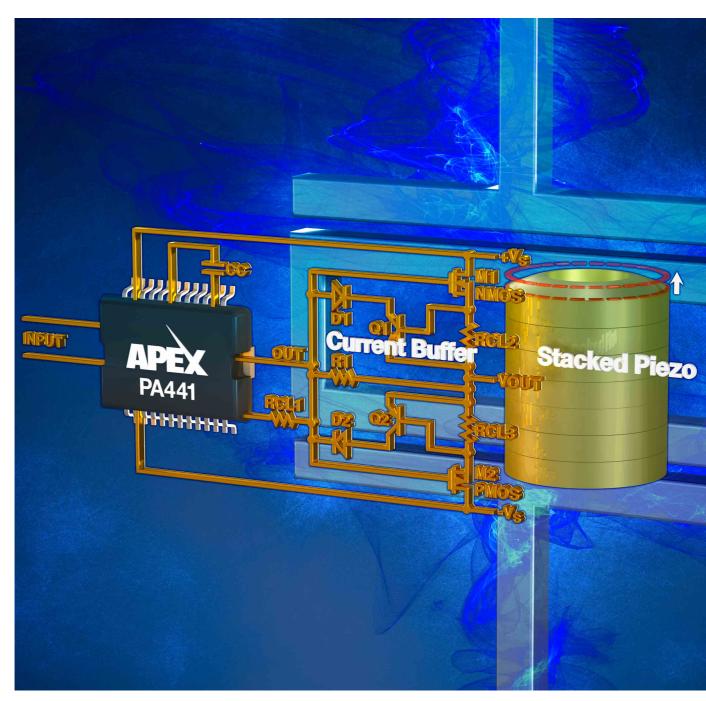

Boosting output in high-voltage op-amps with a current buffer

By Joe Kyriakakis, Apex Microtechnology

#### TECHNICAL FEATURES

Manufacturing & Assembly

Focused Ion Beam circuit edit improves power device design By Taqi Mohiuddin, EAG 23 Automotiv

Using the right power semiconductors can increase your power density By Jifeng Qin, International Rectifier

Serving the Power Grid

How smart is the Smart Grid when the computer crashes? By Edward Herbert

Serving the Power Grid

Optimizing Smart Grid Power Connection Functionality By Chris Siegl and Aung Tu, Fairchild Semiconductor

Power Supplies

Advanced packaging critical to power system performance

By Doug Ping, Vicor

#### SPECIAL REPORT:

POWERING INDUSTRIAL APPLICATIONS

Digital power cuts time-to-market for industrial applications

By Patrick Le Fèvre, Ericsson Power Modules

Digital power management without code qualification

By Frederik Dostal, Analog Devices

Optimizing Rack Power

Distribution with Advanced PDUs

By Joe Skorjanec, Eaton

#### **COVER STORY**

Boosting output in high-voltage op-amps with a current buffer (pg 12)

Highlighted Products News, Industry News and more web-only content, to:

www.powersystemsdesign.com

HV underground cable aids substation expansions with space constraints

By Peter Ebersold, Marmon Utility

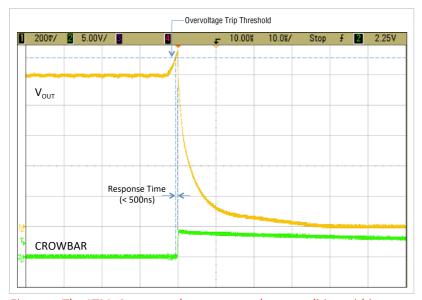

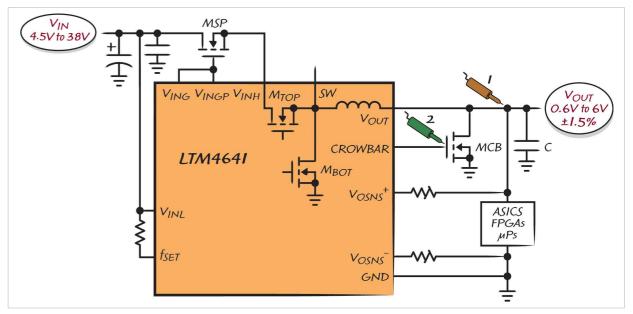

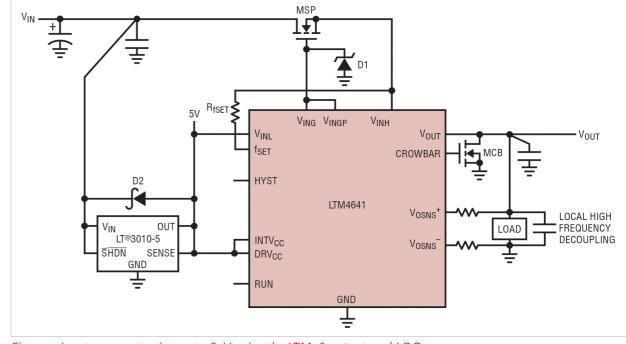

Powering low-voltage devices from an intermediate-bus voltage

By Willie Chan & Jason Sekanina, Linear Technology

GREENpage

Don't forget the main reason to migrate to green tech is a green planet By Alix Paultre, Editorial Director, PSD

Dilbert

#### AGS Media Group

146 Charles Street Annapolis, MD 21401 USA Tel: +410.295.0177 Fax: +510.217.3608 www.powersystemsdesign.com

#### **Editorial Director**

Alix Paultre, Editorial Director, Power Systems Design alixp@powersystemsdesign.com

#### **Contributing Editors**

Liu Hong, Editor-in-Chief, Power Systems Design China powersdc@126.com

Ryan Sanderson, IMS Research ryan.sanderson@imsresearch.com

Dr. Ray Ridley, Ridley Engineering RRidley@ridleyengineerng.com

#### **Publishing Director**

jim.graham@powersystemsdesign.com

#### **Publisher**

Julia Stocks

Julia.stocks@powersystemsdesign.com

#### **Production Manager**

Chris Corneal powersystemsdesign.com

#### **Circulation Management**

Christie Penque christie.penque@powersystemsdesign.com

#### Magazine Design

Louis C. Geiger louis@agencyofrecord.com

Registration of copyright: January 2004 ISSN number: 1613-6365

AGS Media Group and Power Systems

Corporation and Power Systems Design

Magazine assume and hereby disclaim any

liability to any person for any loss or damage by

errors or ommissions in the material contained

herein regardless of whether such errors result

from negligence, accident or any other cause

whatsoever.

Free Magazine Subscriptions, go to: www.powersystemsdesign.com

Volume 6, Issue 02

## The new industrial revolution

Industrial technology and processes have been under constant development since the invention of the wheel. From the potter's wheel came the lathe, fire went from cooking to pottery to steam, and precision went from rough measurements based on body parts and other natural comparators to rulers and levels. The tools get better, then the processes get better, than the precision improves, then the cycle begins again.

Sometime that process of change and development is smooth, and sometimes it's precipitous. Usually with every significant advance, there is a disruptive period of challenge and resistance. On rare occasions, that advance is a technology or procedure that the entire industry wants and needs, enabling growth with minimal pain. The migration to intelligent industrial systems is one of those developments.

#### **Smart factories**

The drive to smart factories, facilities, and systems has been an evolutionary one, as the primary disruptive aspects of the consumer marketplace are not as influential in the industrial space. Industry has different needs than consumers, so while some aspects of the consumer technology revolution strongly impact industry, they do so in ways differently than they impact consumer markets

For example, the explosion in personal electronics and the resulting pressures on RF power, battery management, and device miniaturization have only peripherally hit industrial systems in the same manner. Areas such as control systems and portable test devices may shrink and become portable, but the real impact in industrial systems is the ability to insert logic into every powered subsystem in the facility and link them to central command and control through web-based communications infrastructures for enhanced performance and improved reliability.

#### Better tools

Improved motors and actuators enable more precise processes, improved sensors and microcontrollers enable precise measurement, and improved control systems allow the two to work optimally together for the best result at the highest efficiency. Even the most stubborn manufacturer can see the performance as well as financial advantages to upgrading a facility with smart automation and control solutions today.

This month's issue has some interesting items on industrial systems for your enlightenment. From Linear Technology we have an article on powering low-voltage devices, dealing with properly handling the intermediate bus voltages commonplace in industrial systems where series-connected batteries may be a backup power source and 12V bus architectures tend to be impractical due to distribution losses. We've also got an item from Eaton on optimizing rack power distribution, and something from Exar on programmable power for industrial applications.

Best Regards,

#### Alix Paultre

Editorial Director, Power Systems Design alixp@powersystemsdesign.com

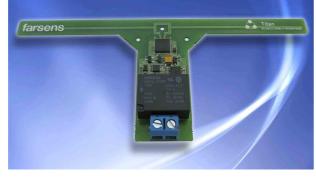

## Farsens' TITAN battery-free bistable RFID relay triggers wirelessly

he TITAN from Farsens is a battery free RFID bistable relay tag compatible with commercial EPC C1G2 readers. They can be wirelessly activated and deactivated via their unique ID and the relay keeps its latest status even when the RFID reader is gone.

The TITAN has a 96 bits EPC number, a 32-bit TID and a password protected Kill command. Built in a PCB format, it is available in different sizes. The communication range is up to 1.5 meters and the operating temperatures are from -30°C to  $+85^{\circ}$ C (-22°F to  $+185^{\circ}$ F). These actuator tags are available in a variety of antenna design and sizes, depending on the specific application. It can be encapsulated in an IP67 or IP68 casing for usage in harsh environments.

The fact that the actuator is full passive makes these relays ideal for hardly accessible or restricted areas and those where the use of batteries is not recommended. The TITAN will never require a battery change, saving the costs associated to maintenance. The TITAN tag consists of a ANDY100 IC for energy harvesting and wireless communication,

an G6CU-2114P-US relay, an MSP430 microcontroller and start-up circuitry based on the AX6427 IC from Maxim Integrated.

In order to read the EPC of the TAG, commercial EPC C1G2 readers can be used. However, some considerations have to be taken into account. As the tag has a large supply capacitor connected to VDD, the power-up of the system can be slow, lasting several seconds. In order to speed up the charge process, the reader can be configured to send power as continuously as possible. Once the supply capacitor is charged, the TAG will respond with its EPC. From this point on, memory access commands can be used to control the G6CU-2114P-US relay via the SPI bridge.

TITAN tags are used in energy scarce applications where the stored energy is limited and the system/circuit is controlled via a wireless battery-free relay. The circuit can be opened and closed from a commercial RFID reader. The bistable relay allows the system to run so that the limited

battery is only switched on during the time the user actually needs it to be running.

Battery-free relays are also a good fit for retrofitting in places where lots of mechanical relays are being manually operated. The fact that each relay is uniquely identified by its ID number makes automation a lot easier and activation/deactivation can easily be implemented in easy-to-use reader software. Mistakes due to human intervention can be reduced to the minimum this way.

Farsens designs and manufactures full passive RFID sensor solutions. Their proprietary UHF RFID IC allows Farsens to develop long-range solutions for asset tracking – via the unique ID – and monitoring – via the attached sensor – without the need of any battery on the tag.

www.farsens.com

## When it comes to Inductors SMALLER IS BETTER

Visit www.RencoUSA.com/catalog-request to get your copy today.

Actual size.

## Network Convergence Design Strategies

By: George Kairys, Molex

Industrial network convergence necessitates a high degree of integration of hardware and software. Lately we've seen a trend towards extending Ethernet to the plant as the link-layer protocol to one or more of the legacy protocol applications, and even extending Ethernet down to the device level on the machines. Technology advancements have set the stage for convergence, offering network tools to effectively link machine processes, control systems and plant-wide information to the enterprise.

#### **Convergence Strategies**

Unlike proprietary protocols commonly used in years past, industrial Ethernet is built on a standard Ethernet structure and Transmission Control Protocol/ Internet Protocol (TCP/IP) standards, which allow computers to share resources across a single local area network. TCP/IP also facilitates rapid and accurate file transfer and user communications on both the commercial and industrial sides.

At the plant level, Industrial process control and automation typically require more stringent

real-time data transmission rates. Ethernet not only improves transmission speed, it can span distances and accept more devices without performance degradation often seen in prior network technology. Examples of industrial Ethernet platforms include PRO-FINET, Profibus and EtherNet/IP.

Industrial Ethernet uses twisted pair cable, fiber optics, wireless networks, and may also include Power-over-Ethernet (PoE) where power passes along with the data. In addition to physical layer components, system designers also need to carefully consider network architecture, as well as interoperability, security, and data management, to enable convergence to work efficiently today and allow for future expansion.

The right network architecture can effectively link business management to plant floor controllers such as PLCs, PACs and PCs, which control operation and collect data from machines and devices. However, ubiquitous data transparency can be both empowering and overwhelming, depending on how it is used.

Real-time raw data from the plant

typically doesn't reach management level, nor does it need to. Translating raw production data into usable intelligence for management is likely the most challenging hurdle for companies seeking to converge on Ethernet and here, too, technology is the enabler. To manage plant floor data effectively, various types of executive dashboards and other business intelligence and analysis software can help to filter data and focus on key metrics and performance indicators and other information needed for high-level decision-making.

#### **Benefits of Convergence**

The benefits of plant and enterprise convergence depend largely on the network configuration and the strategies driving a company's decision to integrate these two sectors. Significant business and operational advantages include improved efficiency and resource management, faster data transmission, enterprise-wide increased business intelligence, improved equipment monitoring and control, and the ability to meet secure real-time data traffic requirements.

www.molex.com

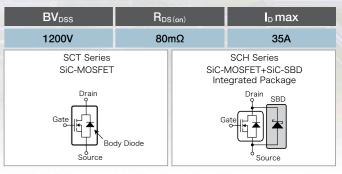

#### **Choose ROHM SiC Products for Your Power Component Needs**

Class-leading SiC power components are available in a range of output currents. From SiC ingots to finished components, we offer a one-stop production and development system that guarantees a stable supply of high-quality SiC power products.

#### ■ Full SiC Power Modules

#### Specifications: 45.6×122×17mm(Including pins)

| BV <sub>DSS</sub> | I <sub>D</sub> max | Structure: Half-Bridge Circuit |  |

|-------------------|--------------------|--------------------------------|--|

|                   |                    | BSM120D12P2C005                |  |

|                   | 120A               |                                |  |

| 1200V             |                    | BSM180D12P2C101                |  |

|                   | 180A               |                                |  |

#### **■ SiC MOSFETs**

#### T0-247

#### ■ SiC Schottky Diodes

#### TO-220AC 2L

| $V_{R}$ | l <sub>F</sub> |  |  |

|---------|----------------|--|--|

| 650V    | 6~20A          |  |  |

| 1200V   | 5~20A          |  |  |

#### T0-220FM 2L

| $V_{R}$ | I <sub>F</sub> |

|---------|----------------|

| 650V    | 6~20A          |

|         |                |

#### T0-247

| $V_R$ | <b>I</b> <sub>F</sub> |

|-------|-----------------------|

| 650V  | 10~20A*1<br>20~40A*2  |

| 1200V | 5~20A*1<br>10~40A*2   |

|       | 5~20A*¹               |

#### D2PAK

| 0A *1<br>0A *2 |  |

|----------------|--|

| 0A *1          |  |

| 0A *2          |  |

6~10A

■ Next-Generation SiC Power Modules (Under Development)

## Life to Return to the Power Supply Industry in 2014

By: Jonathon Eykyn, IHS Technology

he global market for power supplies crashed in 2012 as economic uncertainties led to low consumer demand and the post-ponement of large industrial projects. Whilst 2013 bought growth, it was limited to a few markets and the overall market grew by just 2.4%. However, the outlook for the global power supply market is much brighter in 2014 with the market growth projected at 4.4%.

Unlike 2013, this growth is projected to be across the board with strong growth forecast in nearly all applications. This growth will be driven by a couple of key factors. Firstly, a forecast uplift in end-equipment demand in the traditional power supply markets of telecommunications and industrial. There has been a higher business confidence across many industries despite some less than favorable economic conditions leading to postponed projects being restarted and new projects green-lighted.

The second factor is the meteoric growth of the emerging applications for power supplies. Demand for power supplies used in LED lighting and tablet PCs is projected

to grow by more than 40% in terms of units shipped.

The data communications sector is also set to grow strongly in 2014 with revenues for power supplies for servers and storage devices projected to increase by 4%. This is more than double the growth for 2013 and is driven by the need for continual refreshment of IT systems and the growth of cloud computing and associated datacenters.

This growth in the market will also be spread across all three major regions. Asia continues to grow the fasted with revenues projected to grow by almost 5% in 2014. Revenue growth for both the Americas and the EMEA regions is forecast to more than triple after a weak 2012 where growth was estimated at just over 1% for both regions. However, it is not a perfect outlook for the industry. The majority of the growth by application and region is predicted to be driven by both the AC-DC commodity and non-commodity markets.

Opportunities in the non-commodity AC-DC power supply market by power supply type in 2014 are predicted largely to mirror the demand by application. Strongest growth is forecast for power adapters and chargers at 9.6% and open-frame/enclosed power supplies at 9.3%, owing to their use in LED lighting and telecommunication applications. Whereas the market for DIN Rail noncommodity AC-DC power supplies, of which the majority are used in industrial applications, is forecast to grow by just 2.4%.

The DC-DC converter market was the worst hit in 2012 and the market remained almost flat in 2013. It is forecast that overall revenue growth in the DC-DC market in 2014 will be at around 1% although unit shipments will grow by almost 4%. Part of the reason for the slower recovery of the DC-DC converter market is that many of the 'hot' applications that are helping to drive overall market growth at the moment such as LED lighting and tablets are predominately an AC-DC opportunity. The longerterm forecast for DC-DC converters is slightly better, with an average annual growth rate of 2% for the 2014-2017 period but this is still behind the rest of the global power supply market.

www.ihs.com

## Power supply failure survey – Part II

By: Dr. Ray Ridley, President, Ridley Engineering

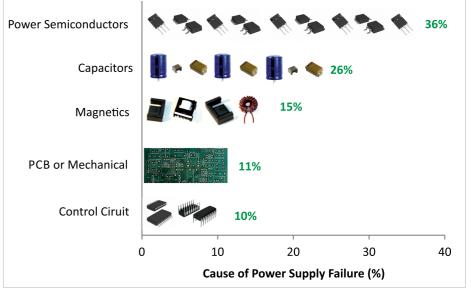

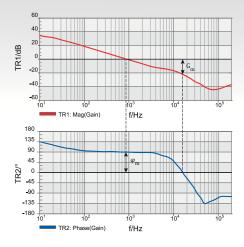

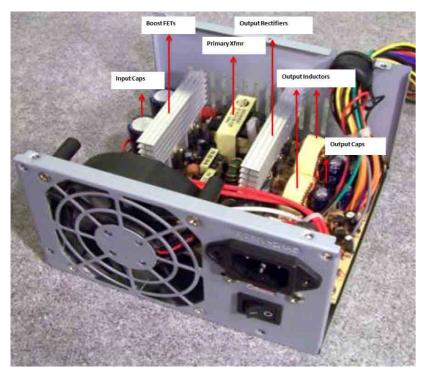

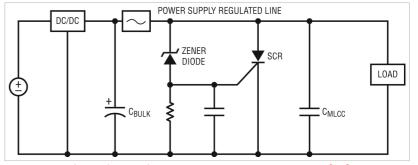

n this second article about power supply failures, the capacitors are examined for their contribution to the failure rate. The causes of failure for different types of capacitors are discussed. In the last part of this article, the question was asked of group members "Why do power supplies fail?" and the results of the survey are repeated in **Figure 1** below.

The survey group saw semiconductors as the main cause of failures, and this was discussed in the last article of this series. Second on the list are capacitors. In this article, we will look at the issues that

look at the issues that cause capacitor failures.

#### **Power Capacitor Failures**

While semiconductors topped the list of failures, they are usually very well documented components. Avoiding semiconductor failure is usually a matter of keeping voltage, current, and thermal stresses below the published limits in the datasheets. Capacitors have many different failure

mechanisms. Overvoltage will cause failure for some types of capacitor, but the current rating is greatly variable. Current-carrying capability is dependent upon the type of capacitor, lifetime required, package, environment, and many other factors. Designing a capacitor into your power system and maintaining reliability over the long term is a challenging task in many applications. It is important to devote proper time and care to the selection of parts.

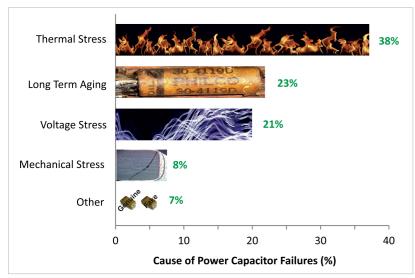

**Figure 2** shows the results for the causes of capacitor failures.

These are summarized as follows:

Thermal Stress: 50% Top of the list, perhaps surprisingly, is thermal stress. Many designers have learned over years of experience that capacitors will fail if kept too hot for too long. Since capacitors are usually in the vicinity of hot semiconductors, they are frequently exposed to temperatures well in excess of ambient. In optimizing highfrequency board layout, it is important to keep current loops small and tight. This implies that the capacitors must be kept as close as possible to the power

Figure 1: Survey Results for the Cause of Power Supply Failures

ç

Figure 2: Survey Results for Causes of Capacitor Failures

switches. This also exacerbates the thermal problem.

Long-Term Aging: 23% Second in the list is long-term aging. This comes from experience with predominantly electrolytic capacitors which dry out over time, especially when placed in a hot environment.

Voltage Stress: 21% Depending upon the type of capacitor, they can be relatively tolerant of overvoltage events. Once again, electrolytics have dominated our industry until recently, and they usually come with a surge rating that lets you briefly exceed the voltage rating. Some of them will even recover after a failure. Other capacitor types are usually much less tolerant of overvoltage.

Mechanical Stress: 8% Much lower on the list is mechanical stress. This can apply to any

type of capacitor.

Other: 7% A multitude of reasons make up the last category. Included in here is the same problem seen with semiconductors – counterfeit parts.

#### Power Capacitor Types

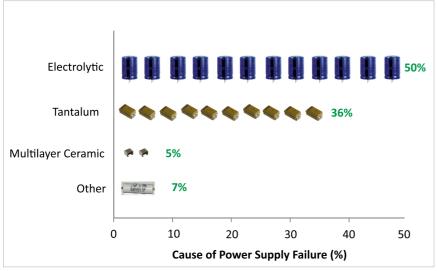

To understand the statistics for the failure mechanisms of **Figure** 2, it is important to split the capacitor failure problem into the different types of capacitor technology. A second part of the capacitor failure survey was run to ask which type of capacitors are most likely to fail. The results of this are shown in **Figure 3**.

**Electrolytics: 50%** Electrolytics are used more than any other type of capacitor, so not surprisingly they experience the most failures. The biggest problem with electrolytics is maintaining the electrolyte inside the component. Great advances have been made in technology to provide longer lifetimes and better seals. Ultimately, however, high temperatures inside the capacitor due to ambient temperature or high currents will cause loss of electrolyte over time. When enough loss has occurred, the ESR of the capacitor rises, temperatures climb further, and the part will eventually fail.

Figure 3: Survey Results for Type of Capacitor Most Likely to Fail

Tantalums: 36% Tantalum capacitors are an interesting case study in the power supply industry. Most engineers in our industry have heard the expression that you "need to let the smoke out" of power components—a humorous reference to failed components. One of the LinkedIn group attendees made the wry observation that with tantalum capacitors, you need to "let the fire out". This refers to the rather alarming fact that the failure of a tantalum can be a very dramatic event that will incinerate other components and board material in the vicinity of the failed tantalum part.

What is even more alarming is that most designers feel that tantalums should be heavily voltage derated, as much as 50%, if the parts are to be reliable. Some manufacturers even go as far as derating the nameplate rating deliberately by this amount in order to get ruggedness. Other manufacturers will suggest putting large current-limiting resistors in series with the capacitors, which of course defeats the purpose of using them in a power environment in the first place. Despite this, tantalums continue to be used since they provide low ESR without the problem of electrolyte loss. They provide high values of capacitance that multilayer ceramics do not yet match.

You should be very careful if using tantalums for the first time. A 50% voltage derating is definitely encouraged, and you might want to check with experienced engineers to find out which manufacturers make the most rugged parts. The vagueness of exactly how to use and derate tantalums safely is something that probably would not be tolerated in any other type of component, and certainly not in semiconductors. The data sheets simply do not provide enough information to avoid all

the hazards.

Multilayer Ceramics: 5% There are two main reasons for failure of MLC capacitors. First, is overvoltage, for which these capacitors have no tolerance. Always stay below the stated voltage rating. Large MLC capacitors are used frequently these days in high power applications. The big packages suffer from the problem of mechanical stress since they are not flexible. Special mounting techniques have been introduced by manufacturers to relieve stress on the large parts. Anything above a 1210 package must be mechanically designed for its proper mechanical and thermal stresses.

Other Types: 7% There are many other types of capacitors, usually used in high-power or specialist applications that can lead to various types of failure modes. Mechanical stress is often high

on the list of causes.

#### Summary

The survey results in this article highlight the major causes of capacitor failures in switching power supplies. There are no perfect capacitors. Tantalum, electrolytic, and multilayer ceramic capacitors all have their own unique ways of breaking down. Each of them must be carefully considered when they are used in power environments.

Much research continues to be done by capacitor vendors to improve their parts, but failures still continue to be a significant problem. There are many other considerations to capacitor application not mentioned in this article, and it is recommended that you study datasheets and application notes very carefully during your design.

#### www.ridleyengineering.com

#### References

- LinkedIn group "POWER SUPPLY DESIGN CENTER" www.linkedin.com/ groups?gid=4860717

- 2. Ridley Engineering website www.ridleyengineering.com

- Power supply workshops and training http://www. ridleyengineering.com/ workshops.html

## Boosting output in high-voltage op-amps with a current buffer

Creating a composite op-amp brings its own set of challenges

By: Joe Kyriakakis, Apex Microtechnology

elivering more than 200mA of output current can be a serious challenge for many high-voltage operational amplifiers. However, when it comes to high-voltage applications requiring as much as 1A of current, it is possible to meet this spec by pairing a current buffer with the op amp. What the current buffer brings to this arrangement is approximate unity voltage gain when it's placed between the output of the high voltage op amp and the load. This means the current buffer is included in the feedback loop of

But creating such a composite op amp does come with its own set of design challenges. These challenges begin with the current buffer's output stage bias circuit. Usually a Class B output stage is adequate for some applications, but such a solution has a characteristic crossover distortion as the low-

the op amp to create a composite op amp.

side device output current transitions to the high-side device. The preferred scenario is to use a Class AB output stage as the crossover distortion is much lower and the feedback loop remains closed during the transition. But setting the quiescent current of the Class AB output stage is difficult because of output device variations and sensitivities.

The current buffer design approach that we will explore here makes it possible to avoid many of the design difficulties related to output stage biasing by incorporating a depletion mode MOSFET as the high side driver. The benefits of this circuit topology are due to the MOSFET's ability to provide the bias current by using it as a current source. The depletion-mode MOSFET then serves as both the bias current generator and the high side driver.

#### **Building A Better Buffer**

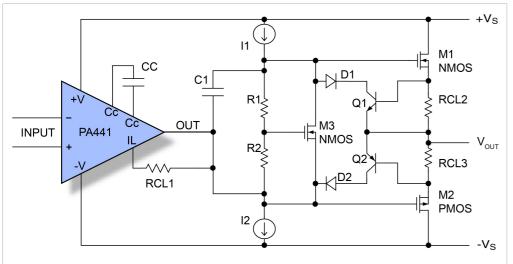

The Class B circuit shown in Figure 1 illustrates one common method of implementing a current buffer. In this circuit diagram, the resistor R1 provides

Figure 1: Class B circuit showing one common method of implementing a current buffer

## "Superinductors"

## That's what engineers are calling our new ultra-low DCR power inductors

Super*con*ductors pass current with virtually no resistance.

Our new XAL/XFL inductors do much the same. Their DCR is incredibly low: often half that of similar size parts.

And their current handling is equally impressive. Coilcraft's proprietary core material has a soft saturation characteristic that

Competitors' 4.7uH inductors have much higher DCR per mm<sup>3</sup>

prevents drastic inductance drops during current spikes.

Unlike competitive parts, these inductors don't suffer from thermal aging. And we give you far more footprint options to maximize PCB density.

To see what else makes our new XAL/XFL inductors so super, visit **coilcraft.com/xal.**

Figure 2: Conventional circuit topology of a Class AB current buffer output stage

a current path to the load from the high voltage op amp (PA441) and is set to limit the maximum gate voltage of the MOSFETs M1 and M2 to 10V. The resistor RCL1 is used to set the current limit value of the PA441 so that the current in R1 creates a voltage drop of 10V. The op amp current limit value should be set as low as possible to minimize the amount of power dissipation that the op amp is forced to bear. Resistors RCL2 and RCL3 are tasked with providing a level of protection for the output devices by serving to current-limit the output MOSFETs.

The output current flows through RCL2 and RCL3, creating a voltage across the base to the emitter of Q1 and Q2. Once this voltage reaches approximately 0.7V, the transistors Q1 and Q2 begin conducting current to the load, thus clamping the gate drive voltage at M1 and M2 as

Figure 3: A simplified conceptual circuit diagram of an alternative Class AB topology

the PA441 enters current-limit mode.

The conventional circuit topology of a Class AB current buffer output stage is illustrated in **Figure 2**. This is a simplified schematic diagram using a VGS multiplier composed of M3, R1 and R2 to set the required voltage at the gates of M1 and M2. This provides the desired quiescent current through the output devices M1 and M2. Constant current sources I1

is much more complex and problematic than the Class B stage design, therefore one must ensure that all of the proper elements are in place. First, additional components are required in order to implement the current sources I1 and I2, and it is important to note that the voltage swing will be less than the voltage swing of the PA441 because of the drive requirements of the output MOSFETs.

and I2 supply the required current to the VGS multiplier. The transistors Q1 and Q2 are used for current limiting the output MOSFETs, as described in the previous Class B stage example.

This Class AB design approach

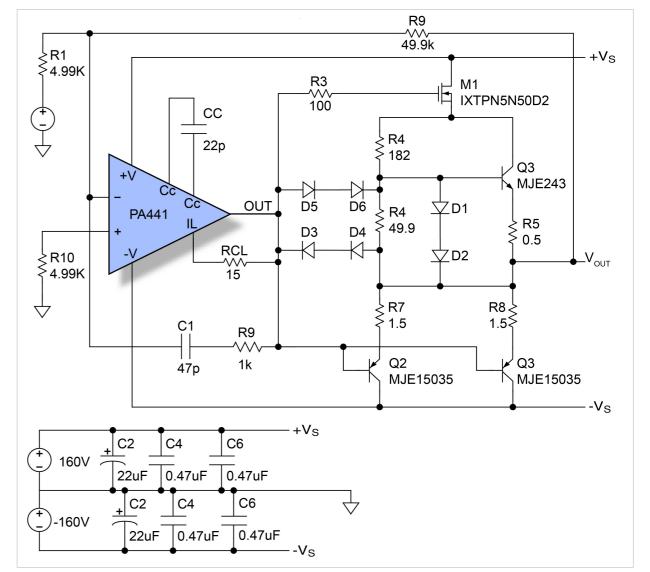

Figure 4: A prototype of the circuit schematic

In addition, setting the quiescent current through M1 and M2 is difficult because of the high sensitivity between VGS and ID. The VGS multiplier, consisting of M3, R1 and R2, must be individually adjusted for every unit. To prevent thermal runaway, the circuit relies on device matching and tight thermal coupling between M1, M2 and M3. Taking these factors into account, along

with temperature instability and sensitivity in setting the quiescent current, the actual implementation of this circuit topology is much more challenging than that of the Class B buffer version.

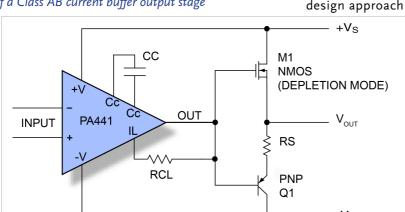

#### There Is An Alternative

Let's take a look at a simplified conceptual circuit diagram of an alternative Class AB topology, as shown in **Figure 3**. One of

the benefits to this approach is that the circuit functions in a self-biasing mode, and does not require the current sources and VGS multiplier of a conventional Class AB stage. In this example, to demonstrate the mechanism for establishing the flow of quiescent current, we will assume that the output voltage is at zero volts, while the base of Q1 must be approximately -0.7V. IN this diagram the gate

Figure 5: Output stage behavior in Class A mode operating under light load conditions

of M1 is also at -0.7V, forcing the MOSFET to conduct. The resistor RS is selected to adjust the quiescent current to the desired value. The actual prototype of this circuit schematic is shown in **Figure 4**. The depletion mode MOSFET M1 is biased to provide the quiescent current for the output stage. Resistors R4 and

dissipation. The maximum rated power dissipation of each PNP transistor is 50W. The current limit function is implemented through the addition of diodes D1 through D6. The diodes used

R5 are selected to establish the operating current of M1. The bipolar transistor Q1 acts as a Vbe multiplier to maintain the desired VGS for M1 as the demand for load current increases. That means the Q1 essentially conducts the output current sourced by M1 by bypassing R4 and R5. The bipolar transistors Q2 and Q3 are biased by the quiescent current and provide the load current during the negative half cycle.

In this circuit, two PNP transistors are necessary to accommodate the required power

CURRENT(M1) 0.8A-0.5A-0.2A--0.1A-12ms 15ms 18ms 21ms 24ms -0.2A -0.5A -0.8A CURRENT (Q2+Q3 9ms 12ms 15ms 18ms 21ms 24ms 1.2A-OUTPUT CURRENT 0.8A-0.4A-0.0A--0.4A--0.8A 15ms 18ms 21ms 24ms 120V 80V OUTPUT VOLTAGE 40V OV: -40V -801

Figure 6: Output stage behavior in Class AB mode circuit operation under full load conditions

15ms

in the prototype are 1N4148, but any equivalent small signal switching diode such as 1N914 is suitable. As the output current approaches approximately 1.2A, the voltage across R6 in series

-120V

with the Vbe of Q1, forces Q1 to limit the output current. Since the diodes D1 and D2 are conducting, a constant current through Q1 is established. In this example the maximum

18ms

21ms

24ms

27ms

output current delivered by the PA441 is set to approximately 40mA by Rcl.

The diodes D5 and D6 clamp the output of the PA441 to limit the VGS of M1 and still provide sufficient gate drive voltage to support the load current. When the current limit function is engaged, the output current of the PA441 flows through D1, D2, D5 and D6. The current limiting for the negative half cycle functions by forcing the output current from the PA441 through diodes D3 and D<sub>4</sub>, which establishes a constant

current of approximately 1.2A through Q2 and Q3.

This alternative topology does offer several advantages including a high output voltage

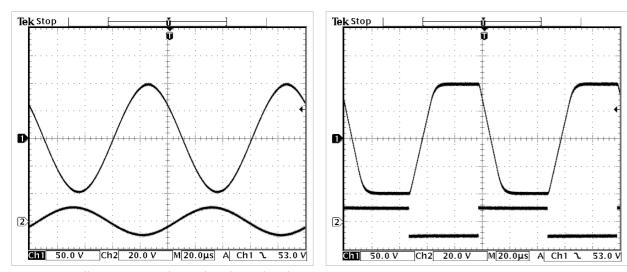

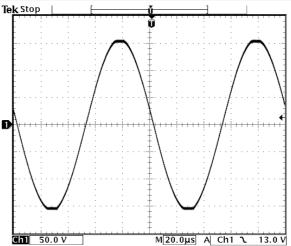

Figure 7: Oscilloscope screen shots taken during bench testing

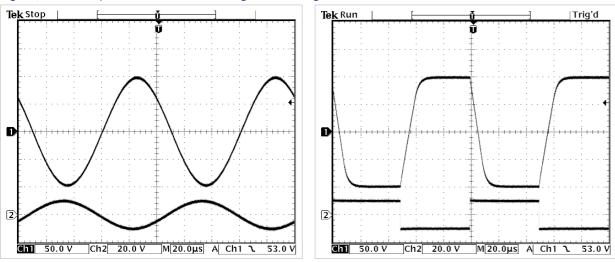

Figure 8: Oscilloscope screen shots taken during bench testing

swing resulting from a limited voltage drop as compared to the typical enhancement mode Class AB output stage; the simplicity of setting quiescent current; and a big plus, a reduced component count.

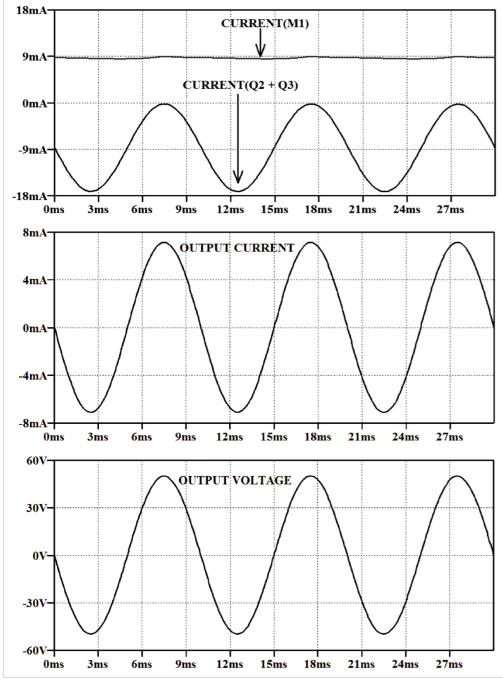

The best way to demonstrate and underscore just how robust this circuit can be is to look at it in simulation. Let's start by looking at **Figure 5**, which depicts actual simulation plots

that demonstrate the circuit is operating in Class A mode under light load conditions. The output voltage is 100V p-p across a load resistor of approximately  $7K\Omega$ , and quiescent current is measured at approximately 9mA. Since the current through the transistors M1, Q2 and Q3 is always greater than zero for the entire cycle, the output stage is proven to be clearly operating in Class A mode

Taking a look at **Figure 6**, we see it demonstrates the current behavior of the same circuit, but now in Class AB mode. Using full load conditions of  $100\Omega$ , this series of simulation plots illustrate how current is able to increase with this circuit and that the output stage behavior is in Class AB operation. In this scenario, the power supply voltage is  $\pm 160V$  and the output voltage is 200V p-p.

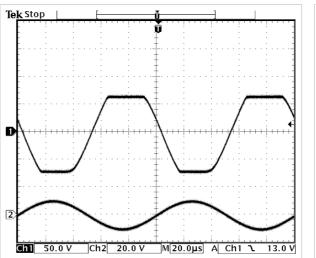

Figure 9: Oscilloscope screen shots taken during bench testing

The waveforms in Figure 7

gain of 10.

On the screen shots, the

"1" indicates

channel one,

which is

the output voltage, and

the number

voltage via

channel two.

illustrate that

"2" is the input

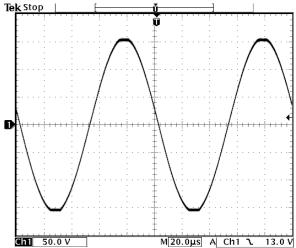

Figure 10: Oscilloscope screen shots taken during bench testing

At this point we should perform with a capacitive

some bench testing to see how well this circuit responds in some additional areas of key performance parameters.

Figures 7, 8, 9 and 10 are oscilloscope screen shots taken during a series of real-time test scenarios. The circuit is using a power supply voltage set at ±160V and a signal frequency set at 10KHz with the amplifier configured for an inverting

with a capacitive load of 0.123µF, the circuit is stable with virtually no distortion. Along the bottom of each screen shot, the voltage supply and slew rate are noted. In **Figure 8**, the circuit is shown now to be operating with a resistive load of  $100\Omega$  and again confirms circuit stability.

Figures 9 and 10 test the circuit's current limit levels and voltage swing clipping.

Without the enhancement of the AB current buffer, the PA441 would typically current limit just above 60mA, but **Figure 9** shows improvement to slightly above 1A. **Figure 10** illustrates the circuit's higher voltage swing clipping, now just above 150V. So the conclusion here is that the arrangement to pair the amplifier with the new buffer does create a circuit that can deliver performance that can scale up as the output current is increased.

In summary, the circuit we created for our example illustrates that by pairing an op amp with a current buffer, it is possible for the resulting composite amplifier to operate in Class AB mode. Granted, this is only a only a basic approach to achieving Class AB, but certainly this concept can be embellished and expanded to achieve even greater performance.

www.apexanalog.com

## Focused ion-beam circuit edit improves power device design

Benefits are especially significant at nanoscale geometries

By: Taqi Mohiuddin, EAG

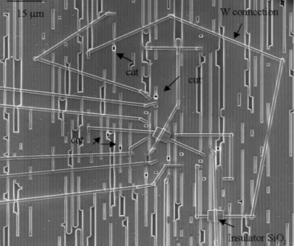

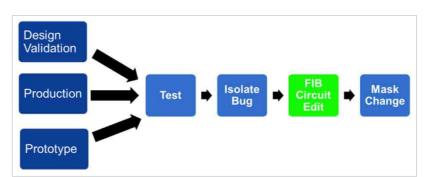

esigners of power control devices and those that combine control with power FET functionality are finding that FIB circuit edit techniques proven at older process nodes are delivering even greater benefits when used at advanced technology nodes. It is also expected that FIB circuit edit techniques will be important as many power devices move to silicon carbide (SiC), gallium nitride (GaN) and other wide bandgap materials. FIB circuit edit can help designers reduce costs while optimizing performance, increasing functionality, mitigating risk and accelerating development cycles.

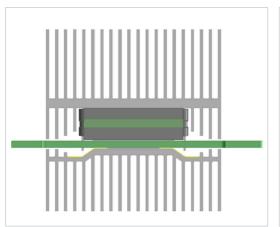

FIB systems used for circuit edit enable designers to cut traces or add metal connections inside a chip (see Figure 1). These edits can be made quickly and easily, at far lower cost than that required for a typical new wafer lot. Using the latest equipment, it is possible to edit circuits fabricated with 28 nanometer (nm) and smaller technology nodes, including devices that feature multiple-layer metal

stacks and those produced in flip chip and other advanced chip scale form factors.

The FIB tool is coupled to a CAD navigation system that enables it to locate each area where edits will be made. A finely focused

gallium (Ga+) ion beam with nanoscale resolution is used to image, etch and deposit materials on a device, with an extremely high level of precision. This enables designers to cut and connect circuitry within the live device, and to create probe points for electrical test. The high-energy Ga+ beam can mill through conductors, and uses various types of gases to either improve the precision of the milling process, or the ability to deposit conductive and dielectric materials.

There are numerous applications for FIB circuit edit at every

Figure 1: Front-side FIB circuit edit with multiple connections and cuts.

commercially available node.

The process can be used to verify design change on the tester, and to validate design change at the system board level.

Typical applications include:

- Debugging and optimizing devices in production

- Exploring and validating design changes

- Prototyping new devices without costly and timeconsuming mask set fabrication

- Scaling fixes, so that a fix can be duplicated on a handful or tens of devices that can be provided to internal test,

Figure 2: FIB circuit edit process flow. validation, and qualification teams and even to customers as samples

Accelerating time to market, and/or avoiding late delivery and associated penalties

The FIB circuit edit process can be implemented both at the simulation stage and later during de-bug to optimize success rates during the IC design process (see Figure 2).

Most current control products are fabricated using traditional silicon technology, and FIB circuit edit is performed in much the same way with these devices as it is with any other anlog or digital circuit. In the future, there is a strong possibility that drivers will move to wide bandgap materials. FIB circuit edit should offer benefits for these devices, as well. SiC, GaN and other wide bandgap semiconductor materials enable power semiconductor devices to withstand high voltages and temperatures, while providing higher frequency response, increased current density and faster switching speeds. At the same time, however, they present complex challenges related to design and characterization, process monitoring and reliability.

Challenges become even more difficult at advanced process nodes. It is harder to find and fix bugs, and mask costs are significantly higher. Testing becomes more tedious, simulations take longer, and in the case of many designs, it is impossible to achieve 100 percent verification. Additionally, there may not be perfect simulation models for extremely complex designs, and packaging can introduce stresses for sensitive devices. These challenges can be alleviated through the use of FIB circuit edit, which can be used to debug and validate fixes, and to explore design optimization changes before committing to a full mask spin.

#### **Tips and Techniques**

While some believe that FIB circuit edit only works well at 90nm and 65nm process nodes, this is inaccurate. Tool and methodology advances have enabled FIB circuit edit to be used for more precise beam guidance.

Today's systems also can operate in smaller areas, perform more intricate operations on both the back and front sides of the device, and handle copper layers.

Advances in operator skill have been particularly important.

The FIB circuit edit process is not completely automated; for example, endpoint detection continues to require a high level of skill in order to ensure when selected layers of interest have been successfully etched, especially at smaller geometries and during the most challenging FIB operations.

Also important is operator knowledge about IC circuitry and process technology, ion milling patterns, and the basics of FIB tool usage. This can be difficult to achieve within an in-house operation. Larger semiconductor companies will often augment inhouse circuit edit resources with external service labs. Small- and mid-sized companies generally can't afford a \$1 million FIB tool and wouldn't likely have the staff to operate it, so they tend to go directly to external labs, which can support basic electrical design characterization or verification of redesign parameters, and have a full range of debug tools for solving difficult logic failures and other development anomalies.

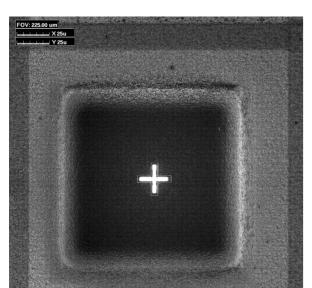

Key prerequisites for FIB circuit edit success – especially at advanced nodes -- include a minimum tool resolution (or

Figure 3: High-resolution trenching enables edits at advanced nodes. [Image courtesy of FIB International Inc.]

aspect ratio) of .1um, and a trenching approach that supports a finer resolution in order to make these edits. Today's equipment can create a hole as small as 0.1x0.1um with an aspect ratio of 1/20. In the case of most 20nm and 28nm designs, it is impossible to make a small enough hole to reach the target. The solution is specialized FIB techniques that shrink the aspect ratio in order to gain access to the target. This also requires the ability to smoothly remove dummy metal above the target metal layer (which, in turn, requires deep and extensive knowledge of IC circuitry and processes, FIB tools and ion milling patterns).

Another important capability is backside and frontside editing. Despite a misperception that flipchip FIB circuit edit can only be performed from the top of a

device, the reality is that backside edit is, indeed, possible -- and frequently the most effective approach. Backside edit may be required either because of the substrate material used in flipchip packaging, or because of the increased number of metal circuit layers

in today's ICs, which makes it harder to reach a lower layer when editing from the top. Figure 3 shows a typical back-side FIB circuit edit in which a probe pad is formed for micro probing.

A third area that should be considered is the ability to handle copper layers. Most 28nm and 20nm devices are copper devices that feature a crystal structure. The engineer must have experience in using special methods that ensure metal is removed smoothly with a very high level of quality. Also, accurate beam positioning is more challenging for copper metal devices due to the non-visibility of the circuit patterns. This is also important for aluminum metal devices if there are no unique patterns to recognize on the top level.

Beyond basic FIB circuit-edit

expertise it is also important that designers have access to companion failure analysis and test tools, expertise and capabilities. Most devices must ultimately be packaged, and there should be a smooth transition to de-capping or de-lidding the devices and performing microprobing and other de-bugging tests on FIB-edited parts.

Finally, designers should consider the expertise that is required in the area of front-end processes and materials. Semiconductor advanced technology nodes create challenges related not only to nano-scale geometries, but also new front-end materials. It can be extremely valuable when the FIB circuit edit function is part of a larger lab environment with significant front-end process understanding and materials expertise.

The design verification and validation of power devices will continue to grow more difficult as the industry moves to smaller nano-scale geometries and widebandgap materials. FIB circuit edit is becoming increasingly important for improving design success. Thanks to advances in tools, techniques and operator skill, FIB circuit edit can be used to explore design optimization opportunities, and to debug and validate fixes, without the cost or time required for a full mask

www.eag.com

#### AUTOMOTIVE

## Using the right power semiconductors can increase your power density

The solution must also address regulatory issues while serving system requirements

By: Jifeng Qin, International Rectifier

he steady increase in vehicle production, along with increased demand for car electrification is a worldwide phenomena. It is expected that global vehicle production will grow at around 4% over the rest of the decade. On the other hand, mainly driven by stringent fuel economy requirement and crossfunctional new features, the power semiconductor usage actually grows at

two-digit rate. The dilemma soon rises up between the increased power requirement and limited space in the automotive system. There are fundamental physical limits to how much energy that can be extracted from a given volume/mass of the energy resources (so called "power density"), and this is the key area that many car manufactures are working on nowadays to improve the performance.

Automotive DirectFET®2: The Optimum Package **Maximizes Power density Minimizes Conduction Losses** passivated die • Provides Lowest Thermal Resistance Lowest Package Resistance copper 'drain' die attach Enable Dual Side Cooling - Efficiently removes heat away from PCB · Major loss reduction in MOSFET with Minimizes PCB conduction Losses Reduces Parasitic Ringing · Lowest Package Inductance source Reduces EMI manufacturing processes copper track on board Improves Switching Speed · Easy to design, easy to parallel IOR Lowest profile, small footprint **Environmentally Friendly** MOSFET • 100% Lead free • 100% RoHS Complian otive Level Reliability No wirebond, no leadframe, no mold **RoHS** • All DirectFET2 are specifically optimized for automotive applications and pass AEC-Q101

Figure 1: Key Benefits of Automotive DirectFET2

Power density is indeed an important phrase in automotive electronics industry. For example, the high power density battery technology is critically needed to ensure the hybrid and electrical car development because nowadays the power density of battery still has significant gap versus gasoline. Similarly, take the steering system as another example, the hydraulic driven steering system always offer

good power density compared with an electrical driven motor system, which means replacing the traditional solutions with electric drives requires advance system design with highly efficiency and compact power electronics, especially discrete semiconductor component.

Silicon technology is pretty matured nowadays, and semiconductor industry relies on

WWW.POWERSYSTEMSDESIGN.COM WWW.POWERSYSTEMSDESIGN.COM

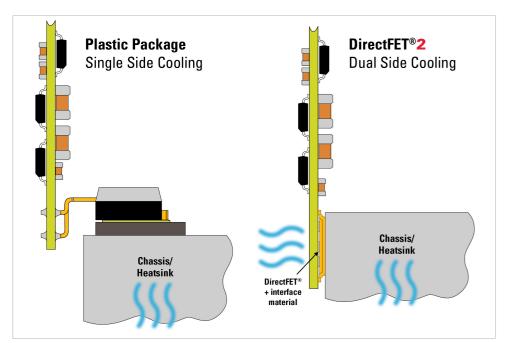

Figure 2: Dual Side Cooling of DirectFET2 significantly improves the power density

two main areas to improve the system power density - either through the innovation of the new material technology, or through the innovative power packaging such as IR's DirectFET2 performance power package. Figure 1 summarizes the key benefits of the DirectFET2 performance power package. DirectFET2 utilize the Copper Can on top to directly conduct the high current - therefore no wire bonding, no leadframe, and even no mold compound is required. This structure makes the package easy compliance with automotive standard, and all DirectFET2 products are specifically optimized for automotive applications and pass the stringent AEC-Q101 automotive reliability standard. On the other hand, low package inductance reduces parasitic ringing and therefore improves

the EMI performance, and low package resistance minimizes conduction loss.

Another important feature for DirectFET2 lies in its superior the dual-side cooling concept. For traditional plastic surface mount package such as DPAK the wire bonding, however thermal resistance therefore prevent the topside cooling,

cooling is always limited by the PCB thermal impedance. Figure 2 shows the

thermal performance by utilizing and D2PAK, package molding is always needed to accommodate molding compound have huge furthermore the bottom side

newer technology arrives at an ever increasing rate, consumers are discarding their obsolete products quickly. Motivated by addressing the global issue of consumer electronics waste.

|                 | RoHS 5/6 | RoHS 6/6 |

|-----------------|----------|----------|

| Pb free package | V        | <b>V</b> |

| Pb free solder  | exempt   | √ ·      |

comparison Table 1: RoHS 5/6 vs RoHS 6/6 Comparison

of the cooling methodology between plastic package and DirectFET2. For plastic package, cooling through the PCB becomes impractical for many high power applications; therefore complicated and costly mechanical assembly is needed to achieve the good single bottom side cooling. On the contrary, DirectFET2

could take advantage of dual side cooling both from bottom PCB and from top heat sink, the flexibility of topside cooling significantly simplifies the mechanical design, reduces the system cost and improves the system overall power density.

The semiconductor industry is in fast changing mode, as

Figure 3: First DirectFET2 package with COOLiRFET™ benchmark silicon platform

The Restriction of Hazardous Substances Directive 2002/95/ EC (RoHS) standard was adopted in 2003 by the European Union. Nowadays RoHS has become the benchmark compliance standard for removal of hazardous materials from electronic components. RoHS compliance refers to an EU law to limit the concentration of these substances:

- Cadmium (Cd)

- Hexavalent chromium (Cr [VI])

- Lead (Pb)

- Mercury (Hg)

- Polybrominated biphenyls (PBB)

- Polybrominated diphenyl ethers (PBDE)

As shown above - one of the six banned substances is lead. RoHS 5/6 and RoHS 6/6 are abbreviations commonly used in the industry to designate components or products that comply with the RoHS Directive. RoHS 5/6 refers to products contain lead used in an exempt application, and RoHS 6/6 refers

to products below the applicable RoHS Directive limits for all six substances without relying on any exemptions (see Table 1 below). Many power devices are still allowed to use lead internally, the solder die attached material offers excellent thermal conductivity, very low electric resistance, and high-melting temperature which allows the solder inside the package not to melt when the pacakge is reflowed on the PCB. This exemption is set to expire in 2016 requiring the redesign of systems using non-compliant devices. The new RoHS 6/6 standard requires 100% lead free, even for the internal die attached material.

DirectFET2 is already RoHS 6/6 compliant - It uses epoxy for die attach material - the epoxy is optimized for thermal and electrical conductivity, the performance is comparable to solder yet contain no lead, therefore DirectFET2 package is a completely lead-free power package that meets all

present and future RoHS regulations.

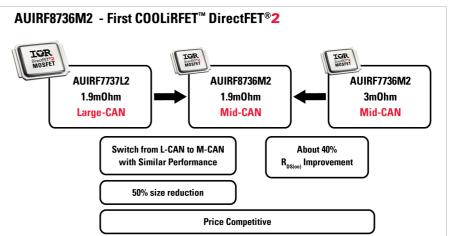

For semiconductor discrete components, package innovation always need to in line with benchmark silicon platform to ensure the excellent component level performance.

IR's 40V automotive grade COOLiRFET™

MOSFET platform finds itself a perfect fit for these 12V battery heavy load applications. By utilizing the most advanced trench technology, COOLiRFET platform sets the new industry's benchmark Rds (on) performance, and by combining automotive DirecFET2 performance power package with benchmark COOLiRFET silicon technology, system designers can benefits from significant power density improvement and 100% RoHS compliance.

Figure 3 shows the key benefits of the first COOLiRFET DirectFET2 part. By leveraging IR's benchmark COOLiRFET™ silicon technology with the power performance DirectFET2 package, AUIRF8736M2 brings a 40% Rds(on) improvement in the same footprint or equivalent performance to Large Can device in 50% smaller package reducing overall system size and cost for automotive applications.

www.irf.com

## How smart is the Smart Grid when the computer crashes?

#### Over-reliance on a central computer is an invitation for disaster

#### By: Edward Herbert, PSMA Energy Efficiency Committee

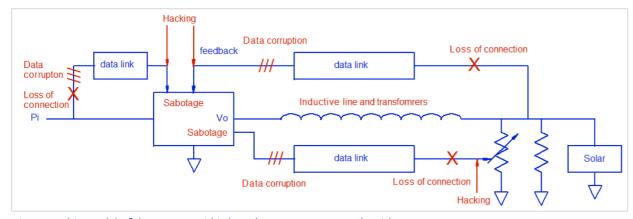

oftware security in the grid is becoming increasingly important. There have been reports of appliances hacked to send SPAM, and The Wall Street Journal claims that the Smart Grid already has been penetrated and infected with potentially disruptive software programs. There are even fears that terrorists may penetrate the SCADA systems in utilities and wreck a generator as revenge for "Stuxnet.". Homeland Security surely is giving this attention.

My concern, however, is more mundane: what happens when the computer crashes? What should happen is "nothing," or at

least nothing that does damage or that cannot be managed expediently.

An infrastructure using central computers with multiple sensors overlaying the Grid is a very powerful tool, with great potential for improving Grid performance and reliability. Using real-time measurement, such systems can pinpoint where repair is needed during a crisis, as well as predict problems. Computer-based management systems allow for unprecedented modeling and calibration. For example, the advantages of automated meter reading for billing are well recognized. However, overreliance on a central computer is

an invitation for disaster. A Grid that requires a central computer and communications for stable operation very likely will become unstable when the computer crashes.

#### Command & control

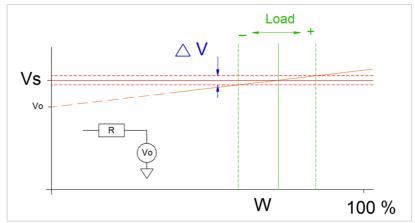

One of the justifications for the Smart Grid is that we can avoid building more power plants if we can send out commands to reduce the load in times of stress. What happens if you cannot implement those commands? Times of stress are when a central computer is most vulnerable, most likely to be unusable (see **Figure**1). Power supply designers understand the need for stability

Figure 1: This model of the Smart Grid is based upon a power supply with remote sense. There are many vulnerable points.

Figure 2: Local control that varies the load in response to line voltage, as an example, is fast and does not rely on a central computer. Other parameters that can be used are frequency and phase angle.

analyses. Loop stability is dependent on response, and lags are a problem. Has the Smart Grid been analyzed to account for lags? What about the time needed to collect and analyze Mega-data, and output the commands to the control devices? A denial-of-service attack could slow the response to a crawl. The lag will make it impossible to respond quickly. Taken together, the inevitability of computer crashes and the slow response make it imperative that local systems have robust default modes and fast response to rapidly changing line conditions. Local controls need to be there. If well done, they mitigate the need for centralized computer control (see Figure 2).

#### The threat of hacking

The conversation needs to include hacking, as it is a sub-set of computer failure. Anything that connects to the Internet has the potential of being hacked. The most effective hack renders

the equipment inoperable and non-repairable. Unfortunately, this is much easier than most people realize, partly because of the features that are built in for tight security. Consider a malicious command that turns an appliance off, followed by a firmware update that makes it non-responsive to any command or override. Or a hack that changes the encryption key, so that the appliance responds only to the hacker, or to no one at all.

Contrary to popular perception, the greatest threat of hacking is not the foreign terrorist but disgruntled employees. Regardless of security and encryption, most commands originate with a person or an algorithm. The bookkeeper that notes that a customer is delinquent disconnects him with a click of a mouse, and security won't stop her. She probably cannot update the firmware or change the encryption keys, but if you substitute the consultant

#### How stable is your power supply?

Easily determine stability using the **Vector Network Analyzer Bode 100** in combination with the Wideband-Injection Transformer B-WIT 100.

Measure loop gain, plant transfer function, phase margin and gain margin from 1 Hz to 40 MHz.

For more information and free application notes please visit: www.omicron-lab.com/psd

SERVING THE POWER GRID

who is hired to upgrade the anti-virus software, he could. He can plant a logic bomb that simultaneously shuts off thousands of customers after he has moved on. Thousands of Smart Meters, shutoff, with corrupted encryption keys, is scary.

The best defense against hacking is having it not do much, the same as the preferred response to computer crashes. If hacking did not do much, it would be no fun and the hackers would stop trying.

So, what can commands from a central computer do that is safe? Often, the concern is "data security," whether a burglar could tell who isn't home by motoring appliance use. While important, that will not threaten the stability of the Grid. So, monitoring and collecting data are OK. But why does a refrigerator need the computer power to send emails? Part of the answer may be limiting function to what really is needed.

#### Market issues

Much of power management is arbitrage. Arbitrage cannot be managed by detecting line conditions, so it needs to be authorized and commanded from a central authority. However, arbitrage does not require abrupt changes. One way to limit the ability to do damage is to apply power changes due to arbitrage at a very slow rate, slow enough

so that errors will be detected and corrected before damage is done.

One function that the utilities would never give up is the ability to shut off the power to delinquent customers.

There is no urgency. If shut-off commands were sent but could only decrease the power by 4 % per hour, constrained by hardware, it would take a day to be turned off entirely. That's OK. Mistakes could be caught and corrected, and the customer might even pay his bill.

What if the encryption keys were hacked? The default mode should be "On." Absent commands that maintained the off-state, the Smart Meter should ramp up 4% per hour.

How about power control during heat waves? The same mechanism can apply. The default power allowed by the Smart Meter should be a reduced level, a baseline power that would not overload the system even in times of high demand. Buying more power above the default level is arbitrage, and would require command and response to enable and sustain it. 99.9% of the time, this would be fully functional. When the computer crashes, everyone has enough power to get by and the total load is low enough not to overload the Grid.

Note that in the above scenarios,

the Smart Meter is not relaying commands to control specific appliances. It is just enabling a percentage of baseline power, lower or higher. It is up to the customer to turn-off some appliances or buy more power on the spot market when necessary. The sophisticated customer may have a load management computer tied to his smart phone. Others may just unplug what is not needed. The computational power and software needed by the utilities is much less, therefore much less expensive.

Little mention is made of liability, but once it is considered, the utilities may realize that the risk of having explicit control of specific appliances may be unacceptable. What is the liability if a freezer is turned off, but cannot be turned on? Times 10,000?

There was a surge in Smart Meter deployment with large grants, but now the Smart Meter manufacturers are trouble as sales lag. Security concerns may be a significant factor. Utilities may be realizing that getting it wrong could be very expensive.

This article reflects the opinion of the author, not necessarily that of the PSMA

## Optimizing Smart Grid Power Connection Functionality

The best solutions combine strong DC current capability with accurate timing functions

By: Chris Siegl and Aung Tu, Fairchild Semiconductor

dvances in system level goals of the Smart Grid to better manage electrical loads during high demand time of use or during a shortage of available resources have created a need for efficient methods of connecting and disconnecting loads from the grid. Load management systems have been available in the commercial and industrial arena for some time. However, with the Smart Grid management systems now advancing on to the stage of controlling devices within the residential and commercial applications, the reliability, efficiency, and cost-effectiveness of such devices become more critical.

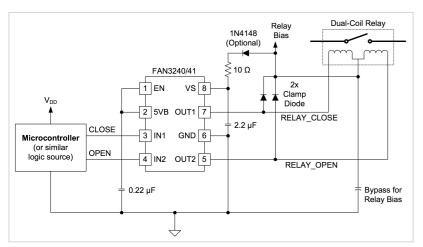

The connect/disconnect solutions must be tolerant of the noisy environment of the smart meter as it is directly connected to the incoming feed from the grid and controlled by a micro-controller. The best solutions combine strong DC current capability to open even welded shut contacts with accurate timing functions to filter out noise, relay protection, and the compatibility to optimize the micro-controller clock cycles.

This article reviews both the implementations currently in use and those in development.

Smart Grid system load management proposals, as well as switches needed in various emerging countries are also reviewed. Mechanical dual-coil relays are examined to define optimized driver circuits that provide the needed functionality.

The article concludes with a discussion of the power systems needed to drive the connection relay, as well as the driver trade-offs to meet the proposed performance specifications.

#### The Impact of Smart Grid

The Smart Grid initiatives have spawned new approaches in load management. The basic technology of remote controller and sequencing of loads in its basic forms has been a function of the industrial market for a long time with complex incentives for businesses to participate. Initially this was done largely through individual device wire telephone connections back to the utility as well as warning and request systems through a mechanism

of telephone communications devices.

The cost of this has dropped dramatically with the introduction of wireless and Power Line Carrier (PLC) communication technologies and a healthy competition resulting in improved performance at constantly diminishing costs. Not being dependent on direct hardwire installation and intrinsic safety in the wireless implementations dramatically reduces the cost and complexity of the installation process.

#### The Residential Meter Market

Another inducement for an economical connect/disconnect requirement comes from the residential meter market. Enabled by the improvements in timely communications to individual meters and local control functions, the ability to remotely open a meter load greatly reduces service costs for a simple service stop or service restoration. There is no longer a need for a service truck when customers request service interruption and re-connects, such as for seasonally occupied vacation and rental properties.

Figure 1: Simplified Diagram of a Relay Drive

Service personal interaction over non-bill payment issues is also minimized. Similar savings apply to temporary construction sites and other venues not needing continuous usage. This remote management capability also reduces power theft in these unoccupied sites and mitigates the associated power losses.

#### Mitigating meter socket failures

There have been concerns over recent instances of fires starting around newly installed smart meters in older meter sockets. When replacing older meters that have been in place for a long time, the issue has been traced to heating in the meter socket due to corrosion in the contacts to the meter. Heat buildup in the socket is a function of load current and level of corrosion, primarily caused by weather damage and water seepage. Disconnecting the load and reporting the over-temperature condition puts the meter in a position to mitigate the damage safely.

#### Disconnect after power is lost

Gaining in importance in contactors is the ability to disconnect and re-connect after power has been lost. This is especially important when controlling devices such as compressors, which have high start-up surge currents and are best not cycled without a minimum off time (compressors overheat if cycled over short intervals). Power restoration surges can be reduced by delayed turn on and sequencing of loads, thereby reducing peak surge currents and stresses on delivery equipment as well as loads.

Meter-based and load-based contactors can provide this function with capacitor stored holdup power which is sufficient to pulse the contactor open even in the powerloss event. Smart Grid research is showing significant advantages in equipment reliability and stability using these types of policies.

#### The Industrial Market

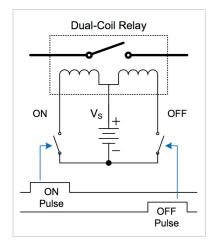

In the industrial market the contactor function has been implemented with a variety of approaches. Motors have been used to drive contactors but these suffer from slow speed during the opening operation with resulting arcing damage. For larger systems, various forms of arc suppression are often used including compressed gasses and spring assisted fast-switching mechanical implementations. These are not economical for the higher volume cost sensitive markets. Therefore the emerging consensus is to use a polarized bistable latching relay utilizing two coils with one coil pulsed to move the relay from the closed position to the open position and the second coil to move the relay from the open position to the closed position.

#### Detailed look at the Driver Configurations

The bi-stable, two coil latching relay is the most common configuration. Some versions include built in springs and other mechanical assistance in the open direction for lower-power operation.

The typical load connection function is implemented with a bistable contactor device with two or more poles to disconnect. The contactor is usually wound with two windings; one to close the contactor and the other to open the contactor. A permanent magnetic material or a mechanical latch is used to hold the contactor in place when it is not switching.

To facilitate the mechanical movement, the relay coils need to be energized for a specific time interval. Once the contact(s) have changed position, the voltage should be removed from the winding of the relay. A simplified, typical circuit diagram is shown in **Figure 1** with example waveforms.

#### **Relay Drive Circuit Requirements**

As the diagram shows, a dual-coil relay is connected to its supply rail at the center point of the two relay windings. Each winding can be energized by the switches connected

Figure 2: a block diagram of a typical metering system

to the relay coils. The two switches must not be on at the same time, which would cause excessive currents to be drawn from the supply rail, and result in improper operation and damage to the relay.

To accommodate the relatively long time required for the relay contact to travel between its stationary positions (ON and OFF positions), the pulse must be longer than the minimum duration specified in the relay specification. It is also desirable to limit the maximum length of the drive pulse to prevent potential saturation of the relay winding and to avoid over heating the coils and drive electronics. The control signals should also be compatible with latest generation of microcontrollers supporting both CMOS and TTL input levels.

The relay specification also defines the minimum and maximum oper-

ating voltages for reliable operation of the contact(s). The voltage requirements of the contactor vary by application, which is driven by tradeoffs in meter requirements. Lower voltages are common in lower-cost low-power applications where the meter and the relay sizes are smaller. Higher voltages are common where higher currents are needed where the larger contacts require more power to switch. Therefore the drive circuit should monitor the relay bias voltage for sufficient voltage level. It is also desirable to have an under voltage lockout for the drive circuit to facilitate smooth startup while circuits initialize.

The preferred integrated solution provides input signal qualification for the control signals, protection against simultaneous activation of the two relay coils, a maximum drive pulse duration limit, and

additional basic functions such as bias voltage monitoring, driver enable input, and thermal protection for the driver. The ideal circuit minimizes component count and board space, while increasing the reliability of the system and the noise immunity of the circuitry when driving the coils of the relay.

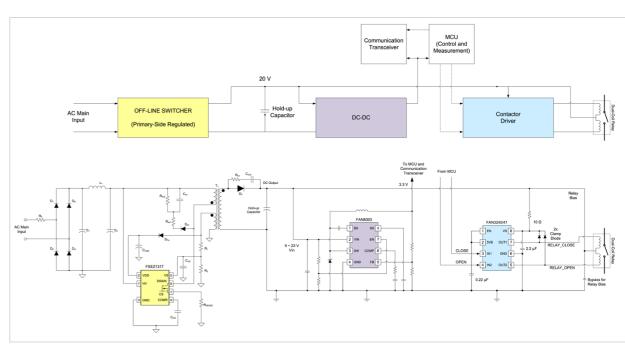

#### Practical implementation of power and connect/disconnect

Figure 2 shows a block diagram of a typical metering system. The relay drive voltage is a function of the particular relay used. In general, larger current switching relays (larger contacts) require higher voltages to deliver enough energy to switch fast enough to minimize contact loss due to arching during the switching. Usually this high voltage source is provided by a capacitor to provide maximum power during switching especially in applications where

Figure 3: A relay driver such as the FAN3240 or the FAN3241 with a built-in bias supply can be very beneficial

switching occurs after power is

The capacitor has to be sized to provide the energy needed to switch successfully. The capacitor charging supply can be current limited, reducing the power supply cost by taking time to bring the switching voltage to full charge. The disconnect switching is an infrequent event in meters. The typical devices being switched, such as compressors, have a minimum required off time for long life operation. Longer recharge times reduce power supply cost and stresses without impacting performance.

Communications, control and measurement functions are typically implemented with lowvoltage (3 to 5 volts) circuits such as micro-controllers and communications circuits. There are a variety of communications technologies that focus on particular market requirements and geographic constraints. Most of these

have a burst profile where power consumption is on the order of 5-watt transmission for 100 milliseconds followed by a delay of one second or more before the next transmission. Transmission after power is lost (reporting the status of the network at the time of power loss) is also desirable for times of up to 10 minutes for last transmissions.

The holdup capacitor as described above for the disconnect function applies as well to the communications circuit if a DC-DC stage is included for efficient low-voltage conversion from the high-voltage capacitor. The holdup capacitor can now be shared by the transmission and disconnect functions if sized appropriately.

For a current-limited, off-line switcher supply, a primary side regulated flyback controller with an integrated MOSFET such as the FSEZ1317WA makes for a feature-rich economical solution. The DC-DC block can be implemented with the minimal-partscount high-performance solution such as the FAN8303, a stepdown regulator with an integrated switch. Finally, the connect/disconnect drive designed to meet the requirements as defined in this article can easily be implemented with the recently introduced FAN3240 and FAN3241 smart dual-coil relay drivers.

#### When Isolation is required

Sometimes isolation is required in cases such as when there is wire-line communications or where there are a number of circuits on different phases controlled from a common point. A relay driver such as the FAN3240 or the FAN3241 with a built-in bias supply can be very beneficial in reducing parts count and cost as well as circuit simplifications as shown in Figure 3.

#### Conclusion

Variations on the presented solutions can be applied to other smart meter power requirements as well as distributed connect/disconnect functions in a variety of specific applications. As the Smart Grid functionality continues to expand in complexity, new opportunities will emerge for new power management functions. Fairchild Semiconductor has tools, application notes and application pages accessible through the Fairchildsemi.com web page to help you in your design process.

www.fairchildsemi.com

#### POWER SUPPLIES

#### Advanced packaging critical to power system performance

The last decades have witnessed aggressive advances in semiconductor miniaturization

By: Doug Ping, Vicor

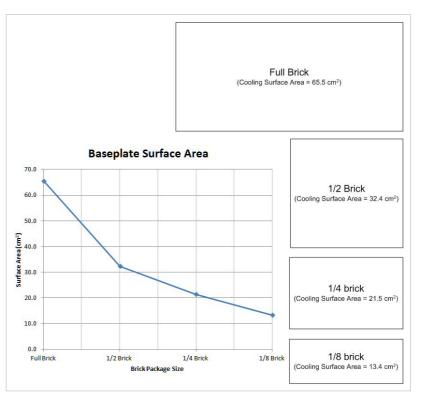

ackaging for power electronics has evolved from simple metal bending to advanced materials and thermo-mechanical design, and from freestanding supply to integrated power management. System-size reductions made possible by higher switching frequencies and semiconductor

miniaturization drove the early part of this trend. The more recent improvements, however, have also depended on advances in thermo-mechanical design, particularly of power management components.

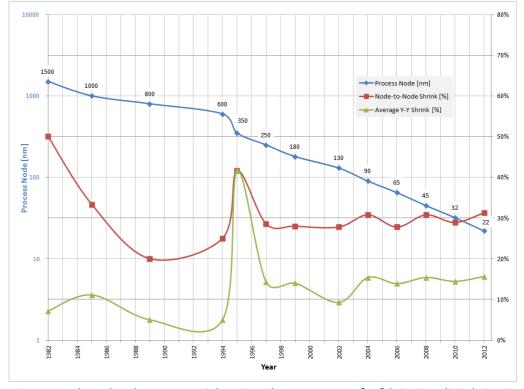

#### Beyond the Box The last decades have witnessed aggressive advances in semiconductor miniaturization. During the 30 years from 1982 to 2012, com-

mercial processes for fabricating CMOS logic shrank from the 1.5 µm node to the 22 nm node (see Figure 1). The resulting increase in functional-density—more than 4,600:1—has altered the course of electronic product design, not just within computational cores or memory subsystems, but throughout the product as well.

At the start of this interval, typical electronic products provided low functional density and presented modest power demands, so power supply designs made use of discrete components and less than optimal cooling methods. Although supply efficiencies were poor by today's standards, they were sufficient given their prod-

Figure 1: In three decades, commercial semiconductor processes for fabricating digital circuits have moved from the 1.5 µm node to the 22 nm node, shown here on a logarithmic scale (left).

WWW.POWERSYSTEMSDESIGN.COM WWW.POWERSYSTEMSDESIGN.COM