Author:

Arne Martin Holberg, AVR Project Manager & Andreas Eieland, Product Marketing Manager, Atmel

Date

02/03/2012

Although power consumption is the product of operating voltage (Vcc) multiplied by the current consumption (Icc), current consumption is usually the only parameter considered when describing the power characteristics of a chip. This is a mistake, because decreasing the operating voltage directly reduces the current consumption and the overall power drain. Current consumption increases directly with the system clock frequency so keeping the system clock as low as possible is critical to keeping power consumption down. At the same time it is important to run the application as fast as possible to reduce the time in active mode so that the device can return to the power saving sleep modes rapidly and stay there as long as possible. The clock frequency is affected by a number of factors that include the microcontroller's surroundings and peripheral set as well as the architecture and the instruction set. Active versus Sleep In many applications, the processor does not run continuously and peripherals may be idle much of the time. The overall power consumption can be lowered by taking advantage of various "sleep" modes available on virtually all processors. The most common sleep modes are Power Down", Power Save and Idle. In Power Down mode everything is shut down, including the clock source and the real time counter. In Power Save mode everything is turned off except a 32 kHz clock running from a crystal to keep track of time. The contents of volatile memory is kept in both Power Down and Power Save mode, this removes the need to re-initialize peripherals when the device wakes up and ensures a shorter wake-up time for the application. Idle mode is a shallow sleep mode where only parts of the device are shut down but the main parts of the microcontroller are running. The advantage of having multiple sleep modes is the flexibility it provides to shut down any part of the microcontroller that is not absolutely necessary to the function at hand. For example with a 1.8V supply voltage operating at 1 MHz and 25°C, Atmel's ATmega328P AVR controller consumes 300 μA in Active mode, 40 μA in Idle mode, 0.70 μA in Power Save mode and a scant 100 nA in Power Down mode. Since a microcontroller can spend substantial amounts of time inactive, it is important to consider power consumption in sleep modes as well as active power consumption.

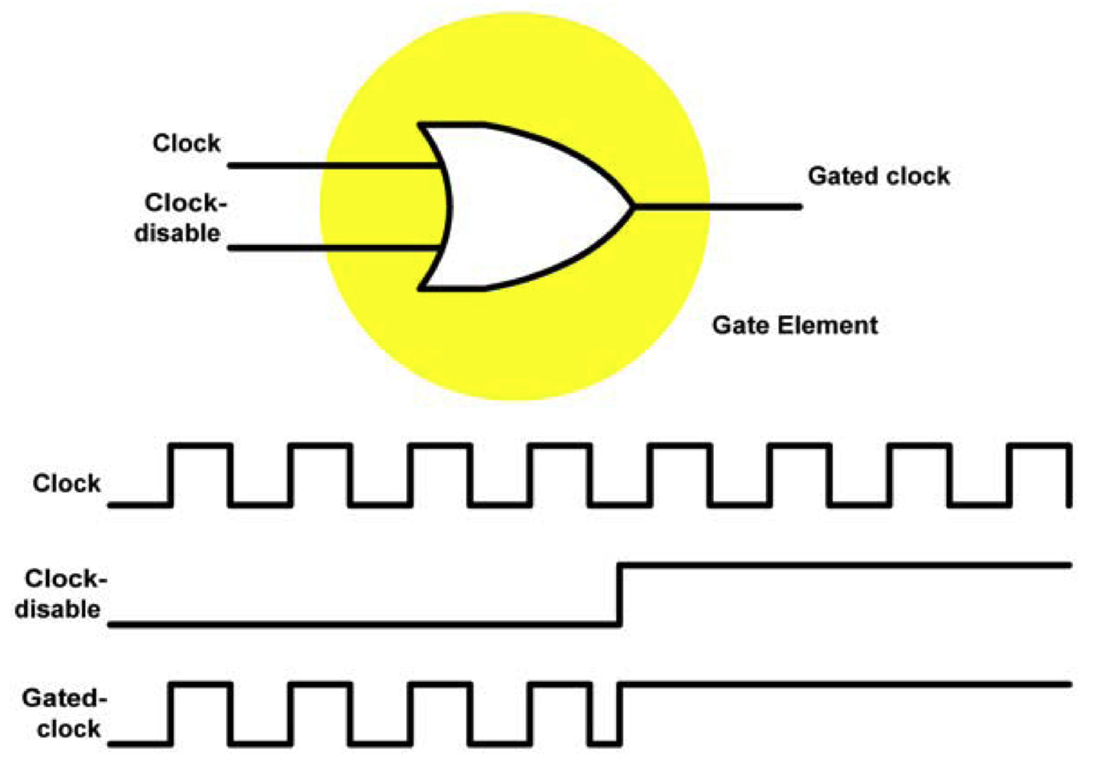

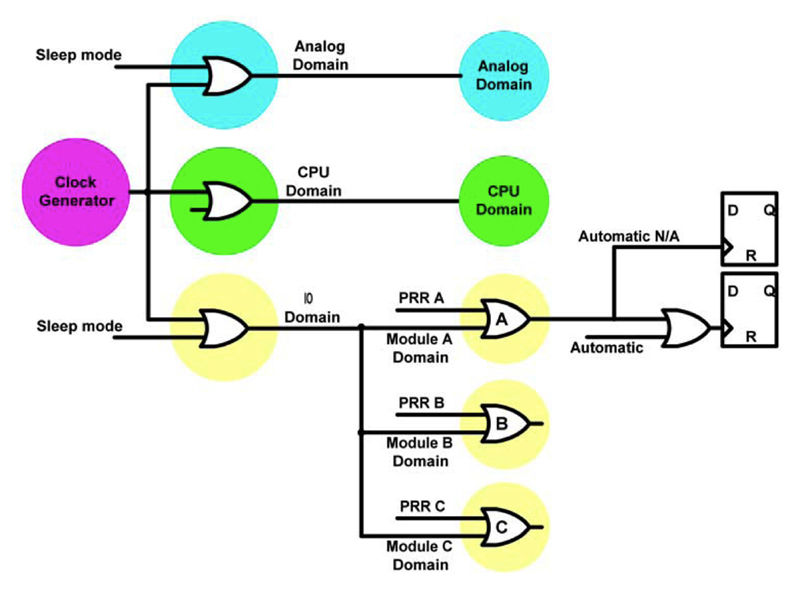

How to Lower Power Consumption in Sleep Mode Modern microcontrollers are built on digital CMOS logic that is, in theory, only consuming power when the logical or clock signals toggle. A signal is toggled when it has a transition from "0" to "1" or vice versa. Based on this theory, sleep current consumption should be equal to zero since no clocks and no transistors are active. Although sleep mode power consumption approaches zero, current leakage and peripherals that remain active can consume quite a bit of power. Leakage Current The temperature, the supply voltage, and the process technology affect the leakage current. Some microcontroller manufacturers use proprietary processes that can provide sleep currents down to 100 nA and the ability to operate at a true 1.8V supply voltage. Active Peripherals The biggest contributors to sleep mode power consumption are active peripherals. Enabling internal analog or digital modules can cause a significant increase in the overall current consumption but can be difficult to evaluate. While well-documented microcontrollers describe this additional current consumption in their datasheet, others claim that this current consumption equals zero. The power consumption in digital logic is mainly due to the toggling frequency, the capacitive load, and the supply voltage. The power consumption in analog modules is, on the other hand, static. There is often a trade-off between power consumption and robustness, accuracy, speed and fast start-up time in analog modules. The single-most important analog module in terms of power consumption during a sleep mode is the brown-out detector (BOD). A BOD protects the microcontroller when the supply voltage falls below its operating threshold by resetting the device. Since the BOD must be functional when the controller wakes up, making a zero-power BOD may seem like the most attractive option. The solution to this problem is to have the microcontroller shut down the BOD when it enters sleep mode and start it again just before leaving sleep mode. This approach ensures the BOD is functioning when it is needed without any current penalty while in sleep mode. Very Low-power Oscillators versus 32 kHz Oscillators In many applications, the time spent in active mode is insignificant compared to the time spent in Power Save mode with everything turned off except a real-time clock and the brown-out detector. In these applications, the power consumed in Power Save mode is the most significant contributor to overall power consumption. Therefore, lowering the current consumption of the 32 kHz oscillator can significantly reduce overall system power consumption. Designers should be very thorough in evaluating the current consumed with the crystal oscillator running. There are, in general, two ways of timed wake from deep sleep: either by a RTC or by very low power oscillators (VLO). The difference between them is mainly the accuracy. The RTC allows proper timing due to the very accurate 32 kHz oscillator while a VLO is very inaccurate and not suited for time-critical functions. The Active mode power consumption for a given device is the sum of all toggeling gates. This gives that Active mode current consumption can be reduced by minimizing both the number of gates and the number of times each gate needs to toggle in order to run the application. Clock gating is used to reduce the amount of toggling gates. A clock signal can be stopped using a gating element. Any clock distribution or clock domain that is gated is frozen, have no toggling, and will not have any dynamic power consumption The principle of clock gating is depicted in Figure 2.

The first level of clock gating is the sleep modes. The sleep modes gate the clock distribution to a group of functionality thereby enabling different levels of sleep and functionality. The response time for wake-up from sleep mode is only six clock cycles when the internal RC oscillator or an external clock is selected as the clock source. Power consumption during the wake-up session is less than in Idle mode. This means that the AVR microcontroller can wakeup from sleep mode and re-enter the sleep mode again with extremely-low energy consumption and spend a very short time during wakeup and active mode. The second level of clock gating is the Power Reduction Register (PRR). Many peripheral modules are only used for a short period of time or not at all. The Power Reduction Register contains control bits for disabling unused peripheral modules. The entire clock distribution to disabled peripheral modules is gated. This is more powerful than just disabling the module by its enable bit since the modules IO registers are disabled by the PRR. By disabling one peripheral module results in a reduction of 5 to 10% of the total power consumption in active mode and 10 to 20% of the total power consumption in idle-mode. www.atmel.com