Empowering Global Innovation

March/April 2010

#### Special Report - Digital Power

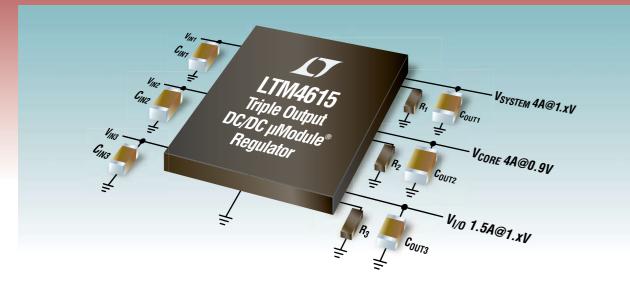

# Multiple Output µModule Regulators

### **Replaces More Than 30 Components**

Our new step-down DC/DC µModule regulator family regulates multiple output voltages and operates from common or independent input supplies. Housed in compact LGA packages with integrated inductors, control circuitry, bypass capacitors and power MOSFETs, these µModule regulators reduce bill-of-materials, insertion costs, board space and design time. Simplify your design for powering the latest generation FPGAs, ASICs, DSPs and microcontrollers.

#### V Multiple Output Step-Down DC/DC µModule Regulator Family

| Low Voltage: ≤5.5V <sub>IN</sub>   |                                  |                      |                                                     |                                            |                                            |  |  |

|------------------------------------|----------------------------------|----------------------|-----------------------------------------------------|--------------------------------------------|--------------------------------------------|--|--|

| Triple                             | Output Current<br>Configurations |                      | V <sub>IN</sub> Range                               | V <sub>OUT</sub> Range                     | LGA (Land Grid Array)<br>Package Size (mm) |  |  |

|                                    | → 4A                             | → 8A                 | $V_{\rm IN1}\!\!:\!2.375V$ to $5.5V$                | V <sub>OUT1</sub> : 0.8V to 5V             |                                            |  |  |

| LTM <sup>®</sup> 4615              | <b>→</b> 4A                      |                      | $V_{\rm IN2}\!\!:\!2.375V$ to $5.5V$                | V <sub>OUT2</sub> : 0.8V to 5V             |                                            |  |  |

|                                    | <b>→</b> 1.5A                    | → 1.5A               | $V_{\text{IN3}}$ : 1.14V to 3.5V                    | V <sub>OUT3</sub> : 0.4V to 2.6V           |                                            |  |  |

| Dual                               |                                  |                      |                                                     |                                            |                                            |  |  |

|                                    | → 4A                             | <b>→</b> 8A          | $V_{\rm IN1}\!\!:\!2.375V$ to $5.5V$                | V <sub>OUT1</sub> : 0.8V to 5V             | Ø                                          |  |  |

| LTM4614                            | → 4A                             | Also see<br>LTM4608A | V <sub>IN2</sub> : 2.375V to 5.5V                   | V <sub>OUT2</sub> : 0.8V to 5V             | Repetator                                  |  |  |

| LTM4616                            | → 8A                             |                      | $V_{\rm IN1}\!\!:\!2.7V$ to $5.5V$                  | $V_{0UT1}$ : 0.6V to 5V                    | 15 x 15 x 2.8                              |  |  |

| 211114010                          | → 8A                             |                      | $V_{\text{IN2}}\!\!:\!2.7\text{V}$ to $5.5\text{V}$ | $V_{\mbox{\scriptsize OUT2}}$ : 0.6V to 5V |                                            |  |  |

| High Voltage: ≤26.5V <sub>IN</sub> |                                  |                      |                                                     |                                            |                                            |  |  |

| LTM4619                            | → 4A                             | <b>→</b> 8A          | $V_{\rm IN1}\!\!:4.5V$ to 26.5V                     | V <sub>OUT1</sub> : 0.8V to 5V             |                                            |  |  |

| 21114013                           | → 4A                             | Also see<br>LTM4601A | V <sub>IN2</sub> : 4.5V to 26.5V                    | V <sub>OUT2</sub> : 0.8V to 5V             |                                            |  |  |

#### V Info & Free Samples

www.linear.com/micromodule 1-800-4-LINEAR

D, LTC, LT, LTM and µModule are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owner

## בינים באנים באורים באלווים באלווים באלים באלי

Viewpoint The Digital Power Marriage, By Cliff Keys, Editor-in-Chief, PSDNA

Industry News: Web Exclusive Content (www.powersystemsdesign.com)

Powerline> TI's Intuitive Fusion Digitial Power™

Power AEG Delivers Expanded Portfolio, Reported By Cliff Keys, Editor-in-Chief, PSD

MarkeiMaien Digital Conversion & Control ICs power Strong Growth, By Ryan Sanderson, IN

**Design Tips** Power Supply Development Diary - Part I, By Dr. Ray Ridley, Ridley Engineering

### 🔏 Teeli falk

Gallium Nitride Hits the Market, Reported by Cliff Keys, Editor-in-Chief, PSDNA

**Cover Story** GaN- A New Era Begins, By Michael A. Briere, ACOO Enterprises.

#### **AC/AC Electric Drivetrain** Powering Agriculture, By Florentsev S.N., Izosimov D.B. RUSELPROM, Electric

Makarov L.N. RUSELPROM.

**Power Factor Control** Variable Speed Motor Solutions, By Mark Steinmetz, Vincotech

#### **Special Report – Digital Power**

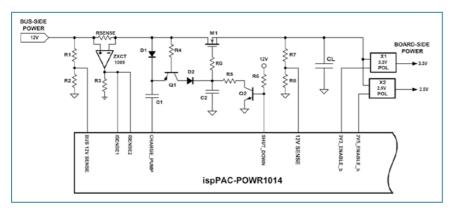

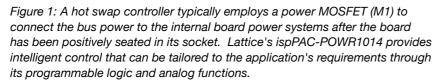

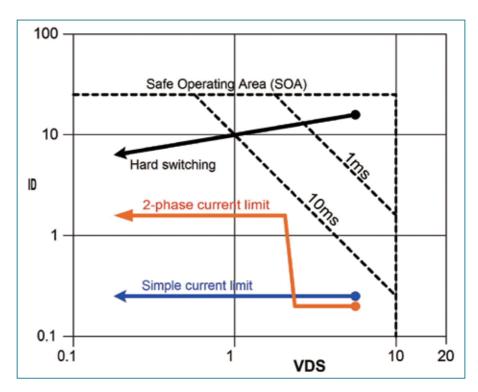

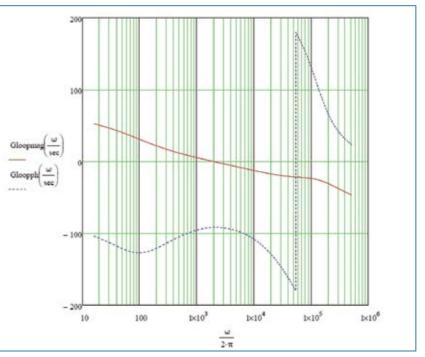

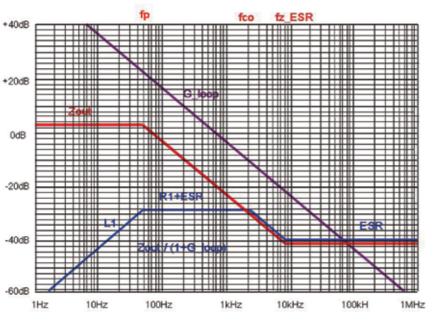

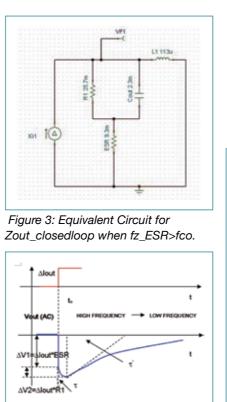

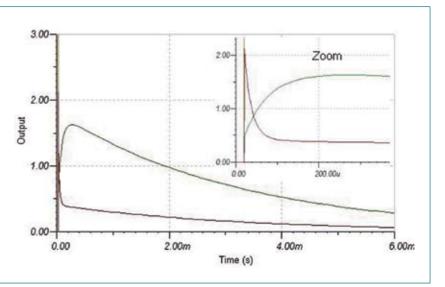

The Future of Digital Power, By Benoit Herve, Powervation. Digital Power Matures, By Patrick Le Fèvre, Ericsson Power Modules Intelligent Load Switching, By Srirama Chandra, Lattice Semiconductor Corpor Managing Multirail Systems, By Dave Clemens, Linear Technology Corporation Modeling of SMPS Output Impedance, By Pietro Scalia, Texas Instruments...

New Products: Web Exclusive Content (wwww.powersystemsdesign.com)

Solar Gets Competitive, Reported By Cliff Keys, Editor-in-Chief, PSDNA .

|                                                     | 4  |

|-----------------------------------------------------|----|

|                                                     |    |

|                                                     |    |

| NA                                                  | 6  |

|                                                     |    |

|                                                     |    |

| IS Research                                         | 8  |

|                                                     |    |

| g                                                   | 10 |

|                                                     |    |

|                                                     |    |

|                                                     | 13 |

|                                                     |    |

|                                                     | 16 |

| 2                                                   | 10 |

| Drive Ltd, Uss I.N. RUE, "Minsk Tractor Works", and |    |

|                                                     | 20 |

|                                                     |    |

|                                                     | 23 |

|                                                     |    |

|                                                     | 28 |

| ration                                              |    |

|                                                     |    |

|                                                     | 41 |

| systemsdesian.com)                                  |    |

|                                                     |    |

### We Systems Design

#### AGS Media Group

146 Charles Street Annapolis, Maryland 21401 USA Tel: +410-295-0177 Fax: +510-217-3608 www.powersystemsdesign.com

#### Editorial Director, Power Systems Design China Europe & North America Editor-in-Chief. Power Systems Design Europe & North America

Cliff Keys cliff.keys@powersystemsdesign.com

**Contributing Editors** Liu Hona Editor-in-Chief, Power Systems Design China powersdc@126.com

Ash Sharma, IMS Research ash.sharma@imsresearch.com

Dr. Ray Ridley, Ridley Engineering RRidley@ridleyengineering.com

Publishing Director Jim Graham jim.graham@powersystemsdesign.com

Publishe Julia Stocks julia.stocks@powersystemsdesign.com

**Circulation Management** Kathrvn Phillips Kathryn.phillips@powersystemsdesign.com

Research Director Meghan Corneal meghan.corneal@powersystemsdesign.com

Magazine Design Beata Rasmus. Evemotive beata@eyemotive.com

Production Manager Abby Wang abbyw@action-new.net

Registration of copyright: January 2004 ISSN number: Pending

AGS Media Group and Power Systems Design North America magazine assume and hereby disclaim any liability to any person for any loss or damage by errors or omis-sions in the material contained herein regardless of whether such errors result from negligence, accidentor any other cause whatsoever

#### Send address changes to: circulation@powersystemsdesign.com

Free Magazine Subscription, go to: www.powersystemsdesign.com

Volume 2, Issue 2

## **The Digital Power** Marriage

With the upwardly spiraling desire for energy efficiency in almost all things, we are now seeing a revolution in technology and products hitting the market. This is not restricted to the super-spins of existing products or the tuning of power systems to hit the sweet spots, but radical changes are quietly taking place. It wasn' t so long ago that the fiercely contested 'intrusion' of digital power techniques almost looked like succeeding. Some of the more traditional, although highly experienced and talented, analog engineers rejected the idea that digital power techniques could add value to power systems arguing that analog techniques could do everything the industry required and at that time, they were probably right. But not any more.

Most now agree that the contribution already made by the skillful implementation of digital power has helped the engineer or system designer in automating design processes such as loop compensation that earlier could take an engineer a considerable amount of highly skilled work.

At the APEC conference held recently in Palm Springs, California, there was great evidence of this. I visited as many companies as I could in the three day

trade fair attached to the conference and was impressed by the volume and quality of new products and by the utilization of new technology on display. The economy may still be down, but innovation is certainly up, alive and flourishing. For those who could not get to this wonderful event. I am pulling together a roundup of the reports I made from my meetings which will be posted on our website.

But in our expanding industry, it's not just the products that make a success. Firms are nurtured, guided and driven by their management. I talked to several senior managers at the conference and it was good to see that creativity and good strategic thinking is alive and well. There will always be the spreadsheet folks, but the ones that can motivate their people forward in a common direction that will bring success have to be experienced leaders. This does mean the deskthumping or super-dynamic egotist, most likely quite the opposite. It is very easy to see the companies that have developed a culture of genuine belief and trust in their leadership, a common goal and a passion to succeed. You can see it in their eyes.

I hope everyone is receiving the Power Systems Design 'PowerSurge' online news blast. We are running this on a weekly basis with content to keep our readers up-to-date in real-time on the latest products, industry news and my industry interviews.

All the best!

CLIF Key)

Editor-in-Chief, PSDNA Cliff.Keys@powersystemsdesign.com

## **Powerful Products** For Powerful Electronics.

Power Distribution Systems

#### Learn more about our power electronics solutions by Booth #12-439 visiting us at

#### PDS

Power Distribution Systems specializes in the design and manufacture of custom designed busbars. RO-LINX® busbars serve as power distribution highways. Rogers laminated busbars provide a customized liaison between IGBT modules, capacitors and the power source.

- Low Inductance

- Design for Controlling Partial Discharge

- Compact Design

- UL Rating

TMS

#### Empowering your energy.

For more information on our Thermal Management Solutions (TMS), visit us at www.roaerscorp.com/tms. You can find more information on our Power Distribution Systems (PDS) at www.rogerscorp.com/pds.

USA +1-480-917-6137 EUROPE +32-9-235-3611 ASIA + 65-6747-3521

### Thermal Management **S**olutions

Rogers' HEATWAVE<sup>™</sup> high performance AlSiC materials combine excellent thermal conductivity and controlled thermal expansion with low density and high stiffness to match the performance characteristics of modern power semiconductor device packaging solutions and systems.

- Improves Longterm Reliability

- Reliable Thermal Performance

- Ease of Integration into Applications

- High Stiffness & High Mechanical Stress

### Power **line**>

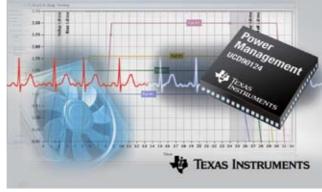

## **TI's Intuitive Fusion Digital Power**<sup>TM</sup>

## Designer tool speeds configuration

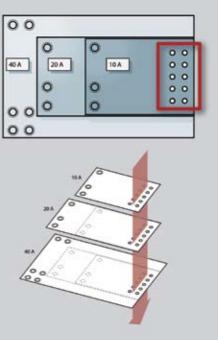

exas Instruments has launched the industry's first 12-channel sequencer and system health manager with fan control and multiphase PWM clock generator. The UCD90124 integrates system power management and system thermal management into one device, which reduces board space and eases design, while providing highly intelligent system health monitoring. The sequencer features power supply margining and comprehensive non-volatile error logging, allowing customers to diagnose power supply failures in their systems.

The UCD90124 is a 12-rail PM-Bus/I2C addressable power-supply sequencer and system-health monitor. The device integrates a 12-bit ADC for monitoring up to 13 power-supply voltage, current, or temperature inputs. Twenty-six GPIO pins can be used for power supply enables, power-on reset signals, external interrupts, cascading, or other system functions. Twelve of these pins offer PWM functionality. Using these pins, the UCD90124 offers support for fan control, margining, and general-purpose PWM functions.

Fan-control signals can be sent using PMBus commands or generated from one of two built-in fan-control algorithms. PWM outputs combined with temperature and fan-speed measurements provide a complete fan-

control solution for up to four independent fans.

TI's easy-touse Fusion Digital Power Designer Graphical User Interface (GUI) allows the designer to configure the UCD90124 via a PMBusTM/I2C interface. The free, downloadable tool simplifies the development process and speeds time-to-market by

allowing the designer to configure all device parameters in minutes.

To download the Fusion Digital Power Designer see: www.ti.com/fdpd-pr.

#### Kev features and benefits of the UCD90124

• Sequence and monitor up to 12 power supplies while simultaneously margining up to 10 rails.

Manage power and monitor and control up to four fans with a single device.

• The UCD90124 has a built-in temperature control algorithm that automatically adjusts fan speed based on five configurable temperature zones. Alternatively, designers can use their own temperature control algo-

#### 12-channel sequencer, system health manager with fan control

rithm running on an external host and communicate desired fan speed via I<sup>2</sup>C commands. This level of intelligent system thermal management helps reduce audible system noise and extend the operating life of the fans.

The auto-calibrate function automatically determines the turn on, turn off and maximum duty cycle for the fan, which allows the designer to think in terms of operating speed and also accounts for environmental variables in fan speed.

The UCD90124 can generate up to eight clocks with configurable frequencies from 15.259kHz to 125MHz and phase shift from 0 to 360 degrees, easing synchronization of switchmode power supplies.

www.ti.com

#### 2SP0115T Gate Driver

Unleash the full power of your converter design using the new 2SP0115T Plug-and-Play driver. With its direct paralleling capability, the scalability of your design into highest power ratings is unlimited. Rugged SCALE-2 technology enables the complete driver functionality on a single PCB board, exactly fitting the size of 17mm dual modules.

Combined with the CONCEPT advanced active clamping function, the electrical performance of the IGBT can be fully exploited while keeping the SOA of the IGBT. Needless to say that the high integration level provides the best possible reliability by a minimzed number of components.

### CONCEPT INTELLIGENT POWER ELECTRONICS

## Unleash Sheer Power!

#### SAMPLES AVAILABLE!

#### Features

Plug-and-Play solution 1W output power 15A gate current <100ns delay time ± 4ns jitter Advanced active clamping Direct- and halfbridge mode Direct paralleling capability 2-level and multilevel topologies DIC-20 electrical interface Safe isolation to EN50178 **UL** compliant 50.- USD @ 1000 pieces

### Power Player

## **AEG Delivers Expanded Portfolio**

I had the opportunity to talk with Laszlo Lakatos-Hayward, CTO of AEG Power Solutions (AEG PS) about the company's proud history and achievement throughout the world. He gave me an insight into where the company is now and its powerful strategic direction going forward.

#### Reported by Cliff Keys, Editor-in-Chief, PSDNA

EG Power Solutions is already a renowned and well respected company for its work in providing European and Asian-Pacific markets with a wide range of AC & DC power systems. The company has launched an intensive program to raise its US portfolio to match this achievement. The company, formerly Saft Power Systems, has a distinguished heritage in North America going back over half a century, with many of its systems operating reliably over decades of continuous trouble free service.

As part of its planned expansion, AEG Power Solutions is expanding its corporate operations in the US, specifically in Dallas, Texas and Markham, Ontario.

The company is headquartered in Amsterdam, Netherlands, with offices established in Texas in 2001. Its products are spread over the whole gamut of Industrial and commercial organizations.

AEG PS is adapting its offerings to renewable energy solutions in the North American market where the company is establishing design and applications engineering teams, to strengthen its service capability. Solar systems solutions for the commercial and industrial sectors are to be found at the top of the company's target list.

But achieving all this takes a highly concerted and determined effort. In North America as well as in Europe, there is a shortage of good, well qualified engineers. Over the past decade or so, the number of students enrolling into engineering degree courses in universities has declined. The more appealing Law and Medical courses have attracted more students simply because of the elevated prestige and earning capability they offer in the real world.

But all this is in a state of flux now. Engineering excellence is the route to energy efficiency and engineering

creativity and wisdom in its generation and application will improve our lives. History will certainly show that the contribution to the quality of our environment as well as that of future generations will be greatly enhanced by the pioneering achievements by skilful and talented engineers, led by visionary and committed management.

AEG PS is confident in its planned global expansion and especially in delivering its capability and system solution strategy to the North American market. It is currently seeking out and recruiting the very best in engineering talent.

AEG Power Solutions also looks forward to enabling smart grid applications with its intelligent and rugged power electronic solutions. The company can now offer to its customers a complete power electronic system solution for the newly expanded North American market that provides the same high level of innovation and reliability that AEG PS has been providing to European and Asia-Pacific markets for decades.

AEG Power Systems is ideally placed to become the ideal partner for the Industry and Commerce sector's total energy needs.

www.aegpowersolutions.com

### C AP Instruments Inc.

The world's most dependable

frequency response analyzer

## And the ultimate hands-on laboratory education for working power electronics engineers

## **Four-Day Power Supply Design Workshop**

Ridley Engineering offers power supply design workshops around the world. Dr. Ridley combines the teaching of theoretical and practical concepts, and hands-on experience with design software and lab instruments. Attend our intensive four-day workshop, where mornings are spent studying theory and design concepts, and afternoons are spent building power circuits and controllers.

#### Power Supply **Modeling & Control**

PWM Switch Model CCM and DCM Operation **Power Stage Characteristics** Voltage-Mode Feedback Design Current-Mode Power Stage Characteristics Design with Current-Mode Control

#### High-Frequency **Magnetics Design**

Optimal Magnetics Design Core and Winding Loss Component Parasitics Frequency Response Planar Design Structures Proximity Effects

SARL Ridley Engineering Europe ~ Chemin de la Poterne ~ Monpazier 24540 ~ FR ~ +33 (0)5 53 27 87 20 ~ Fax: +33 (0)5 67 69 97 28 Ridley Engineering, Inc. ~ 3547 53rd Avenue West, Suite 347 ~ Bradenton, FL 34210 ~ US ~ +1 941 538 6325 ~ Fax: +1 877 247 8595 Email: DRidley@ridleyengineering.com

### **A Powerful Combination**

With the world's most comprehensive design software

Our next workshop is May 25-28, 2010 in Atlanta, GA USA. Tuition is \$2500 and includes training, lab notes, POWER 4-5-6 software, and lunch. Reservations are now being accepted. Only 24 seats are available at each workshop. Download a reservation form at www.ridleyengineering.com

#### Hands-On Laboratory

Combined Lecture and Lab Learning **Build Power Supply Circuits Build Magnetics** Measure Waveforms and Components Measure Transfer Functions **Design Control Loops**

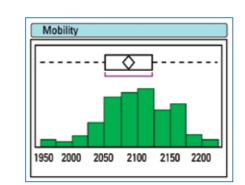

## Digital Conversion & Control ICs Power Strong Growth

By Ryan Sanderson, Market Research Analyst, Power & Energy Group, IMS Research

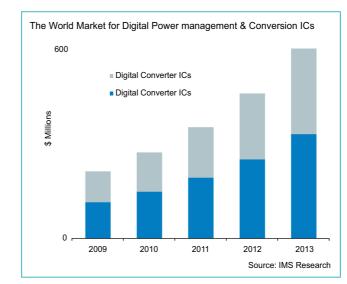

White many power IC suppliers reporting strong results for the fourth quarter of 2009 and underlying drivers looking much more positive, it seems safe to assume the market is now well into the recovery phase. Inevitably though, some areas of the power IC have a much more positive future projected than others. Of all the power IC markets IMS Research studies, digital power management and conversion ICs are forecast to see one of the highest growth rates over the next few years.

Latest projections from IMS Research's report on power management and driver ICs predict revenues of digital controller and conversion ICs are set to more than double over the next four years to around \$600 million. Despite this, opportunities for digital controllers and converters today are still very much limited to infrastructure and datacom equipment such as high-end servers, routers and base stations, though penetration of digital controllers in power supplies is growing. Digital converters are targeted at applications where space is very constrained and where customers are willing to pay a premium to get the smallest footprint; however prices

of digital solutions are now becoming much more competitive as economies of scale are realised.

So are more competitive prices of digital converters and controllers driving adoption? In essence the answer is yes, though a fair comparison can't be made on a chip-to-chip basis and there are other factors to consider. Digital controllers and converter ICs still have a much higher average selling price than their analog equivalents, but the overall system cost of an application can still be reduced using a digital solution. This partly comes down to the typical integration model, whereby if you can provide all of the power management functions in a single IC and save board space, you can produce a cheaper solution. However, there are other benefits of a digital solution which can lower costs further down the line. Improving energy efficiency is often easily achievable using a digital approach, and using integrated diagnostic feedback in order to assess and solve problems faster, can minimize system downtime which is particularly important in datacom/infrastructure applications.

The downturn may also act in favour of digital power vendors, as customers have had a chance to step back and assess their designs and consider using digital solutions whilst demand was reduced. Growth is, however, also attributable to the increased time digital power vendors have spent working very closely with end-equipment manufacturers to provide the most effective designs.

IMS Research predicts that these factors will fuel adoption in applications outside of the server/datacom markets such as high-end consumer

driving penetration of digital products to more than 10% of the total controller and regulator market by 2014. There is therefore a substantial threat to analog technology in the future. The analog industry powerhouses are already preparing themselves however, developing and releasing products in the digital market space. IMS Research believes that there will be more mainstream analog suppliers following suit in the next few years. The transition to digital solutions is now inevitable and is set to gain momentum. Digital power remains an extremely interesting market – and we will be watching it very closely!

www.imsresearch.com

### Power systems, Design

www.powersystemsdesign.com

To Receive Your Own **FREE** Subscription to Power Systems Design North America, go to: www.powersystemsdesign.com/ psd\_na\_subs/nalogn.htm

## **Power Supply Development Diary** Part I

This article begins a new series in which Dr. Ridley shows the multiple testing and revision steps needed to get a power supply from concept to a fully-working prototype.

Power Supply Development Time

Whenever I look at doing an off-line power supply development, I have a formula for calculating how long it will take. I lay out each step of the process, and estimate the maximum amount of time that each step might take. Then I double the result. After this, I am normally hard-pressed to finish on time.

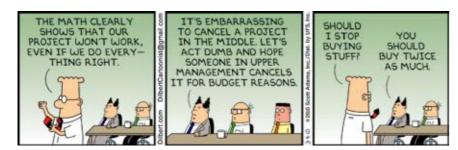

Why does this happen? It's because there are always unforeseen events that can drastically slow down the development process. After many years of working with switching power supplies, you learn that parts seldom behave as expected. When designing for a rugged environment of line variations, surges, short-circuits, and temperature variations, you can never be certain how long it will take.

It is hard to explain to those new to power supply design exactly what can go wrong. It is also hard to explain to management why the project schedule estimate is so long, and why we might need three or more board turns to get such a "simple" circuit right. Part of the reason for this difficulty is that when solving the problems of a power supply, we are often in a hurry and rarely have time to fully document the steps involved in fixing problems. Later on, we forget exactly what hap-

pened during that accumulated time.

I am guilty of following the same process. When working on a consulting design, or on a design for my own projects, the main objective is to be done as quickly as possible. Recently, however, I had a unique opportunity to take time to fully document the process from a power supply that was already laid out and ready for testing, to achieving full power. In following this process. I encountered many events I had seen in the past, and never documented.

#### **Power Supply Requirements**

The specification for the power supply was as follows:

1.Output 1 - 35 VDC @ 10A isolated

2.Output 2 - 35 VDC @ 10 A isolated 3.Maximum power 350 W (only one output fully loaded at a time, application is for audio.)

4.Input - 180 - 265 AC 5. Power Topology: Two-switch forward

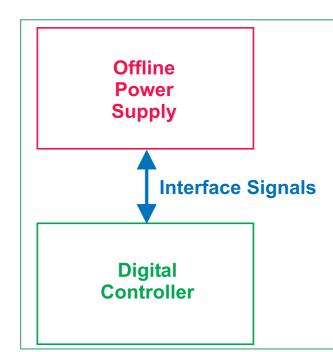

6.Controller: Digital controller from TI

The project was launched for several purposes. Firstly, I needed a bulk supply for an audio product which is currently running from a linear supply. Secondly, I had a digital designer who was eager to work for me for four months to try and learn some realworld power supply design. I have watched the promise of digital for over 20 years now, and felt is was finally time to see whether it could really work in a real-world product. And finally, I have always recognized the twoswitch forward as the most rugged topology available, but never actually built one from scratch. It was time to learn the details of the topology first hand.

The optimistic goal of the project was to finish in plenty of time so that a second converter with the same specifications could be built to run from the one digital controller. I didn't really expect this to happen in the given time frame, but it was kept as a goal. At the end of the project, I hoped to have

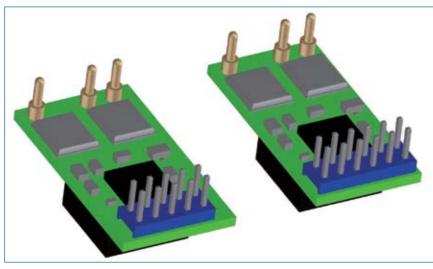

In early development, the most practical thing to do is separate the controller and power stage into two boards with a connector between them. Digital control forces you to this approach. This is also an approach I have always taken for analog power development. A controller from one project is often very applicable for your next project, and can be taken as a partial pc board and interfaced with a new power stage. This can save a tremendous amount of time, and is easy to do if you have a clear delineation between power and control.

During the development of most power converters, the control and power stage delineation becomes blurred with more and more communication from one to the other. The addition of ground planes confuses the line even more. This can lead to multiple problems with noise.

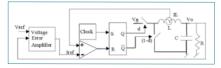

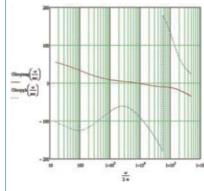

Figure 1: Separation of Power Circuit and Control Circuit with Interface Signals.

a working prototype, learn a lot about digital controllers and their guirks, and to impart some knowledge on analog power design.

As is often the case in the power supply world, things didn't guite work out as planned. At the end of the four months, I found that I still couldn't program a digital controller (although I learned a lot), and a digital designer couldn't possibly learn enough about high-voltage analog design in such a short time. However, I learned a tremendous amount about our analog design process and why it remains a challenge after so many years. The digital designer returned to the world of low-power offline work, and he learned more about his digital algorithms but not, unfortunately, what makes the analog world go round.

#### Separation of Power and Control

The first major lesson when working with a digital controller is that the layout needs are totally different from the needs of the analog power stage. The digital part of the board requires fine-pitch traces, and at least a four-layer board. On the other hand, the power stage requires heavy copper for high-current traces, large trace separation for voltage breakdown requirements, and plenty of allowance for thermal management, and bulky magnetics. And, as we shall see later in this series, you must be able to rework the power board manually to arrive at a well-designed converter in the shortest amount of time.

I always work with just two layers for power supplies. I like to be able to see all of the traces on the top and bottom sides to ensure proper spacing for all components. I also like to have the ability to move a trace if necessary, and relocate critical components without needing to layout a new circuit board.

Ground and other PCB planes should be completely

separate between the control board and power board. This is naturally achieved when the two boards are built separately, as is recommended for the early stages of digital control. This proper separation of the power and control boards will be discussed in more detail in the next article of this design series.

#### Full Schematic and Layout

The full schematic of the forward converter will be presented in the next article of this series. The power layout took about 1 month to complete, including the entry of all component footprints and placement of parts and traces. When working with existing parts databases, I usually expect this process to take me about two weeks. Less experienced designers can easily spend eight weeks on this process if starting from scratch.

The layout alone is a topic worthy of a complete series of articles. I won't go over that in full detail in this series, and will concentrate instead on the issues involved in completing the design after the first layout was complete.

#### **Debugging the Power Stage**

The guestion that has troubled me the most about digital control has been the issue of debugging. After many years of solving power supply problems where you must capture fleeting events and track them down through power stage and controller waveforms. I have alwavs wondered how this can be done in conjunction with the development of software and digital controllers, which may also have bugs.

Finally, I think I have resolved "how" this must be done. The answer is simple - the power stage must be fully debugged with an analog controller before the digital control is implemented! This is not a comfortable answer for the advocates of digital control. You must go through a complete analog design first, and then implement the digital and software aspects. It's clear that the development time of this approach will be considerably longer than just analog control. So the digital control implementation must offer significant advantages to justify this extra time.

An important item I learned about the difference between analog and digital designers is the way they think about their circuits and components. There is a fundamental divide between the two. Digital controllers, and microprocessors in general, have millions of transistors in their circuits. They are all expected to work within their specs, and work perfectly. When the software is complete, there should be no surprises. Designers do not expect the individual transistor circuits to misbehave.

In the analog power stage, however, you learn to expect almost every aspect of the circuit to misbehave. Nothing is exactly as documented in the textbooks or datasheets.

This will be clearly illustrated in the following parts of this series. There are many steps involved in the process, most of which involve events not to be found in any book or datasheet. There were several categories of problems to be resolved:

- 1. Failed components

- 2. Misconnected components

- 3. Component values

- 4. Unexpected operation in regions outside of the com ponent specifications.

- 5. Layout

- 6. High-frequency parasitics and noise

- 7. Snubbers and clamp circuits

- 8. Mechanical

- 9. Magnetics

- 10. Control stability

In all, in moving the converter from the initial board layout to a full power prototype, there were a total of 85 process steps. That does not include full characterization of the power stage and control optimization. The work is ongoing, when I have time to get back to the bench. I would expect in excess of 200 steps by the time the converter is done and ready for production.

For me, with 30 years experience, these steps moved very rapidly since I had seen many of the phenomena before. It took a total of approximately two weeks to implement them all. For the inexperienced designer, many of these steps can take days or weeks to solve. Quite often, the project can never be completed since the solutions are hard to find without experience.

#### Summary

The key points learned of the first stage of the project: 1. There must be a clean separation of power stage and controller, whether using analog or digital control.

2. A tremendous amount of analog experience is needed to implement a digital control system.

3. If you want your power supply to work with a digital controller, you must first debug it with an analog controller. You cannot take on both problems at once.

4. Resolving the power stage issues alone can be a very long process, and design experience is essential to expedite this.

In the next article of this series, I will begin describing the full schematic and the initial problems with the converter.

www.ridleyengineerig.com

## **Gallium Nitride Hits the** Market

### Has silicon reached the end of the road?

I had the pleasure to talk with Alex Lidow, CEO of EPC, Efficient Power Conversion Corporation. Alex is a true veteran of the power business dedicating his life to the pursuance of energy efficiency. He told me about his new company and the amazing products it will bring to the marketplace.

Reported by Cliff Keys, Editor-in-Chief, PSDNA

talked to Alex about the company' s drive, mission and purpose. He gave me a clear response, "We enable industry to benefit from the most efficient energy conversion using superior semiconductor materials. EPC designs, develops, markets, and sells Gallium Nitride based power management devices".

When I asked about the background for this strategy, I was reminded that industry in general and power management in particular, is a large and growing market that is constantly in need of higher energy efficiency.

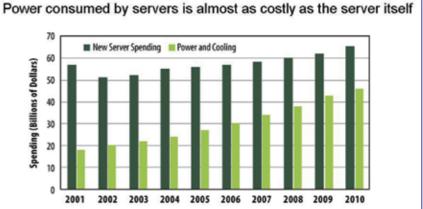

Silicon has now reached performance limits in power management and further improvements can only bring small incremental gains. Now the industry needs to go to the next level. Companies such as those running huge server farms to provide their services not only need to find a way of drastically cutting down on the losses that turn expensive and precious power into waste, they have to deliver ever higher levels of performance.

Gallium Nitride (GaN), which is grown on top of silicon, enables a game-changing price/performance ratio. This is a step-function improve-

www.powersystemsdesign.com

Alex Lidow, CEO of EPC, Efficient Power Conversion Corporation

ment and not another incremental gain. These devices work like a power Mosfet, designers can get used to the design rules transferring their skills without having to relearn their craft. The advantages are clear. These devices can handle higher step down ratios in converters for instance. Not just an incremental gain, but by a hefty 10x in performance. As an example a laptop power supplies are normally fed by a 20V source. The required step down can be done in one single step with GaN to reach the processor voltage.

EPC's served available market of \$7B is forecast to grow at a rate of 11.1% between 2009 and 2015. With

### 👗 TechTalk

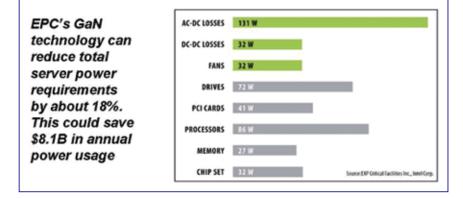

A dual processor server card consumes approximately 450W of power. Approximately 160 W are consumed by power conversion.

Gallium Nitride products reduce the considerable power loss experienced with conventional silicon solutions.

EPC's initial products are targeted at the Server, Switch, Hub, and Audio markets

| RDS(on)        | Voltage       |         |                   |                  |         |  |  |

|----------------|---------------|---------|-------------------|------------------|---------|--|--|

| m0hm           | 40            | 60      | 100               | 150              | 200     |  |  |

| 7              |               | EPC1005 | EPC1001           |                  |         |  |  |

| 25             | EPC1014       |         |                   | EPC1011          | EPC1010 |  |  |

| 30             |               | EPC1009 | EPC1007           |                  |         |  |  |

| 100            |               |         |                   | EPC1013          | EPC1012 |  |  |

| Intro<br>Dates | April<br>2009 |         | September<br>2009 | December<br>2009 |         |  |  |

| EPC#           | 1001 - 1005   |         | 1007 - 1009       | 1010-1014        |         |  |  |

aggressive pricing and a strong team in place, EPC intends to capture its fair share of the market.

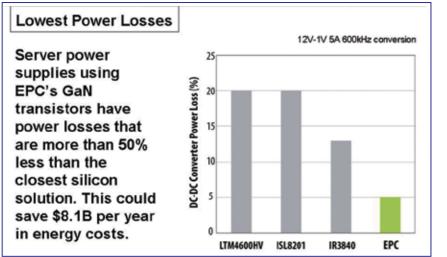

In the now highly scrutinized Served Market, a dual processor server card consumes approximately 450W of power. Approximately 160W are consumed by power conversion. EPC's GaN technology can reduce total server power requirements by about 18% which could save \$8.1B in annual power usage. Server power supplies using EPC's GaN transistors have power losses that are more than 50% less than the cloest silicon solution available.

But servers are by no means the end of the story. The market possibilities are almost without limit and here are just a few examples:

- Class D Audio can achieve unprece dented sound quality while lowering cost

- Laptops can reduce power consumption, save space, and lower cost

- Flat-screen TVs can incorporate 5.1 or 7.1 surround sound at a lower costs and with reduced space

- Cell phones can significantly in crease battery life and reduce costs

All this is not just theory though. These are real, fully supported products to revolutionize our industry. EPC's initial products are targeted at the Server, Switch, Hub, and Audio markets and will cover 90% of the existing power MOSFET market by the end of 2010.

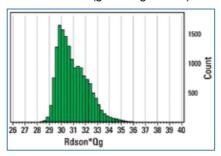

Gallium Nitride technology from EPC can provide significant benefits to new designs with the smaller die sizes and lower on-resistance involved. As accepted by manufacturers the on-resistance (R<sub>DS(ON)</sub>) for a given device area is a key determinant of product cost. The big groundswell of news in the media in the last few years regarding the attributes of Silicon Carbide devices has yet to gain the wide adoption predicted, probably due to the specialized fab

#### EPC's products will cover 90% of the existing power MOSFET market by the end of 2010

| RDS(on)<br>mOhm | Voltage |         |         |         |         |         |   |  |  |

|-----------------|---------|---------|---------|---------|---------|---------|---|--|--|

|                 | 40      | 60      | 100     | 150     | 200     | 400     | Γ |  |  |

| 4               | EPC1015 |         |         |         |         |         | Γ |  |  |

| 7               |         | EPC1005 | EPC1001 |         |         |         |   |  |  |

| 25              | EPC1014 |         |         | EPC1011 | EPC1010 |         |   |  |  |

| 30              |         | EPC1009 | EPC1007 |         |         | EPC1017 |   |  |  |

| 100             |         |         |         | EPC1013 | EPC1012 |         |   |  |  |

| 200             |         |         |         |         |         | EPC1016 |   |  |  |

| 500             |         |         |         |         |         |         |   |  |  |

|                 |         |         |         |         |         |         | _ |  |  |

requirements and resultant normally prohibitively high cost.

EPC's products have the same onresistance and are significantly smaller than the best silicon parts available on the market.

EPC is a brand new company consisting of a management team that is the most experienced in the power industry. The company's focus on GaN concentrates the whole design support and manufacturing on what is for sure a disruptive technology.

Top (degC) Bottom (degl

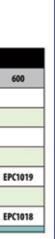

### **TW Paktron** multilayer polymer capacitors Latest Product Innovation Length (in)

**3rd Generation, Thermally Shielded** Capstick<sup>®</sup> Capacitor – Type CB4G-FS Compatible with industry standard high-temperature Pb-Free reflow solder assembly procedures.

#### FEATURES:

- Made In USA

- Long Life >10 Years

- RoHS-6 Compliant

- 100% Pb-Free (Unlike X7R Ceramic Caps)

- Proven Dielectric

- Ultra Low ESR

- High Ripple Current

- No Cracking **APPLICATIONS:**

#### 48V telecom/datacom

- HEV boost converters

- PFC front ends and SMPS off-line

- RFI/EMI suppression

- DC/DC converters

www.paktron.com

238.3

240.0

3.9

23.9 24.4 24.4

www.powersystemsdesign.com

The available market open to EPC is \$7B and is forecast to grow at an annual rate of 11.1%. With a mature supply chain - EPC is using well established and respected players in semiconductor manufacturing - the future looks very bright indeed. The company has enormous capacity already in place and is well prepared for the predicted adoption as manufacturers take advantage of the differentiation that GaN enables.

This was a brief insight into what EPC are driving to achieve. It is not the full story and I am sure we'll be hearing more from this newly established company. According to Alex, Silicon has reached the end of the road.

www.epc-co.com

1205 McConville Road • Lynchburg, Virginia 24502 USA tel. 434-239-6941 • fax. 434-239-4730 • itwpaktron@paktron.com

## Commercial introduction of GaN based power electronics

The initial commercial introduction of GaN based power conversion solutions by International Rectifier repre-sents the culmination of significant engineering efforts to resolve several fundamental barriers to achieving practical cost effective high performance packaged power devices.

#### By Michael A. Briere, ACOO Enterprises LLC, USA

#### Introduction

As has been previously discussed <sup>[1]</sup>, significant advances in the performance/cost figures of merit (FOMs) for power devices (e.g. Rdson\*cost or Ron\*Qsw\*cost) are required in order to improve the power delivery system FOM of efficiency\*density/cost. The reduction of total system costs can be substantially enabled by intelligent power elec-tronics which optimize performance/cost, in turn promoting the wide spread adoption of more efficient working loads, leading to a potential reduction in worldwide energy consumption by some 25%.

Over the last 3 decades significant engineering efforts have driven the improvement in the performance figure of merit of silicon based power devices by more than an order of magnitude. However, as this technology approaches maturity, it becomes increasingly expensive to achieve even modest improvements in the device FOM. It is estimated that less than a factor of two improvement will be economically feasible to achieve for 30 V FETs <sup>[3]</sup>, with perhaps a factor of five possible for 600 – 1200V silicon IGBTs<sup>[4]</sup>. Necessary further advances in power device performance must be achieved through the use of alternative materials. One of the most promising alternatives to silicon is gal-lium nitride based power devices.

Even though the basic GaN HEMT transistor was first invented over 15 years ago by M. Asif Khan <sup>[5]</sup>, significant development efforts on practical power devices using GaN-on-Si technology have been fairly recent, predominantly in the past 5-7 years. GaN based power devices are expected to improve rapidly over the next 10 to 20 years. In fact, it is expected that an order of magnitude in improvement in the key device performance FOMs will be achieved over the next 5 years.

#### **Barriers to Commercialization**

There have been however, several significant barriers to the commercialization of GaN based power devices. Chief amongst these is the cost of production. The production of power devices includes the costs of substrate, epitaxy, device fabrication, packaging, support electronics and development.

The viable economic based limit of about \$3/cm<sup>2</sup> for substrate and epitaxy cost set by the power device marketplace is exceeded by all substrate choices except silicon wafers. Multi-wafer MOCVD tools provide the required through-put and cost of ownership.

Next to the cost of substrate and epitaxial layers, device fabrication costs are the most critical. In fact, currently, sub-strate diameters of at least 150mm are required to achieve widespread commercial viability for power device fabrica-tion. In addition, the device fabrication costs are only acceptable if high volume, high vielding standard (silicon compatible) semiconductor fabrication lines are used. Similarly, the volume necessary to support the broad power device market (10 million 150mm wafer equivalents per year) requires scalability in device manufacture provided most readily by existing silicon device fabrication facilities.

Figure 1: Measured Hall Mobility (cm<sup>2</sup>/ Vs) for GaNpowIR III-Nitride HEMT epitaxy.

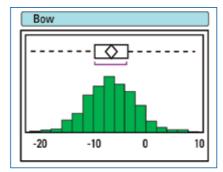

Figure 2: Measured wafer bow in microns after III-Nitride HEMT epitaxial deposition on 150mm silicon.

It is for these reasons that International Rectifier has developed its GaNpowIR technology platform using GaN-on Si hetero-epitaxy and device fabrication processing that can be performed in a standard modern silicon CMOS manu-facturing line with little modification to equipment or process discipline. It is this approach that allows this technol-ogy platform to provide power devices with compellingly superior performance/cost FOMs compared to silicon which will promote widespread adoption.

#### Initial GaNpowIR Device Focus

As has been previously reported <sup>[2]</sup>, the initial GaNpowIR products from International Rectifier will be low voltage (30V) dc-dc power stage modules. This approach is different from many commercial efforts which focus

on the ob-vious advantages of GaN based power devices at higher voltage ratings above 600V<sup>[3,6,7]</sup>. Though the distinct ad-vantage of low voltage GaN based HEMTs is not as obvious in terms of specific-on-resistance, it is important to note the it is the R(on)\*Qsw FOM which is critical to many of the low voltage applications. In this regard, the GaN HEMTs are expected to achieve more than an order of magnitude improvement over state of the art silicon devices within the next 5 years <sup>[2]</sup>. Quantitatively, this means a R(on)\*Qq device performance of less than 4 mohm\*nC compared to next generation silicon FOM of 45 mohm\*nC.

#### **Barriers Overcome**

One of the most fundamental challenges to the commercialization of GaN based power devices is the development of cost effective, high yielding, high throughput III-Nitride epitaxial processes on large diameter silicon wafers. It is well established that silicon is the substrate of choice for commercial GaN based power devices. The intrinsic mis-match in both lattice constant and thermal coefficient of expansion with the requisite III-Nitride epitaxial films causes threading dislocations, as well as significant macroscopic film stresses, which result in excessive wafer bow and plastic deformation (cracks) in the films. These issues have been addressed by engineering the proprietary epi-taxial film growth on standard thickness 150mm <111> silicon wafers to both eliminate most of the threading dislo-cations, resulting in 10°cm<sup>-2</sup>, predominately edge dislocations for 2µm thick films (comparable to similar thickness films grown on SiC), as well as compensating for the stresses due to thermal coefficient mismatches. These result in a high quality device layer, as demonstrated by the excellent electron Hall mobility of >2000cm<sup>2</sup>/Vs achieved in the 2 dimensional electron gas formed at the interface between the thick GaN buffer layer and the overlying AlGaN

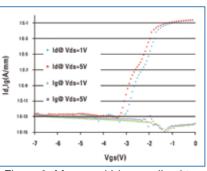

Figure 3: Measured Id normalized to gate width (850mm) as a function of Vgs for Vd= 1 and 5V,  $Lg=0.3\mu m$ .

bar-rier layer, as shown in Figure 1.

In addition, the resulting wafer bow is well within the required limit for device fabrication of <  $60\mu m$ , as shown in Figure 2 (bow in  $\mu m$ ).

It should be noted that truly crack free material to within 0.5mm of the wafer edge are consistently produced by this process in manufacturing volume. Further, the occasional crack that is found within 0.5mm of the wafer edge has been shown not to propagate during subsequent device fabrication.

Much of the reported constructions for GaN devices to date utilize Schottky gates and subsequently exhibit device leakage in operation of mA/mm of gate width. For a power device, which often has an effective gate width on the or-der of 1 meter, such gate leakage would result in an unacceptable power loss/heating. Similarly, the maximum oper-ating voltage has often been specified at reverse bias sourcedrain current densities of mA/mm of gate width. Another challenge, therefore, is the reduction of these leakage currents to less than 1uA/mm. This has been achieved through the combined use of a proprietary insulated gate construction and improved III-Nitride epitaxial film quality. This has resulted in gate and drain-source leakages of <10pA/mm, as shown in Figure 3. The resulting ratio of lon/loff of 10<sup>12</sup> is substantially better than reported elsewhere for GaN based devices and

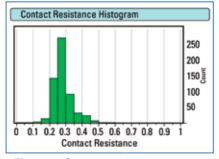

Figure 4: Contact resistance measured using standard transmission line technique in ohmmm for initial GaNpowIR platform.

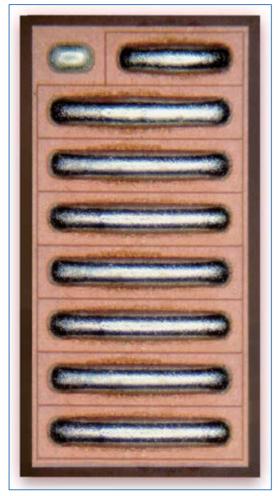

Figure 5: Topside view of a flip chip GaNpowIR device.

even exceeds that of comparable silicon based power devices.

Though the principle challenge to

develop high voltage GaN on Si based devices which substantially exceed the per-formance of silicon based devices appears met to a large degree [e.g. 3,6,7], substantial challenges existed to produce low voltage devices to exceed silicon device performance. One such challenge is the reduction and control of source-drain contact resistance. Though this component to the Rdson of a high voltage device (e.g. > 300V) is negligibly small, it can dominate the FOM for low voltage devices (e.g. <100V). In fact, in order to be competi-

> tive, the contact resistance for low voltage devices must approach 1micro-ohm cm<sup>2</sup> or <0.350hm mm. This has been achieved in a cost effective, high volume manner within the IR GaNpowIR technology platform, without the use of gold metallurgy, as shown in Figure 4.

Another challenge for the realization of commercially viable low voltage GaN devices is the effective conduction of the source-drain current from the internal to the external device terminals. This has been accomplished through the use of planarized multi-level metallization, common to silicon ULSI device fabrication. In addition, the use of a proprietary solderable front metallurgy (SFM) has been used to produce a flip-chip die, eliminating wire bonding and minimizing other package related parasitics. Figure 5 shows such a flip chip GaN power device.

Device yield is an important challenge for the commercialization of large area power devices. Unlike RF devices, with active areas < 1 mm<sup>2</sup>, power devices often have active areas >10mm<sup>2</sup>. It is economically imperative that yields

Figure 6: Wafer vield map for production GaNpowIR fabrication process for  $15mm^2$  die (green = good die).

Figure 7: Measured Ron\*Qg product for initial GaNpowIR technology platform.

> 80% are commonly achieved for such large devices. Figure 6 shows a wafer map of device yield for 15mm<sup>2</sup> devices, demonstrating the necessary level of process maturity for commercialization.

It is interesting to note that much of the remaining yield loss is unrelated to the properties of the III-Nitride epitaxial layers.

Figure 7 shows the distribution for the RQ FOM for a typical wafer batch of low voltage product die, demonstrating that the target of 30mohm\*nC for this first generation technology platform has been achieved <sup>[2]</sup>.

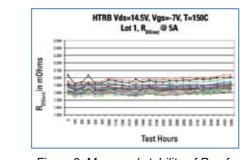

Finally, the stability of device incircuit performance is a prerequisite to commercialization. Figure 8 shows the Rdson stability for a random selection of low voltage GaN power devices.

As can be seen, the stability of this critical FOM is excellent under ac-

Figure 8: Measured stability of Ron for large (2.5 meter Wg, Lg=0.3µm) power device under constant reverse bias stress for >4000 hrs.

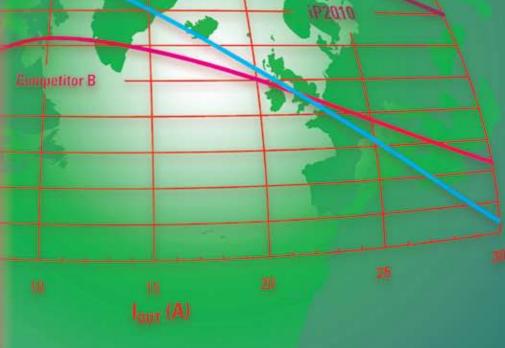

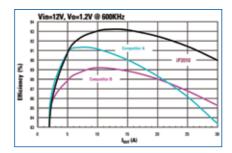

Figure 9: Measured power conversion efficiency for initial GaNpowIR product, iP2010, a 12V<sub>in</sub> to 1.2V<sub>out</sub> POL converter power stage operating at 600kHz compared to two silicon based alternatives.

celerated conditions for >4000 hrs. In fact, over 1,000,000 device hrs of reliability testing has shown performance in line with silicon based device specifica-tions. Tests have included, gate stress, reverse bias stress, constant current (2x specification), temperature humidity bias, package testing for MSL and temperature cycling, high temperature operating life and intermittent operating life tests.

#### First Product

In order to realize the potential of the GaN based power devices, it is necessary to develop companion technologies such as high speed drivers, low duty cycle capable PWM controllers and low parasitic packaging <sup>[1]</sup>. For example, the transition times (and dead time) are on the order of 1ns<sup>[1]</sup>, making it necessary to provide intelligent and fast deadtime control for the drivers

in order to realize the optimal performance made possible by the GaN power device.

The first product release to production on the IR GaNpowIR technology platform is a 30A capable 12V buck con-verter power stage product. It incorporates the control and synchronous rectifying switches together with the intelli-gent gate driver in a low parasitic LGA package. Figure 9 shows the measured power conversion efficiency for this first generation GaN product compared to competitive silicon based solutions.

Here it can be seen that the GaN based power devices provide more than a 3% improved conversion efficiency over state of the art silicon FETs. In adition, by enabling this high efficiency at 600kHz, this GaN based power solution enables the use of all ceramic capacitors in the power converter, thereby enhancing system reliability.

As has been previously discussed <sup>[1]</sup> further improvements in LV GaN based power devices (e.g. RQ<5) will allow for truly revolutionary performance of efficient (85 to 90%) single stage power conversion (e.g. 12V to 1.2V) at >50MHz frequencies, eliminating much of the output filter components, significantly reducing costs, and shrinking the converter size by more than a factor of ten. Perhaps more importantly, this higher frequency operation enables the more intimate positioning of the conversion stage with the electronic load. This eliminates a significant amount of parasitic power losses in the output filter and PCB/ package. The resulting simultaneous improvement in power conversion density, efficiency and cost represents the true value of GaN based power device development for LV ap-plications, as it is unknown how to achieve such performance/cost using silicon based devices.

Perhaps even more importantly, the

IR GaNpowIR technology platform represents a cost effective platform for true power integrated circuits, incorporating a range of voltage capable devices with best in class performance. This will allow system on a chip integration, such as complete AC-LV DC conversion and high power monolithic inverters for motor drives and power distribution. More than the replacement of silicon discrete devices with GaN based devices, this platform opens a new era for integrated power conversion.

#### Conclusion

The first commercially viable GaN based power device platform has been introduced, overcoming several significant barriers, particularly cost. First products focus on low voltage applications, resolving technical issues particular to these class of devices. General solutions of high quality, crack free III-Nitride epitaxy in a production environment as well as low contact resistance and low device leakage levels have been achieved. Excellent device stability as well as commercially acceptable device yields have also been achieved.

More than the replacement of silicon discrete devices with GaN based devices, this platform opens a new era for in-tegrated power conversion.

References

[1] M.A. Briere, Proceedings of PCIM Europe 2009

[2] Briere, M.A., Power Electronics Europe (7), October/ November 2008 pp. 29-31

[3] Ikeda et.al. ISPSD 2008 p. 289 [4] Nakagawa, A., ISPSD 2006 p.1 [5] Khan, M.A. et.al, Appl. Phys. Lett (63) p.3470, 1993.

[6] S. Iwakami et.al. JJAP vol 46 (24) 2007 pp L587-L589

[7] Selvari et.al. IEEE EDL vol 30 (6) June 2006 p.588

www.irf.com

## **Powering Agriculture**

### Tractor with AC/AC electric drivetrain

The world of power engineering finds its way into almost every application we come into contact. Now, even on the farm we can find up to the minute power technology in a piece of equipment that for almost generations has been a simple yet essential workhorse, the tractor. Our power colleagues in Russia send in this singular report.

By Florentsev S.N., RUSELPROM – ElectricDrive Ltd. General Director; Izosimov D.B. RUSELPROM - ElectricDrive Ltd. Vice-Director for Science; Uss I.N., RUE "Minsk Tractor Works" General Designer; Makarov L.N., RUSELPROM Corp. General Designer.

USELPROM Corp., a leading Russian electro-engineering development and manufacturing group jointly with Production Association (P/A) "Minsk Tractor Works" which is one of the world's largest enterprises for production of wheeled tractors, has developed an agricultural tractor "BELARUS-3023" featuring an AC/AC electro-mechanical drivetrain (EMD).

The application of EMD provides the following benefits:

Improved technical and economical parameters of the tractor

• Reduces dynamic loads on the units of tractor and diesel

· Reduces slipping of wheels, reduces "fuel consumption – performed work" ratio by up to 30%

• Provides continuous step-less variation of speed of the tractor and aggregated tools

Reduces cost of maintenance, repair and spare parts

Increases total reliability, controllability and comfort

A prototype concept-tractor was created in 2007-2008 and has now successfully passed benchmark and field tests. In the timeframe 2008-2009 prototype series of the "BELAR-US-3023" tractors have been manu-

Figure1: Tractor "BELARUS-3023".

factured and have passed tough trials in machine-test stations in Russia, Belarus and Ukraine. The tractor model "BELARUS-3023" was presented to a wide consumer audience at the largest agricultural exhibition AGRITECHNI-CA-2009 which took place at Hanover. Germany in November 2009 where the tractor was awarded a silver medal for innovation by the organizer of this display – German agricultural society DLG. RUE "Minsk Tractor Works" who have subsequently planned the release of the first serial party of tractors with complete traction electric equipment set (TEES) by RUSELPROM Corp. for the year 2010.

Parameters of the tractor "BELAR-US-3023" of prototype series (Figure 1):

- Type general purpose

- Wheel formula 4x4

- Nominal force at hook 50kN

ICE – Detroit Diesel S40E 8.7 LTA M146

- ICE power 220kW (300h.p.)

- Engine nominal rotational speed 1750rpm

- Engine maximum torgue 1457Nm

- Engine torque reserve factor -40%

· Specific fuel consumption at diesel operational power - 249g/(kWh)

- Optimum fuel rate 195g/(kWh)

- Fuel tank volume 500liters

• Drivetrain - electro-mechanical CVT, AC drive, two mechanical ranges, 2-step automatic or compulsory switching within each range by frictional hydro-operated clutches, rear axle

• Speeds in ranges, km/h: - Field – 0...18

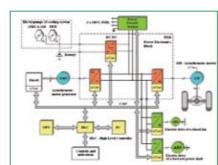

Figure 2: Block-diagram of the TEES of tractor "BELARUS - 3023" developed by RUSELPROM Corp.

|                                   | [                                     | r           |  |

|-----------------------------------|---------------------------------------|-------------|--|

| Parameter                         | MG, value                             | AM, value   |  |

| Туре                              | Asynchronous with squirrel-cage rotor |             |  |

| Number of phases                  | 3                                     |             |  |

| Power, kW                         | 220                                   | 183         |  |

| Nominal rotation speed, rpm       | 1750                                  | 1450        |  |

| Rotation speed range, rpm         | 8002200                               | -3600+ 3600 |  |

| Efficiency (with power converter) | 0,93                                  |             |  |

| Dimensions (length/diameter), mm  | 630/545                               |             |  |

| Cooling                           | liquid, 40liter/min                   |             |  |

| Weight, kg                        | 650                                   |             |  |

Table 1: Main MG and AM parameters.

- Road 0...42 (50)

- Reverse riding ability full

• Forward driving axle - with planetary final drives, self-blocked differential

• Rear axle – with differential with interlock friction coupling, planetary final drives

Overall dimensions (length/width/ height) - 6400/2630/3250mm

- Weight:

- Design 11500kg

- Operational 12500kg

- Maximum admissible 18000kg

- Baseline 3260mm

• Tyres (basic equipment, forward/ rear) - 540/65R30 / 580/70R42

• Minimum turning radius - 5.5m

The complete set of a traction electric equipment of the electromechanical transmission (Fig. 2) contains:

Asynchronous motor-generator (AMG)

Asynchronous traction motor (AM) · Power frequencies converters (inverters) of the generator and the motor • High level controller (HLC), the

managing director on CAN converters and a diesel engine

• Bidirectional converter DC-DC

The actual positioning of these elements on the tractor is shown in fig. 3

Parameters of the asynchronous motor-generator (MG) and traction asynchronous motor (AM) are given in the Table 1.

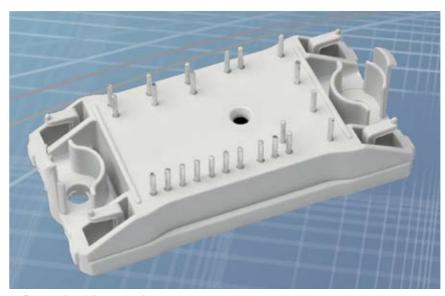

Power converters of AMG and AM are integrated in the power electronics block (PEB). Power converters are mady on base of integrated 3-phase voltage inverter modules SKAI from

SEMIKRON. Their maximum effective current per phase is 300A (continuously), nominal DC-bus voltage is 850V. Processor controllers TMS 320 are applied for vector control of electric machines. PEB is liquid-cooled; coolant flow is 20liter/min.

Information panel having seven modes of information display is located in the driver's cabin. It provides total control of various components and systems of the electric drivetrain and ICE.

The direction and speed of movement are controlled by joystick with mechanical interlock protecting from casual turning on. Movement is available within one of two ranges: operating (0...18km/h) and traveling (0... 42km/h). For simplicity of aggregating with mounted implements, the tractor has a function for traveling at a low speed while fully pressed accelerator pedal.

For simplicity of diagnostics and service, adjustment and control of equipment parameters, RUSELPROM-ElectricDrive Ltd. has developed a service computing system (SCS) special software for external PC. SCS allows adjusting settings of the control system, selectively visualizing current values of variables, saving and dy-

namically displaying them in operatorfriendly form, providing navigation and visualization of emergency logs of the high level controller (HLC).

Additionally to the main equipment RUSELPROM-ElectricDrive Ltd. has developed and delivers are a set of options:

• Autonomous power station with rated power of 172.5kW (3x400/220V. 50Hz, η≥95%, 1200x800x300mm, 85kg, IP65)

Electric drive of the forward PTO, mounted on tractor or on forward implements (55kW, 105Nm, η≥93%)

Electric drive of the ICE fan with precise air-flow control and reverse mode for ventilation and cleaning of the radiator (max. 20kW)

• Options are fed from the PEB DC bus through controlled inverters Advantages achieved in the tractor

- by application of the electric drivetrain:

- Effective, simple and reliable CVT Only 2 modes chosen manually ("field" or "road")

Automatic switching by a friction coupling providing effective acceleration in traffic mode

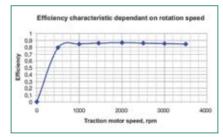

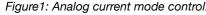

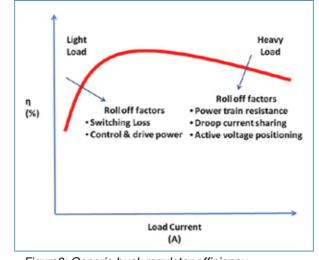

Possibility of operation with high efficiency in the overall tractor speed range (see Fig.4)

Efficient control of diesel operating mode depending on power demand Availability of modes of electric

Figure 3: Configuration of traction equipment in the tractor.

Figure 4: Dependence of the drivetrain efficiency on the traction AM rotation speed.

braking with motion energy transfer to diesel, tractor holding on ground ascents and descents, fixed moving for the pre-set small distance

Effective liquid cooling of the electric drive

Advantages in the comfort and controllability:

· Simplicity and convenience of

gearbox controls

· Availability of several drivetrain control modes:

- Speed setup from pedal,

- Speed setup from joystick with possibility of rough and exact adjustment.

- Tractor positioning with possibility of diesel RPM control from a pedal in this mode

- Exact tractor speed stabilization by GPS

- Possibility of automatic and compulsory diesel RPM control while working with PTO

- Ease of movement direction variation

Experimental characteristic of the total drivetrain efficiency (from the ICE shaft to the output traction motors

shaft) dependant on the AM rotation speed at maximum torgue and maximum power is given in Figure 4.

After the significant success with this design, RUSELPROM Corp. is ready to be a partner to vehicle manufacturers for development, manufacture, preproduction tests and serial production of TEES for step-less automatic EMD, both for on-road and off-road vehicles such as wheeled and tracked agricultural and industrial tractors, dozers, building/ road-building machines and other similar vehicles.

For further information contact florentsev@ruselprom.ru or visit the website.

www.ruselprom.ru

## **POWER YOUR WORLD!**

The Global Source For All Planar &

NEW Power Modules for 500W to 50kW **Solar Inverters** Widest Selection of Standard Inverter Modules **Custom Modules Available** Part Number Voltage Amps APTGV30H60T3G 600V 30A APTGV50H60T3G 600V 50A APTGV75H60T3G 600V 75A 600V 100A APTGV100H60T3G APTGV15H120T3G 1200V 15A APTGV25H120T3G 1200V 25A APTGV50H120T3G 1200V 50A 50A + APTGV50H60BG 600V APTGV25H120BG 1200V 25A APTGV100H60BTPG 600V 100A S APTGV50H120BTPG 1200V 50A **Key Features & Benefits** • Unique Full Bridge Solution for Unipolar Switching DC-AC Inverters Optimized for inverter operation, reduced power loss · More efficient than "motor drive" modules Modern packages reduce stray inductance and resistance Smaller, lower cost magnetics Capable of high operating frequency Reduced EMI. "Quiet Switching" technology Phone USA: 541-382-8028 Microsemi Phone Europe: 33-557-92.15.15 © 2009 Microsemi Corporation

Tel: 954-428-3326 x203 Full engineering design capabilities allow you Fax: 954-428-3308 to specify 10 to 20,000 watts, from industrial / jim@paytongroup.com telecom / automotive to space applications. www.paytongroup.com

## **Variable Speed Motor Solutions**

### Increasing efficiency with power factor control

The words, "Global Warming, Carbon Footprint, and Energy Efficiency" are becoming mantras for the industrial manufacturing sector. With energy costs constantly rising leading to increased overhead costs, the need to use electrical energy in a more efficient manner by reducing the amount is at the fundamental basis of this crisis.

#### By Mark Steinmetz, Field Applications Engineer, Vincotech GmbH

ver 40 million electric motors are used in manufacturing operations in the United States alone.1 Electric motors account for 65 to 70 percent of industrial electrical energy consumption and approximately 57 percent of all electrical consumption worldwide.<sup>2</sup> Saving even a few percent of the world's estimated 16,000-plus terawatt-hours (TWh) annual consumption of electricity<sup>3</sup> amounts to several hundreds of trillions of watthours per year.

Governments around the world are mandating regulatory pressure to increase motor efficiency. In the United States, EISA (aka Energy Independence & Security Act - Public Law 110-140) was signed by President Bush on December 19, 2007 and will become effective on December 19. 2010. From this date, motor manufacturers may not sell motors built after December 19, 2010 with a lower nameplate efficiency than EISA allows. EISA applies to both NEMA and IEC motors with features described in the details of the law. EISA allows motors that are considered "finished goods" or are shipped from the factory before December 19, 2010 to be sold after

December 19, 2010, In March 2009, the European Union passed Minimum Efficiency Performance Standards (MEPS) for motors.

Brazil and China have current or planned mandatory electrical motor standards. Many motor applications will utilize an oversize motor for the required mechanical load. Some applications employ a motor's full speed operation and control the output by mechanical means. These types of implementation for motor applications waste precious energy, since they are

controller.

ran at full speed operation. Currently, the average motor in use today has an efficiency of 88 percent in converting electrical into mechanical energy. Even an efficient compliant motor can reduce energy by no more than 10%, even under optimum operating conditions (i.e. full line voltage). Industrial motor users are finding that further energy savings can be realized by using electronic speed controls (i.e. inverter based), which can reduce energy by 30%, and mechanical energy by 60%.<sup>4</sup> Numerous motors operate at light loads. According to a Department of

Texas Instruments<sup>®</sup> has made designing much simpler using their UCC28070<sup>®</sup>

Energy study, 44% of motors in industrial facilities operate at 40% or less of full load and are thus, operating inefficiently. A drive's contribution to energy savings lies in its ability to allow you to manage motor operations to reduce output power by controlling its speed. Managing motor speeds, ramps, and available torque translates directly into managing power consumption.<sup>5</sup>

#### Power factor

Electronic designers of are now looking to maximize the energy efficiency of a motor drive application using Power Factor Control (i.e. PFC). Utilizing an electronic drive to regulating the output speed of the motor for the mechanical load required, with the addition of Power Factor Control improves efficiency of the drive by correcting the out of phase voltage and current being used. Power factor is defined by the relationship between the instantaneous voltage and current waveform being applied. When the PF=1 (maximum), both the voltage and current are completely in phase with one another.

This happens when the load is purely resistive. If the current and voltage are out of phase, the power factor is less than one. This happens In the case of a motor. The load looks inductive, which causes an out of phase condition. Thus power being applied will not be used optimally, wasting energy. Since the voltage at the motor input is fixed, the current increases to compensate for this phase shift to supply the necessary mechanical power required. Not only does this situation cost more money to operate, it impacts infrastructure cost having to use larger conductors to power motors and larger circuit breakers. Finally, more heat is generated by the motor yielding a shorter operating life for it. Thus implementing a power factor design in a drive will yield less energy usage, lower implementation cost (size, mechanical, wiring, safety), flexibility (speed), and longer motor life.

Types of power factor control

Classic Power Factor Control (i.e. PFC) circuits used in many drive applications have been the single boost topology. Recently, Interleave Power Factor has gained much interest in the drive community. Each of these types of PFC topologies has distinct benefits. Let's take a closer look at what each has to offer the designer.

#### Cost Inductors

The single boost PFC requires a single boost inductor and power switch. However, in high power motor applications (i.e. 3HP or greater), the boost inductor becomes guite large. In addition, this larger coil has increased losses, is bulky, and costly due to the large amount of copper being used.

The Interleave PFC has two parallel boost stages working180° out-ofphase with each other. This results in the requirement to use smaller boost inductors. Two small current sense transformers are also need for feedback control. The two smaller inductor sizes are the result of the two boost circuits working 180° out-of-phase. This unique technique reduces both the input and output ripple current. The results of this lower ripple current will reduce total inductor boost volume and the size of the EMI filter. Thus overall lower systems costs are realized.

#### Link Capacitors

Depending on the allowable motor ripple current, the single boost inductor will require a large amount of electrolytic capacitors to smooth the output from the PFC. The Interleave PFC has roughly 50% less high-frequency output capacitor current requirements compared to a single-stage topology. This reduction in current can result up to a savings of 25% reduction in boost capacitor volume.

#### Complexitv

Single boost PFC circuits are supported by a wide variety of controllers. Thus as a mature technology, advanced designs by IC suppliers in reducing the amount of support

circuitry (i.e. discrete components) required by integrating functionality into the controller have been realized. Therefore, these types of circuits are easily implemented.

Previously, designing an Interleave PFC circuit was rather complex requiring a lot of analog circuitry. However, Texas Instruments® has made designing this topology much simpler using their UCC28070<sup>®</sup> controller. Although more support discrete components are required over the single boost type of PFC, the two out of phase boost circuits are identical making the design simple.

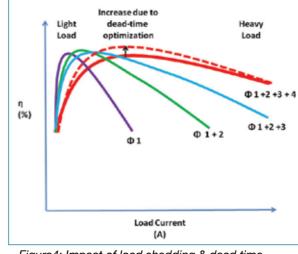

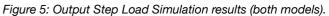

#### Efficiency