January/February 2013

Special Report: Energy Efficiency; Test & Measurement (pg35)

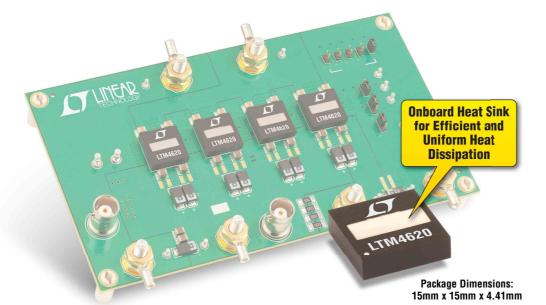

## Single 26A or Dual 13A µModule Regulator

### Scalable to 100A with Four LTM<sup>®</sup>4620 µModule<sup>®</sup> Regulators

**High Efficiency**

• Dual 13A or Single 26A Complete

MOSFETs and DC/DC Controller

Step-Down Regulator with Inductors,

• Pin-compatible with LTM4628: Dual

8A, Single 16A µModule Regulator

\*\*60°C Rise, T<sub>A</sub> = 28°C, 200 LFM, 12V<sub>IN</sub>, 1.2V<sub>OUT</sub>, 100A

**Features**

•  $4.5V \le V_{IN} \le 16V$

Sense Amplifier

\*4 x LTM4620 for 100A

•  $0.6V \le V_{OUT} \le 2.5V$

• Internal Temperature Sense

• ±1.5% V<sub>OUT</sub> Accuracy Over Temperature Including Remote

Precision Current Sharing

www.linear.com/umodule/techclips

/ Info

www.linear.com/umoduleguide

L7, L1, LTC, LTM, Linear Technology, the Linear logo and µModule are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

#### Computing

efficiency stepper motor driver IC voltage fault By Shyam Chandra,

Efficiently powering an always-on world By John Collins, Eaton

MARKETwatch Driver to energy efficiency continues to provide opportunities By Ryan Sanderson, IMS Research

**DESIGN**tips Flyback power supply development: part 1

By Dr. Ray Ridley, Ridley Engineering

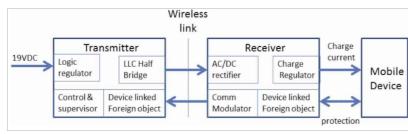

#### systems for portable electronics By Trevor J. Smith, Tektronix

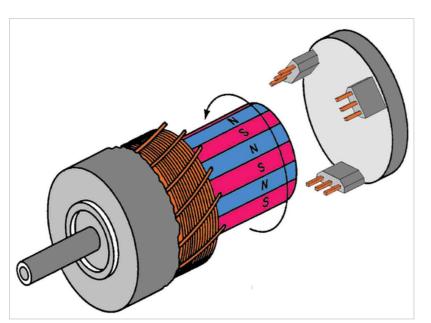

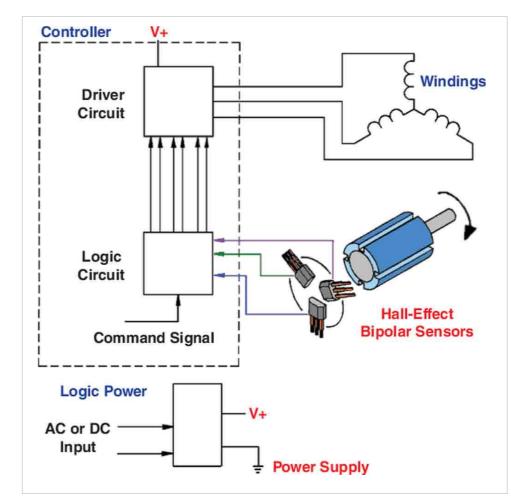

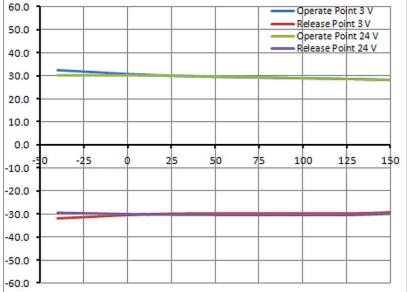

Hall-effect sensors deliver higher efficiency in brushless-DC motors

By Josh Edberg, Honeywell Sensing and Control

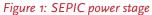

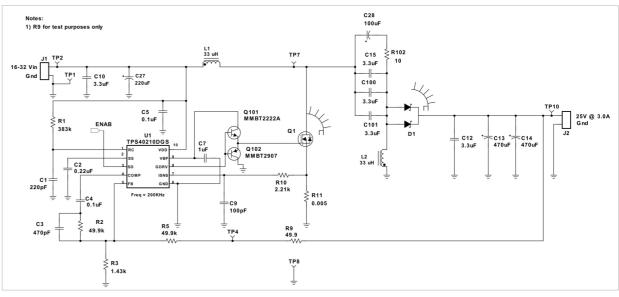

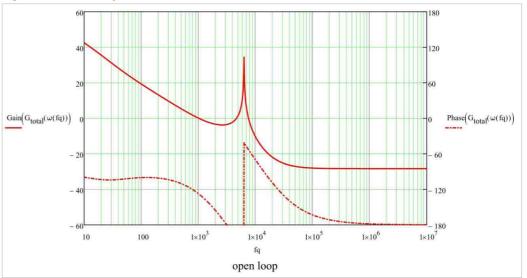

Designing a 75-W SEPIC By Florian Mueller, Texas Instruments

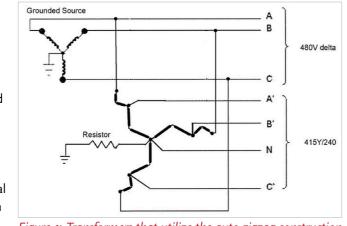

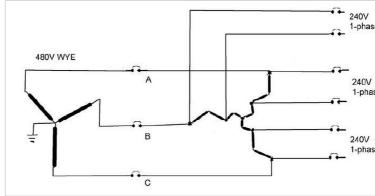

50 Two methods for increasing ACdistribution efficiency

By Robert W. Johnson, Eaton

Watch Videos

**Proof of Performance**

Excellent Thermal Performance\*

LED Lighitng

NORTH AMERICA

Convert a buck regulator into a highcurrent LED driver By John Kraft, Analog Devices

On Semiconductor introduces high-

**POWER**player

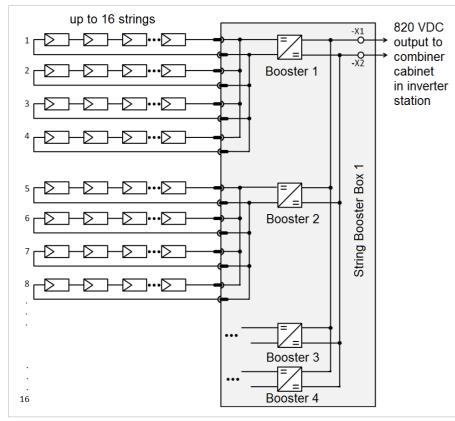

Solar Power String central inverter system By Frank Hinrichsen and Mark Ahmling, Wind and Sun Tech

#### SPECIAL REPORT:

#### ENERGY EFFICIENCY: **TEST & MEASUREMENT**

#### Wolfgang Dreipelcher, EPCOS

#### **TECHNICAL FEATURES**

COVER STORY

over 100-m CAT-6e cable

90-W plug-n-play Power over Ethernet

By Alison Steer, Linear Technology

#### POWER SYSTEMS DESIGN JANUARY/FEBRUARY 2013

Flash corruption: software bug or supply-

**COVER STORY** Faster switching in inverters (pg 13)

Highlighted Products News, Industry News and more web-only content, to: www.powersystemsdesign.com

**SPOTLIGHT** on Power Technology

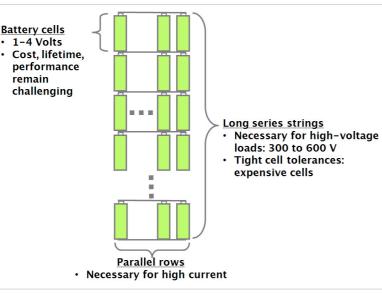

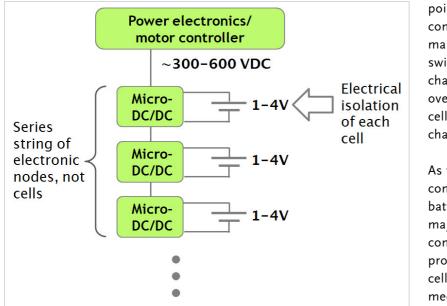

Rethinking battery management for EV's and grid-tied energy storage By David G. Morrison, Editor, How2Power.com

#### GREENpage

Test and measurement of a straw in the wind By Gail Purvis, Europe Editor, Power Systems Design

#### Dilbert

AGS Media Group 146 Charles Street Annapolis, MD 21401 USATel +410.295.0177 Fax: +510.217.3608 www.powersystemsdesign.com

#### Editor-in-Chief

Joshua Israelsohn, Editor-in-Chief, Power Systems Design joshua@powersystemsdesign.com

#### **Contributing Editors**

Gail Purvis, European Editor, Power Systems Design Gail.Purvis@powersystemsdesign.com

Liu Hong, Editor-in-Chief, Power Systems Design China powersdc@126.com

Ash Sharma, IMS Research Ash.sharma@imsresearch.com

Dr. Ray Ridley, Ridley Engineering RRidley@ridleyengineerng.com

David Morrison, How2Power david@how2power.com

#### **Publishing Director**

lim Graham jim.graham@powersystemsdesign.com

#### Publisher

Julia Stocks Julia.stocks@powersystemsdesign.com

#### **Circulation Management**

Kathryn Philips kathryn.phillips@powersystemsdesign.com

Magazine Design

Louis C. Geiger louis@agencyofrecord.com

#### **Production Manager**

Chris Corneal chris.corneal@powersystemsdesign.com

Registration of copyright: January 2004 ISSN number: 1613-6365

AGS Media Group and Power Systems Design Europe magazine assume and hereby disclaim any liability to any person for any loss or damage by errors or ommissions in the material contained herein regardless of whether such errors result from negligence, accident or any other cause whatsoever.Send address changes to: circulation@powersystemsdesign.comFree Magazine Subscriptions,

go to: www.powersystemsdesign.com

Volume 5, Issue 1

### Simulation anyone?

One of the more interesting automated design developments recently at the University of Dundee is in the field of advanced drugs, which for complex conditions and multiple targets, cause complex and difficult chemistries in need of optimisation. Dundee took the US baseball's *Moneyball* approach by using advanced statistical and data analysis techniques.

Thanks to sensors, improved data capture and organised drug design databases, the developed algorithm has been able to learn from the human experience of drug design, mimicking it on a massive scale, and iterating it, to solve complex design problems. America's ITRS (international technology roadmap for semiconductors) estimates that the use of such simulation tools reduced chip development times and costs by about 40%.

It has certainly been the golden mean for GSS (gold-standard simulations) software that in its latest research where the 3D simulator ran simulations on random dopants, line edge roughness and metal gate granularity as main sources of statistical variability on an unprecedented statistical scale.

It emerges with the news that "If you can develop a metal-gate-last 28 nm FD-SOI technology you will be able to achieve an astonishing SRAM supply voltage, in the range of 0.5 to 0.6 V," says expert Professor Asenov. Small wonder GSS is part the Fraunhofer Institute's SUPER-THEME project for circuit stability under process variability and electro-thermal-mechanical coupling.

At the Fraunhofer Institute for Mechanics of Materials project manager Dr Dirk Helm and his scientists have use simulations to develop shape memory alloys, developing various objects, such as minuscule forceps for endoscopy, where its small dimensions and elasticity, can be thoroughly sterilized with no joints. Numerical simulation models allow researchers to calculate in advance the components, the strength and clamping force, and efficiently develop and manufacture the component.

"By using simulations, we can avoid producing most of these prototypes," said Dr Helm. " This saves costs because the raw materials for the shape memory alloys are very expensive and are sometimes difficult to work with." In addition, the researchers can estimate how durable the materials are through the simulations.

So smaller wonder, perhaps, that news from IT design-conscious Apple, is that it is to invest in WITNESS from Lanner-simulation software originally developed in the OR department of British Leyland Motors. The licence and maintenance agreements will put WITNESS at the heart of simulating and optimising business processes within Apple enable it to represent real world processes in a dynamic animated computer model and then experiment with alternative what-if? scenarios to optimise production across its business.

Best Regards,

Gail Purvis

Europe Editor, Power Systems Design www.powersystemsdesign.com

The widest selection of the newest products. Over 3 million products from over 450 suppliers.

Authorized distributor of semiconductors and electronic components for design engineers.

#### www.mouser.com

The Newest Products for Your Newest Designs®

nichicon

EMERSON

molex

FAIRCHILD

Amphenol

KEMET

**ON** Semico luctor

## **ON** Semiconductor introduces high-efficiency stepper motor driver IC

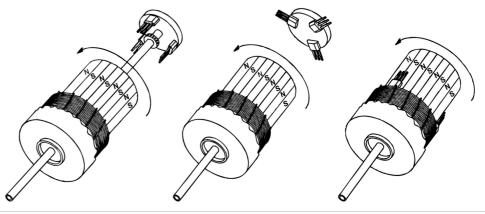

N Semiconductor has introduced the LV8702V, a new stepper-motor driver IC that delivers significantly improved efficiency compared to existing products on the market. The device has been specifically designed for office-automationequipment applications such as copiers, scanners, and multifunction printers.

"The poor energy efficiency of stepper motors utilised in a wide range of electronics applications has, for some time been an area of concern to communities the world over and a challenge to power system design engineers," said Tsutomu Shimazaki, general manager of power products for ON Semiconductor's SANYO division. "The LV8702V meets this challenge by providing a unique driving system that enables it to achieve no-load power-consumption savings of up to 80% and a reduction in peak motor current of approximately 77% (**reference** 1). This [stepper-motor driver] greatly assists our customers in the development of office automation electronics that meet the global demand for better energy efficiency."

#### Features and Benefits

In addition to reducing overall power consumption, the LV8702V helps reduce heat generation, vibration, and noise from the motor in applications such as positioning control in printers. Due to the increased efficiency, the surface temperature of the driver IC and the motor are decreased by up to 46°C and 28°C respectively (reference 2). This can overcome the need for cooling fans with the corresponding space and cost savings and enhanced system reliability.

The LV8702V stepper-motor driver IC detects motor conditions through driver waveform monitoring; power consumption is reduced by automatically reducing the current value according to the rotation speed or load of the motor. The new device has an operating voltage range of 9 to 32 V. Protection features include output-short protection, thermal shutdown, and a step-out detection function.

The LV8702V joins ON Semiconductor's portfolio of motor drivers that provide cost-effective, leadingedge performance for a broad range of applications and drive currents. Advanced functions such

The LV8702V achieves no-load power-consumption savings of up to 80% and a reduction in peak motor current of approximately 77%. as stall detection, step loss, and current drive optimization are now simple to integrate into applications where cost may have previously precluded high-end motor control.

#### Pricing and Availability

The LV8702V is available in an SSOP44J package measuring 5.6 x 15.0 mm. The device is budgetary priced at \$6.00 per unit for orders in quantities of 2,000 units.

#### www.onsemi.com

#### References:

- 1. Driving voltage: 24V; current setting: lout = 1 A; excitation mode: half step; speed: 1500 pps; motor: HB motor bipolar type; load: none

- 2. Driving voltage: 24V; current setting: lout = 2 A; excitation mode: half step, speed: 2000 pps; motor: HB motor bipolar type; load: none; power-on time: 20 min

## **Quality Products**

## **Impeccable Service**

A dedicated group of experienced Powerex applications engineers are available to serve as an extension of your design team.

## **Convenient Purchasing** Options

**Order Powerex Inventory** in Stock Online:

> www.pwrx.com/support/ HowToPurchase.aspx

**fE** 724-925-7272

## Efficiently powering an always-on world

#### By: John Collins, Global Segment Director, Data Centers, Eaton

data center's top priority has always been maintaining uptime. From this perspective, it's understandable that efficient energy use has historically been an oversight.

However, the entire industry has become aware that this was changing due to federal mandates, social pressure, and a global energy crisis that has caused the cost of energy to rise dramatically. In fact, energy related costs can represent up to 1/3 of operating expenditures for data centers, which makes efficiency attractive from both competitive and societal perspectives.

The key to balancing business and energy requirements is not to sacrifice reliability in the name of efficiency, but to become smarter about how we use power and collaboratively share successful techniques as they evolve. For example, common data-center efficiency losses are a direct result of computing, storage, and networking underutilization. However, much innovation has gone into minimizing these losses with the most remarkable

innovation being virtualization. Virtualization allows the utilization of servers to increase dramatically by decoupling IT hardware and software. One physical server now supports multiple operating systems running multiple applications. This allows data-center operators to reduce the number of servers and for processor power to match dynamically the varying demands of application workloads across a facility.

From a power perspective, what can we learn from the success of this computing model? The answer is the intelligent provisioning of power to the hardware that needs it, at the precise moment it needs it, rather than the unnecessary continuous feeding of energy into non-critical devices.

This approach is a modular power-infrastructure design. The core of this design, an intelligent central-software system, continuously monitors power requirements and ensures that only the modules necessary to supply the load at any particular time are delivering energy. The remaining modules hold in a low-power ready state, and the system is

ready to react instantly to changes in load level to meet demand.

There are two primary benefits to this approach: The modules that are in service operate efficiently because they are highly loaded and the modules that are in standby consume very little power. As a result, large energy savings are possible without compromises in service quality.

It is a system that is at the heart of some of the most energyefficient data centers operating in the world today. For example, Iliad Datacenter, one of France's largest co-location facilities, applied a modular system combined with an intelligent energy management system to boost energy efficiency at one of its sites from 92 percent to 98 percent.

If we are to continue meeting the needs of our always-on society without sacrificing the environment, we must take an intelligent, deliberate, and collaborative approach to managing power on an everyday basis.

www.eaton.com

# JEI JDEEU

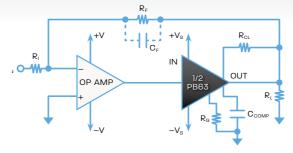

PB63 Power Booster: Hit Speeds of 1,000 V/µs With Multi-Channel Drivers

#### DUAL-AMPLIFIER TEAMS UP WITH SMALL SIGNAL OP AMPS TO DELIVER VOLTAGE AND CURRENT GAINS.

Apex Microtechnology is driving high voltage instrumentation with its next generation power booster. The PB63 is a high density, dual channel booster designed for evolving technologies such as high-speed industrial printers and pattern generators in flat panel display inspection (AUO) systems. The PB63 uses an exceptional 1,000 V/µs slew rate to deliver voltage and current gains when used in a composite amplifier configuration with a small signal op amp driver. Accuracy, offset, input noise and settling time are also optimized. The 1 MHz power bandwidth of the PB63 benefits these additional applications:

- Deflection circuitry in semiconductor wafer and mask inspection and lithography systems

- Programmable power supplies for semiconductor automated test equipment (ATE)

- Print head electronic drivers for industrial ink jet printers

#### apexanalog.com/psdnapb63

#### Power up at www.apexanalog.com/psdnapb63

## Drive to energy efficiency continues to provide opportunities

#### By: Ryan Sanderson, Associate Director, IHS IMS Research

ost will agree that 2012 proved to be a difficult year for the power electronics industry. Floods in Thailand resulted in a shortage of hard-disk drives, restricting PC production in the first half of the year. Global economic confidence worsened owing to increased uncertainty surrounding the *Euro-Zone Crisis*, and many semiconductor markets plummeted despite already low inventory levels.

Despite this, some applications offered pockets of growth. Although market conditions remain unstable, this is projected to continue in 2013 and beyond. In nearly all of these, the common driver is the demand for higher efficiency, driven by either consumer needs or legislation. Several examples spring to mind:

Demand for LED lamps and luminaires continues to grow, driving opportunities for power-supply and -semiconductor manufacturers. A key driver is the LED lamp's much lower power need to provide luminance comparable to incandescent bulbs. It is estimated that lighting currently accounts for approximately 19% of the world's energy use. IHS IMS Research predicts that, in 2016, around 15% of all lighting will use LEDs, reducing the global energy consumption for lighting by around 20%—a saving of \$100 billion over five years.

Power-supply efficiency in general is now a crucial factor for any OEM/ODM bringing a product to market, despite the majority of power supplies themselves being supplied by merchant vendors. The market for semiconductors in merchant power supplies is forecast to grow by more than \$500 million from 2012 to 2016, driven by various methods to increase efficiency. One is demand for active PFC, including approaches which use SiC diodes. Another is the adoption of synchronous rectification at the output which is driving demand for additional MOSFETs. A third is the adoption of digital power techniques and components.

The overall market for digital-power components—power supplies and ICs—has grown rapidly over the last few years but this has been mostly accounted for by telecom and datacom applications. However, the situation is set to change with design wins in lower cost applications such as notebook and adoption by merchant power supply vendors. This, along with the existing OEM adoption is projected to drive growth in a number of applications over the next five years.

As well as generating, distributing, and monitoring power, it is also predicted that there will developments in the way we store energy efficiently over the coming years. Transitions from battery technologies such as lead-acid to lithium or other alternatives has already begun and is predicted to accelerate, particularly in applications such as UPS, energy storage for reserve power, and motive power applications such as electric vehicles and material handling equipment.

These few examples demonstrate just some of the recent developments in the power industry relating to energy usage. The full list is much larger and should provide many new opportunities in 2013 and beyond. Happy New Year!

www.imsresearch.com

**DESIGN**tips

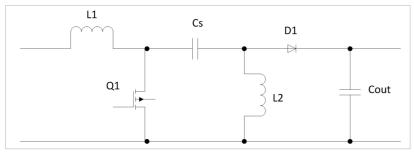

## Flyback power supply development: part 1

#### By: Dr. Ray Ridley, President, Ridley Engineering

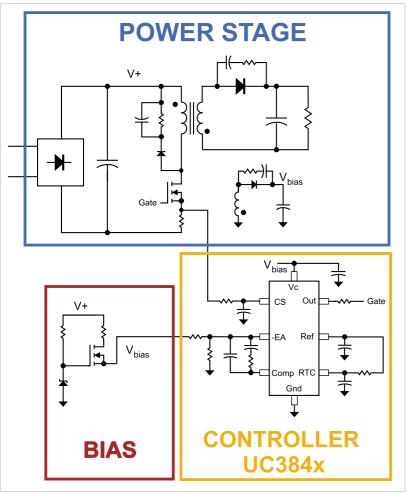

his article is the first of a series in which Dr. Ridley shows the steps involved in designing and building an offline flyback converter. The first part of the series presents the power supply architecture and schematic, including the control and bias circuits.

#### Flyback power converter

The offline flyback converter is a topology that is found in many applications. It serves as a bias supply for other power converter topologies, or as the main supply for low-power electronics systems, typically 50 W or less. The flyback is usually selected for the following reasons:

- 1. Low parts count

- 2. Single magnetic element

- Single ground-referenced switch

- 4. Ease of generation of multiple outputs

The disadvantages of the flyback converter are pulsating input and output currents, and a voltage stress on the switch that exceeds the input voltage. At low power levels, these issues are less important than the flyback

V+

Figure 1: Three parts of a five with interconnect signals advantages.

#### Power supply requirement

The specifications for the supply were as follows:

- Input Voltage: 185 to 2.

Output 1: 15 V DC @

- isolated ±10%

3. Output 2: 15 V DC @ mA nonisolated (bias regulation supply)

- 4. Maximum power: 22

- 5. Power Topology: Flyb

- Controller: 384x control from Texas Instrumer

| WE                      | R STAGE    | Output |

|-------------------------|------------|--------|

| irrent<br>dback<br>rive |            |        |

| oltage<br>edback        | CONTROLLER |        |

| Bias<br>ower            |            |        |

|                         | ÷          |        |

Figure 1: Three parts of a flyback converter—bias, control, and power stage

|             | The main output provides a relatively constant current, and the |

|-------------|-----------------------------------------------------------------|

| nts         | regulation range of 10% should                                  |

| e power     | be achievable through cross-                                    |

|             | regulation to the bias winding                                  |

|             | supply.                                                         |

| 265 AC      |                                                                 |

| ) 1.4 A     | Block diagram and circuit                                       |

|             | schematic                                                       |

| <u>ۇ</u> 50 | Figure 1 shows the block diagram                                |

| as and      | of the flyback power converter with                             |

|             | the control, bias, and power stage                              |

| 2 W         | blocks. Both the power stage and                                |

| back        | the bias circuit are fed directly                               |

| troller     | from the rectified AC input line.                               |

| ents        | The function of the bias supply is                              |

|             |                                                                 |

Figure 2: Schematic of an offline flyback converter with control and bias

to provide the operating voltage to the control circuit, and to do this with minimal dissipation.

The controller sends a gate drive signal to the power stage, and receives a current-sense signal from the power stage, used to protect and regulate the converter. Voltage feedback for the control loop is derived from the bias circuit. so there is no need for isolated feedback from the power stage. The choice of the correct controller from the UC384x family of parts will be discussed in a later part of this series.

Figure 2 shows the complete schematic of the flyback powersupply system. In this series of articles, each of the parts of this circuit will be discussed in detail, including test procedures.

#### **Bias Circuit**

The bias circuit shown in figure 2 consists of just a few parts. A FET is used as a linear regulator to start the control chip and its gate is fed by a resistor and zener diode combination.

A secondary winding is added to the power transformer to provide the bias power once the main circuit reaches regulation, and the linear regulator is then automatically shut off. This simple circuit provides a rugged and efficient way to power the controller.

#### Control Circuit

The 384x series of current-mode controllers were selected since they are readily available from multiple sources and are low cost with high performance (reference 1). While this family of controllers may seem outdated, they are still used extensively by experienced power designers and power supply companies who wish to have full control over all of the waveforms of the circuit. This will be discussed in detail later in this series of articles.

#### Power Stage

The power stage shown in figure 2 includes a power FET with voltage clamp, current sensor, transformer, output diode with snubber, and output capacitor. A second output winding on the transformer, together with another diode and capacitor, feeds the bias circuit voltage.

Having a discrete FET design allows much greater design flexibility than working with integrated controllers where the power FET is on the same die as the control circuitry. Also, higher voltage parts are available in the discrete FET package, and this can

# $AP = C_{\mathbb{R}} 2013$

March 17–21, 2013 Long Beach Convention Center Long Beach, CA THE PREMIER **GLOBAL EVENT IN POWER ELECTRONICS<sup>TM</sup>** Visit the APEC 2013 web site for the latest information!

## www.apec-conf.org

#### **SPONSORED BY**

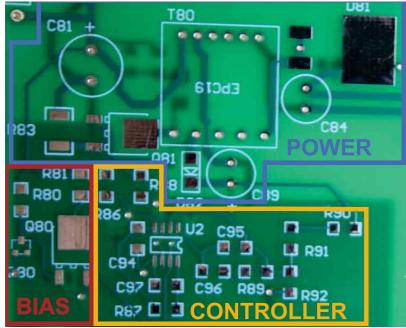

### Figure 3: PC board layout of the flyback converter ready for parts population

be important for rugged design.

#### Printed Circuit Board

This may not be welcome news to those who are about to embark on their first power supply design, but the first thing that needs to be done is a board layout. It is not a good use of time to try and test controllers and power stage parts with a wired breadboard. There are many critical layout paths in the circuit, and proper placement of parts can only be achieved with a real printed circuit board.

During a power supply development, even a simple flyback, you can count on needing a minimum of two iterations of the PCB. Most projects will iterate the board at least three times by the time it is ready for manufacturing. It is very important to begin your initial

testing on the PCB. The board layout creates parasitics and EMI issues that must be resolved as early in the design cycle as possible.

Figure 3 shows a photograph of the double-sided PCB designed for the flyback power supply. Notice that good partitioning of the control, bias, and power stage are maintained on the PCB, and this helps you work on the board later and to achieve good layout.

The details of the layout process are extremely important, and many of the rules and guidelines for proper layout were discussed in some detail in reference 2. If you are new to power supply design, the best thing to do is to dive into using a layout program and to learn as quickly as you can by making some boards and

testing them. If you are fortunate, you may have someone to mentor you through this process, but most engineers have to learn board layout the hard way, by themselves. Once you become adept at PCB layout, it becomes the fastest way to build test circuits for your power supplies.

#### Summary

The architecture and schematic of a complete flyback power supply have been presented in the first part of this series of articles. A standard 384x current-mode controller driving a discrete FET is to be used for the power system to provide maximum flexibility of design at a low cost.

In the next article, the input rectifier design and bias circuit will be discussed and test results for this part of the circuit presented.

#### www.ridleyengineering.com

#### **References:**

- 1. Current-mode PWM Controller, UC384x datasheet, Texas Instruments, June 2007, http://www.ti.com/lit/ds/ symlink/uc3842.pdf

- 2. Power Supply Development Diary Parts IX-XII, Ridley Engineering Design Center, Articles 42 through 45, http:// www.ridleyengineering.com/ index.php/design-center.html (note: These articles give design rules for PCB layout for power circuits.)

Cover Story

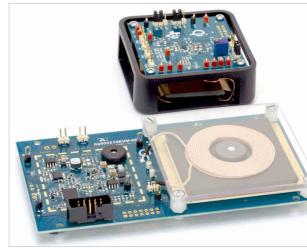

### Faster switching in inverters New EPCOS CeraLink capacitors benefit power-inverter's DC-link

circuits for fast-switching IGBT modules

By: Wolfgang Dreipelcher, Senior Director, Global Reference Designs, EPCOS

he powersemiconductor switches used in power supplies and inverters are based on two technologies, namely MOSFETs and IGBTs. MOSFETs can operate at relatively high switching frequencies significantly above 30 kHz but, unlike IGBTs, they have a very large chip surface area.

A new generation of IGBT modules from Infineon Technologies operates at frequencies of up to 100 kHz. Line-based and turn-off losses are of about the same magnitude in both systems. Fast IGBTs, whose manufacturing complexity is significantly lower and chip areas are often smaller than superjunction MOSFETs, are the basis of an IGBT<sub>3</sub> technology with high switching frequencies and an excellent priceperformance ratio.

Fast-switching systems require circuit designs with minimized ESR and ESL values. Accordingly, the passive componentsinductors, but especially capacitors-must also keep pace with the high switching frequencies. These in turn permit the use of more compact and

lightweight passive components, producing lower losses and increasing efficiency.

Capacitors are at the focus of these developments. They must combine high switching frequencies with low ESL and ESR values as well as an extremely compact design.

Conventional capacitor technologies are only partially able to meet these requirements. The EPCOS CeraLink represents a completely new approach: This advanced component is a ceramic multilayer ripple-current suppressor, also known as a link circuit or DC link capacitor; moreover, it functions as a snubber.

#### New inverter designs possible

EPCOS developed the CeraLink in the company's Competence Center for Ceramic Components in Deutschlandsberg, Austria. The expertise that formed the basis for this advanced component was gained, among others, over many years in the volume manufacture of piezo actuators.

The EPCOS CeraLink offers the advantages of ceramic capacitors

without their unfavorable characteristics. The patented multilayer component—based on antiferroelectric ceramic material with special copper internal electrodes—allows the use even more economically of both standard IGBTs and the new high-speed types with significantly higher switching frequencies. This naturally also applies to circuits with corresponding superjunction MOSFETs.

The innovative CeraLink combines high capacitance per volume with low ESL and ESR values, which thus enables significant improvements in efficiency, reliability, and space requirement for future IGBT and MOSFET inverter designs. Moreover, CeraLink is also available in a low-profile SMD design, making it suitable as a snubber for integration in power modules.

The EPCOS CeraLink components were adapted and continuously optimized for the first designs of special IGBT modules in close cooperation with Infineon Technologies, the market leader in IGBTs. This allowed the best results to be

| Insulation resistance       Typical values of 1 to 10 GΩ releakage current, especially at h         ESL       <4 nH         ESR       Typically <4 mΩ. Extremely low capacitances, resulting in low h         Operating temperature       -40 to +125 °C (for short period thus also suitable for SiC         Design benefits       Internal copper electrodes         Internal busbar       Optimized for variable use         Various terminal configurations       Terminals for soldering and pr technology         Compact case design       Case height optimized for wide semiconductor modules |                     |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|--|--|

| ESR       Typically <4 mΩ. Extremely low capacitances, resulting in low low capacitances, resulting in low low capacitances, resulting in low low losses and extremely high capability                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |  |  |  |  |  |

| ESR       capacitances, resulting in low l         Operating temperature       -40 to +125 °C (for short period thus also suitable for SiC         Design benefits       Internal copper electrodes         Internal busbar       Optimized for variable use         Various terminal configurations       Terminals for soldering and pridechnology         Compact case design       Case height optimized for wide semiconductor modules                                                                                                                                                            |                     |  |  |  |  |  |

| Operating temperature       thus also suitable for SiC         Design benefits       Low losses and extremely high capability         Internal copper electrodes       Low losses and extremely high capability         Internal busbar       Optimized for variable use         Various terminal configurations       Terminals for soldering and pr technology         Compact case design       Case height optimized for wide semiconductor modules                                                                                                                                                |                     |  |  |  |  |  |

| Internal copper electrodes       Low losses and extremely high capability         Internal busbar       Optimized for variable use         Various terminal configurations       Terminals for soldering and pr technology         Compact case design       Case height optimized for wide semiconductor modules                                                                                                                                                                                                                                                                                      | ods up to +150 °C), |  |  |  |  |  |

| Internal copper electrodes capability<br>Internal busbar Optimized for variable use<br>Various terminal configurations Terminals for soldering and pr<br>technology<br>Compact case design Case height optimized for wide<br>semiconductor modules                                                                                                                                                                                                                                                                                                                                                     |                     |  |  |  |  |  |

| Various terminal<br>configurations       Terminals for soldering and pr<br>technology         Compact case design       Case height optimized for wide<br>semiconductor modules                                                                                                                                                                                                                                                                                                                                                                                                                        | current-handling    |  |  |  |  |  |

| configurations technology Compact case design Case height optimized for wide semiconductor modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |  |  |  |  |  |

| Compact case design semiconductor modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ess-fit assembly    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | espread             |  |  |  |  |  |

| Rugged design Designed for snubber and pow<br>industrial and automotive syste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |  |  |  |  |  |

| Compatibility Special types for integration in<br>based on Si IGBTs and MOSFETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |  |  |  |  |  |

| Further benefits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |  |  |  |  |  |

| Suited for rapid rise times and high switching frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |  |  |  |  |  |

| Positive DC bias effect on the capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |  |  |  |  |  |

| Active cooling not always necessary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |  |  |  |  |  |

| Easy traceability thanks to QR codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |  |  |  |  |  |

Table 1: Optimized parameters and properties of the EPCOS CeraLink

achieved in terms of performance and energy efficiency. For both the EASY automotive series from Infineon Technologies and the corresponding types in industrial applications, all the relevant capacitor parameters

and properties were optimized towards more economy and efficiency (table 1).

The first designs of an on-board inverter, the Infineon EASYKIT DCDC, were based on existing

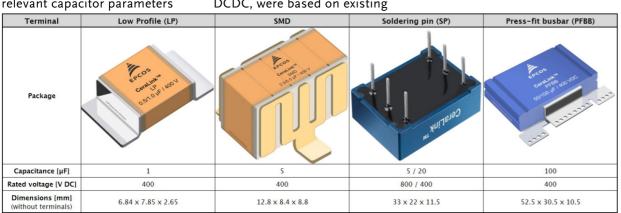

OEM specifications for rated voltages of about 400 V DC on the high-voltage side. The EPCOS CeraLink is currently available in several designs. Its capacitance range extends from 1  $\mu$ F to 100 µF at rated voltages of 400 and 800 V DC.

CeraLink capacitors are available with various terminal. The SMD versions (LP and SMD) are designed for direct integration in semiconductor power modules in view of the restricted space available (table 2). They can be soldered, bonded, or sintered.

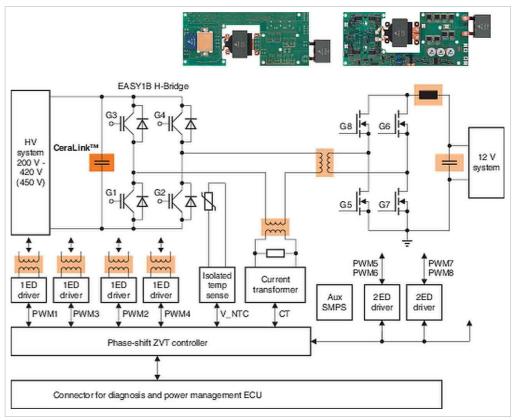

In close cooperation with EPCOS, Infineon Technologies has developed an HV/LV DC-DC demo board with an output of 2.7 kW. The requirements included a high-voltage input range from 200 to 400 V DC-depending on the HV battery used-and a lowvoltage output range from 8 to 16 V DC that is typically standard in automobile electronics systems. Furthermore, the demo board had to cover a current range of up to 200 A DC.

Table 2: Various design versions of the EPCOS CeraLink

#### Figure 1: Infineon EASY 2.7 kW inverter

Nearly 100 EPCOS and TDK components Various types of circuit topologies are available on

the DC-DC converter market. However, the most widely used is the full-bridge circuit with a ZVT (zero-voltage transition) based

| Component                                                                              |       | Q |

|----------------------------------------------------------------------------------------|-------|---|

| CeraLink with 20 µF for 400 V DC                                                       | EPCOS |   |

| Aluminum electrolytic capacitors                                                       | EPCOS |   |

| MLCCs                                                                                  | TDK   |   |

| SMT power inductors                                                                    | EPCOS |   |

| PCEM T7921 power choke from the Electromobility<br>Platform with peak current of 225 A | EPCOS |   |

| PTEM T6973 power transformer from the<br>Electromobility Platform                      | EPCOS |   |

| GTEM T7509 gate drive transformer from the<br>Electromobility Platform                 | EPCOS |   |

| CTEM T7078 current sense transformer from the<br>Electromobility Platform              | EPCOS |   |

|                                                                                        |       |   |

Table 3: EPCOS and TDK components for fast-switching IGBTs from Infineon Technologies

| uantity |

|---------|

| 1       |

| 3       |

| 80      |

| 7       |

| 1       |

| 1       |

| 4       |

| 1       |

|         |

per volume, low ESL and ESR values, and a minimum leakage current, and thus satisfies all the requirements of high-speed IGBT modules or MOSFETs. This system configuration also permits control of high current change rates (di/dt) of up to 10 kA/ $\mu$ s. Despite these extremely high potential rates, the generated voltage peaks (V = Ldi/dt) are extremely low thanks to the low ESL of the CeraLink.

The capacitor is not the only source of parasitic inductance. Noticeable stray inductances occur in a normal system configuration for several reasons, including the contacting inside the IGBT module and the feed

on MOSFET transistors.

Infineon Technologies has redesigned these circuits with various EPCOS components and adapted them to its EASY series of fast-switching IGBTs (figure 1). They employ a large number of diverse EPCOS and TDK components (Table 3).

The EPCOS CeraLink combines high capacitance

line to the capacitor. The EPCOS CeraLink allows for dramatic reduction in the parasiticinductance values for the feed line-to the same extent as the values for the capacitor itself, thanks to its compact design.

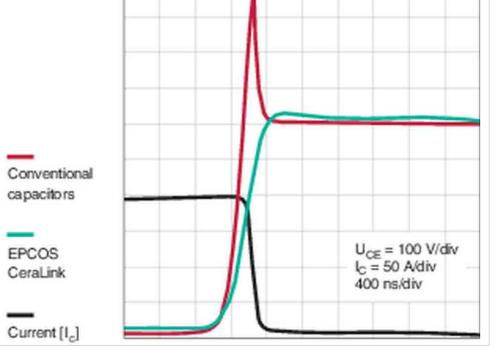

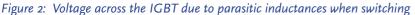

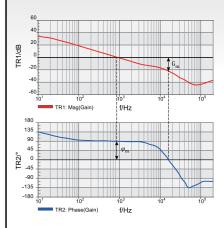

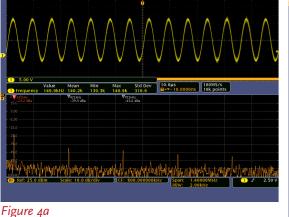

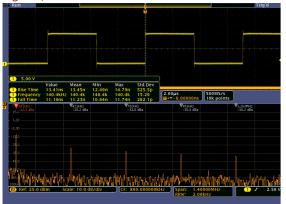

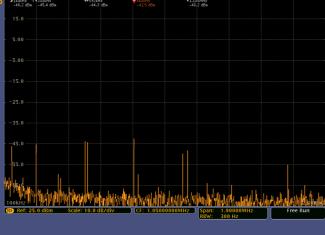

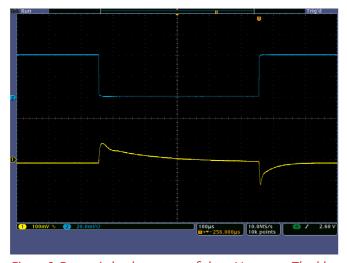

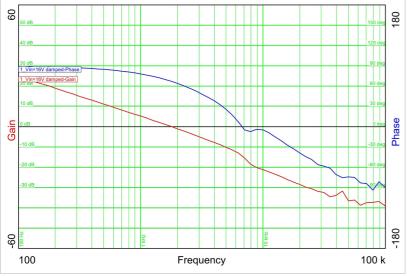

The compact link to the IGBT module simultaneously attenuates its over voltages, and a snubber capacitor is usually not necessary. Figure 2 shows the voltage curve at turn-off of the IGBTs with and without an EPCOS CeraLink. The voltage

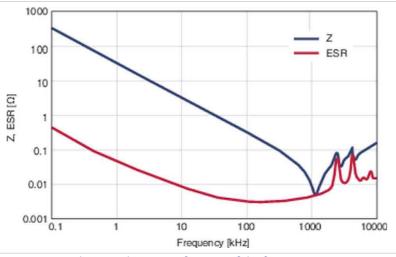

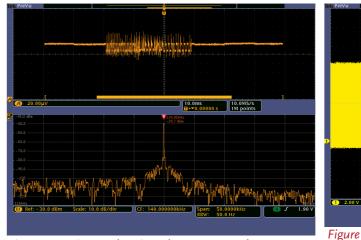

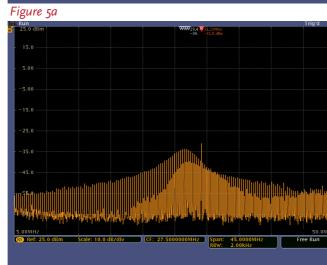

rise is thus only minimal and is within the safe range for the IGBTs. In this case, the switching frequency is 100 kHz, meaning the capacitor sees a ripple-current frequency of 200 kHz. Figure 3 shows the impedance and ESR curves as a function of the frequency.

Thanks to its very low ESR values, the **EPCOS** CeraLink

attenuates the overvoltage peaks very effectively. As a rule, therefore, additional snubber capacitors are not necessary.

Although the capacitance of the EPCOS CeraLink is usually sufficient for pure DC-DC applications, it may be too low for motor operation, for example. This can be remedied by connecting aluminum electrolytic or film capacitors in parallel, as their high capacitance carries the low-frequency current component. The EPCOS CeraLink then handles the high-frequency component, including the snubber component.

www.epcos.com

POWER OVER ETHERNET

## 90-W plug-n-play Power over Ethernet over 100-m CAT-5e cable

Proprietary PoE extension is fully backward compatible

By: Alison Steer, Product Marketing Manager, Mixed-Signal Products, Linear Technology

oE (Power over Ethernet) has been increasing in popularity due to its flexible and cost-effective method of delivering both power and data over a single Ethernet cable. This allows equipment to be installed almost anywhere without the constraint of AC-power proximity or requiring installation by an electrician.

The original IEEE 802.3af PoE specification limited the power delivered to the powered device to just 13 W, which in turn limited

the scope of applications to devices such as IP phones and basic security cameras. In 2009, the IEEE 802.3at specification increased this available power to 25.5 W. However, this was still not enough to satisfy the growing number of power hungry PoE applications, such as picocells, wireless access points, LED signage, and heated PTZ (pantilt-zoom) outdoor cameras.

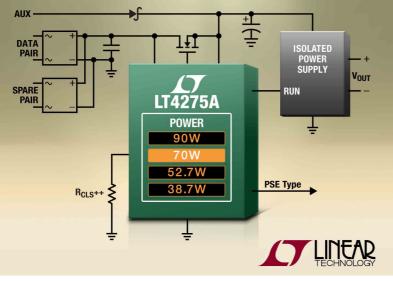

In 2011 Linear Technology released a new proprietary standard, LTPoE++, which extends the PoE and

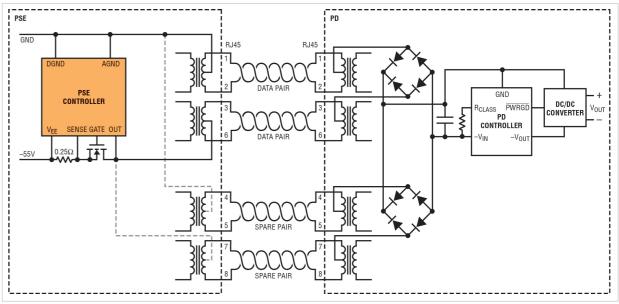

Figure 1: A typical PoE system

PoE+ specifications to 90 W of delivered power, while maintaining 100% interoperability with the IEEE PoE standards. LTPoE++ provides a safe and robust plug-n-play framework that dramatically reduces engineering complexity in PSEs (power-sourcing equipment) and PDs (powered devices). The benefit of LTPoE++ over other power-extending topologies is that only a single PSE and PD is required to deliver up to 90W over 4 pair CAT5e cable, resulting in significant space, cost, and development

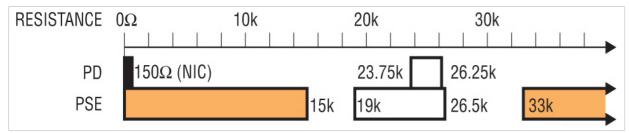

#### Figure 2: IEEE 802.3af signature-resistance ranges

time advantages (figure 1). Four different power levels are available—38.7, 52.7, 70, and 90 W—allowing system designers to size the power supply to the application's requirements.

#### **Powered-device detection**

Before a PSE can apply power to the line, it must check for an IEEEmandated signature resistance with a power-limited probing source. To be considered a valid signature, the PD must look like 25 k $\Omega$  ±5% in parallel with a capacitance of 120 nF or less. The PSE, in turn, must accept a somewhat wider range of 19 k $\Omega$ to 26.5 k $\Omega$  to account for parasitic series and parallel resistances in the system (figure 2). The PSE must reject anything below 15 k $\Omega$ or above 33 k $\Omega$ , or anything with >10 µF across its terminals.

The PD signature impedance is allowed to have a voltage offset of up to 1.9 V—typically caused by up to two diodes in series—and a current offset of up to 10 µAtypically caused by leakage in the PD. These terms complicate the PSE resistance measurement. since a single V-I point measurement will not account for these errors. As a result, the PSE is required to take at least two

different V-I points, separated by at least 1 V at the PD. It then must calculate the difference between the two points to find the true resistive slope, subtracting out voltage and current offsets. Because CAT-5 cable typically runs in ceilings, walls, and other spaces where AC wiring is also present, 50 or 60 Hz noise can be significant. Linear Technology PSE controllers handle this by using a proprietary dual-mode, four-point detection method, which ensures immunity from false positive or negative PD detection.

#### Powered-device classification

Once the PSE has successfully detected a PD, it performs the power-classification step. The PSE must keep track of how many PDs are connected and what their power-classification levels are, and stop accepting PDs when its power budget is exhausted. The PSE checks a PD's classification signature by forcing between 14.5 and 20 V across the PD and measuring the current that the PD draws. The PSE uses the measured current to classify the PD.

LTPoE++ uses a three-event classification scheme to provide mutual identification

handshaking between the PSE and PD while maintaining backward compatibility with the IEEE 802.3at standard. The LTPoE++ PSE determines if a PD is a Type 1 (PoE), Type 2 (PoE+), or LTPoE++ device by the PD response to the threeevent classification scheme. The LTPoE++ PSE also uses the three-event classification scheme result to update the ICUT and ILIM thresholds.

On the other end, the LTPoE++ PD uses the number of classification events it receives to determine whether it is receiving power from a Type 1, Type 2, or LTPoE++ PSE. If the LTPoE++ PSE measures the PD's first classification event current as a Class 0, 1, 2, or 3 device, the LTPoE++ PSE will proceed to power on the port as a Type 1 device.

Otherwise, if the PSE detects a Class 4 PD during the first classification event, the LTPoE++ PSF will continue with a second classification event, as defined in the PoE+ specification. This informs the PD that it is receiving power from either a Type 2 or LTPoE++ PSE. The absence of the second classification event

| PD input                      | Class pulse                                                  |              |              |  |  |

|-------------------------------|--------------------------------------------------------------|--------------|--------------|--|--|

| power                         | 1st Event 2nd Event                                          |              | 3rd Event    |  |  |

| 13                            | 0                                                            | -            | -            |  |  |

| 4                             | 1                                                            | -            |              |  |  |

| 7                             | 2                                                            | -            | _            |  |  |

| 13                            | 3                                                            | -            | -            |  |  |

| Invalid                       | 4                                                            | 0 to 3       | -            |  |  |

| 25.5                          | 4                                                            | 4            | 4            |  |  |

| 38.7                          | 4                                                            | 4            | 0            |  |  |

| 52.7                          | 4                                                            | 4            | 1            |  |  |

| 70                            | 4                                                            | 4            | 2            |  |  |

| 90                            | 4                                                            | 4            | 3            |  |  |

| Invalid                       | Overcurrent*                                                 | -            | -            |  |  |

| Invalid                       | 4                                                            | Overcurrent* | -            |  |  |

| Invalid                       | 4                                                            | 4            | Overcurrent* |  |  |

| *Class current I <sub>C</sub> | I <sub>CLASS</sub> exceeds that specified for an overcurrent |              |              |  |  |

Table 1

indicates the PD is receiving power from a Type 1 PSE that is limited to Type 1 power levels.

The Type 2 PD physical layer classification is defined by IEEE as two consecutive Class 4 results. The LTPoE++ PD must also display two consecutive Class 4 results in the first and second classification events.

The LTPoE++ PSE will move onto the third classification event after valid Class 4 measurements in the first and second classification events. The third classification event must result in a classification other than Class 4 to recognize the PD as LTPoE++ capable. An LTPoE++ PSE will consider a PD that maintains Class 4 during the third classification event as a Type 2 PD. The IEEE 802.3at standard requires compliant Type 2 PDs to repeat Class 4 responses for all class events.

The third classification event informs the LTPoE++ PD that it is receiving power from an LTPoE++ PSE. Table 1 shows the class-event permutations for the various PD power levels. The LTPoE++ PD presents a Class-0 through -3 classification current during the third classification event. The four different classes indicate to the LTPoE++ PSE the maximum power the LTPoE++ PD is requesting at its input. The four LTPoE++ power levels of 38.7, 52.7, 70, and 90 W at the LTPoE++ PD input correspond to the four classes, Class 0, Class 1, Class 2, and Class 3.

#### DC disconnect

Just as a PSE must only send power to valid PD, a PSE also must not leave power on after the powered device has been unplugged because a powered cable could subsequently connect to a device that doesn't expect

power. LTPoE++ uses the DC disconnect method to determine the absence of a PD based on the amount of DC current flowing from the PSE to the PD. When the current stays below a threshold IMIN—between 5 and 10 mA—for a given time tDIS— 300 to 400ms-the PSE assumes that the PD is absent and turns off the power.

#### Putting it all together

Once a PSE has successfully detected and classified a PD, it then makes the decision whether to supply power to it. If the PSE's available power is adequate to power the PD, the PSE powers on the PD and begins monitoring the port for the DC disconnect condition. The PSE now has the whole picture: The detection sequence tells it that there is a real PD attached to the port. The classification routine tells it how much power that PD will draw so it can allocate its power supply resources accordingly. Finally, the DC disconnect method tells it that the PD is still present and operating normally. The PD, in turn, has a straightforward way to communicate to the PSE what it is, how much power it wants, and whether or not it wants that power to keep flowing. All of this occurs without affecting the data stream in any way.

One important distinction with LTPoE++ is that it does not require the use of the LLDP (linklayer discovery protocol) that the IEEE mandated in its PoE+

EMPOWERING GLOBAL INNOVATION CHINA : NORTH AMERICA : EUROPE WWW.POWERSYSTEMSDESIGN.COM

### Figure 3: The LT4275 90-W PD controller uses an external MOSFET for increased power efficiency.

specification for software-level power negotiation. LLDP requires extensions to standard Ethernet stacks and can represent a significant software development effort. LTPoE++ PSEs and PDs autonomously negotiate power level requirements and capabilities at the hardware level while remaining fully compatible with LLDP-based implementations. This gives LTPoE++ system designers the choice to implement or not implement LLDP. Proprietary end-to-end systems may choose to forgo LLDP support. This creates time-to-market advantages while further reducing BOM costs, board size, and complexity.

#### LTPoE++ plug-n-play support

Linear Technology offers single, quad, octal, and 12-port LTPoE++ PSE controllers with low power dissipation, robust ESD and

cable-discharge protection, low component count, and costeffective designs. When paired with the LT4275 PD controller (figure 3), a complete plug-n-play LTPoE++ system, with no LLDP required, can deliver up to 90 W while remaining fully compatible with PoE+ and PoE standards. The entire implementation uses external low-RDS(ON) MOSFETs to drastically reduce overall PD heat dissipation and maximize power efficiency, which is important at all power levels. High absolute maximum ratings on all analog pins and cost-effective cabledischarge protection ensure the devices are safe from the most common Ethernet line surges.

www.linear.com

## It's all you need.

### The AP300 Frequency Response Analyzer

Designed for switching power supplies, it is simply the best product on the market for all of your frequency response measurement needs.

Ridley Engineering, Inc. 3547 53rd Ave W, Ste 347 Bradenton, FL 34210 US +1 941 538 6325 Ridley Engineering Europe Chemin de la Poterne Monpazier 24540 FR +33 (0)5 53 27 87 20

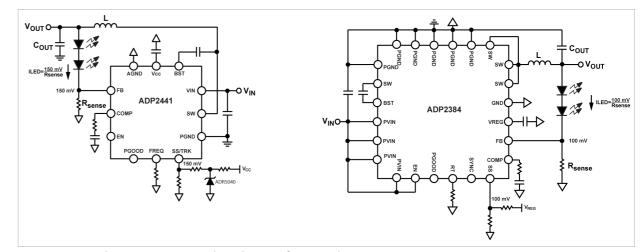

## Convert a buck regulator into a high-current LED driver

Coercing a voltage regulator to provide a constant current can extend your drive capability while maintaining low BOM cost.

#### By: Jon Kraft, Applications Engineer, Analog Devices

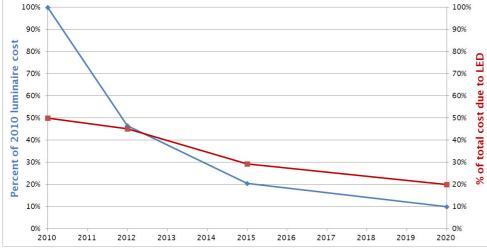

EDs promise to change the world, and few doubt that they will. However, a key limiter to more rapid adoption is the cost of the LEDs themselves. The cost breakdown of LED luminaires varies, but it is safe to put the expense of the LEDs at around 25-40% of the total luminaire cost (reference 1). Projections suggest that LEDs will continue to represent a significant fraction of the total luminaire cost for many years (figure 1).

One way to reduce the total

luminaire cost is to drive an LED at its highest possible current. If driven properly, these LEDs produce more lumens per unit cost. Doing so, however, requires higher current drivers. While there are many drivers available to operate LEDs at low currents (< 500 mA), there are fewer options at higher currents (700 mA to 4.0 A).

This is all the more surprising given that the semiconductor world is rich with DC-DC converters that can source as much as 4.0 A. The problem is that these DC-DC converters control voltages, not LED currents. Fortunately, there are some easy methods to take a readily available DC-DC buck regulator and convert it into an LED driver.

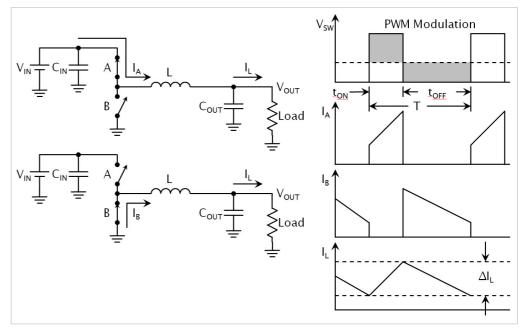

A buck regulator simply chops up an input voltage, passes it through an LC filter, and gives a stable output (figure 2). To do this, the buck employs two active elements and two passive elements. The active elements are a switch, A, from the input to the inductor and a switch, B, or

> diode from ground to the inductor. The passive elements are the inductor, L, and the output capacitor, COUT. These form an L-C filter, which reduces the ripple the active elements create.

If the switches are internal to the IC it's a regulator. otherwise it's a controller. If both

#### Figure 2: A basic buck-converter topology with waveform timing

switches are power transistors-MOSFETs or BJTs-then it's synchronous, otherwise it's called asynchronous. This gives several categories of buck circuits and each has its own merits and drawbacks. A discussion of which type to use, and all the tradeoffs, would be extensive. However, in a very general sense, the selection that often times gives an optimal efficiency, parts count, BOM cost, and board area is a synchronous buck regulator.

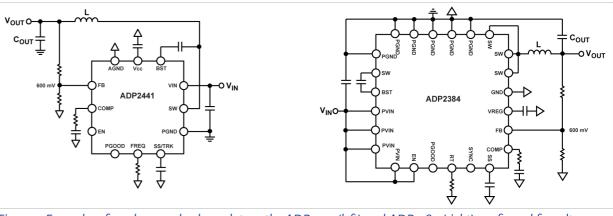

However, synchronous buck regulators for driving high current LEDs-up to 4 A-are few and expensive. An alternative is to take a standard synchronous buck regulator and modify it to regulate LED current. Here, we'll use as examples two generalpurpose synchronous buck

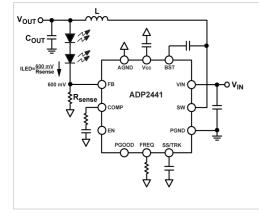

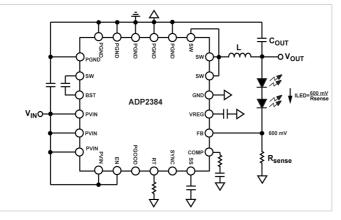

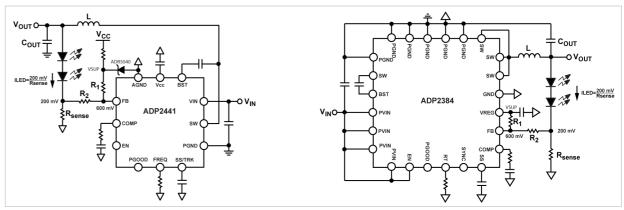

Figure 3: Examples of synchronous buck regulators, the ADP2441 (left) and ADP2384 (right) configured for voltage regulation

Figure 1: Projected relative cost of LED Luminaire and percentage due to the cost of LEDs (Source: DOE SSL 2011 Manufacturing Roadmap)

regulators from Analog Devices: the ADP2441 and the ADP2384.

The ADP2441 is a high efficiency, 36-V input synchronous buck regulator, capable of producing an output current of up to 1.2 A. The ADP2384 is another high-efficiency synchronous buck regulator,

but with an output current of up to 4.0 A, and an input voltage up to 20 V (figure 3).

For both the ADP2441 and the ADP2384, the output voltage is resistor divided down to the FB pin, compared against an internal 600-mV reference, and used to generate the proper duty cycle to the switches. In steady state, this FB pin regulates to exactly

Figure 4: A basic but inefficient LED-driver configuration

600 mV. So instead of a resistor divider, it is easy to put the LEDs there, with a resistor, RSENSE, in series to set the current (figure **4**).

Using a precision resistor from FB to GND sets the LED current to

$$I_{LED} = \frac{600 \text{ mV}}{R_{SENSE}}$$

This works nicely, but it produces a lot of power dissipation:

$$P_{diss} = 600 \text{ mV} \cdot I_{LED}$$

For low LED currents, the senseresistor dissipation is not a big issue. But at high LED currents the impact to efficiency adds significantly to the heat that the luminaire must dissipate:

#### $600 \,\mathrm{mV} \cdot 4 \,\mathrm{A} = 2.4 \,\mathrm{W}(!)$

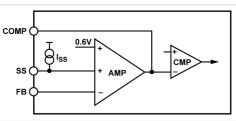

Fortunately, there are two methods to reduce the FB reference voltage for most buck regulators: use the SS (soft-start) or TRK (tracking) pin or offset the Rsense voltage.

Many general-purpose buck ICs

Figure 5: An example of soft-start or tracking pin operation

include an SS or TRK pin. The SS pin provides a controlled inductor current at startup. The TRK pin forces the buck regulator to follow an independent voltage. Often times the pins are combined into one SS/TRK pin. In most cases, the error amplifier will use the minimum of the SS, TRK, and FB\_ref voltages to change the regulation point (figure 5)

For the current purposes, we want to just set the SS/TRK pin to a fixed voltage and use it as our new FB reference. A resistor divider from a constant voltage to this pin works nicely. Many buck regulator ICs include a controlled low-voltage output, like the VREG pin on the ADP2384 or the Vcc pin of the ADP2441. For greater

accuracy, use a simple two-terminal precision reference such as the ADR5040, for example. Either way, a resistor divider from the supply to the SS/TRK pin forms the new reference (figure 6). Setting the resistor divider

to give a SS/TRK voltage around 100 to 200 mV generally offers the best compromise between power dissipation and LEDcurrent accuracy. Another benefit to setting your own feedback reference voltage is that this method can easily accommodate any sense resistor value in the standard-value series. This eliminates the expense and inaccuracy of paralleling multiple RSENSE resistors to set the LED current.

Using an SS or TRK pin accommodates many, but not all buck regulators. Some ICs do not have SS or TRK pins. Additionally, in some buck ICs, the SS pin changes the peak inductor current, not the FB reference so carefully check your

Figure 6: Using the SS/TRK pin to reduce the FB reference voltage

#### Figure 7: Offsetting the Rsense voltage buck-regulator's datasheet.

If either of these situations is the case, you can use a different method: offset the RSENSE voltage. A resistor divider tied to an accurate rail between FB and RSENSE provides a fairly constant offset voltage between RSENSE and the FB pin (figure 7).

To implement the RSENSE voltage offset, calculate the necessary values for the resistor divider: V = FR

$$R1 = R2 \frac{F_{sup} - F_{REF}}{F_{REF} - F_{REF(NEW)}}$$

So to get an effective feedback

reference, FBREF(NEW), of, say, 200 mV with R2 = 1 k $\Omega$  and VSUP = 3.0 V.

$$R1 = 1 \,\mathrm{k}\Omega \frac{3.0 \,\mathrm{V} - 0.6 \,\mathrm{V}}{0.6 \,\mathrm{V} - 0.2 \,\mathrm{V}}$$

With this arrangement, the LED current is equal to:

$$I_{LED} = \frac{FB_{REF(NE)}}{R_{SENSE}}$$

Using this method does not require a SS or TRK pin. Additionally, the FB pin will still regulate to 600 mV, but the voltage at RSENSE regulates to the FBREF(NEW) voltage. This means that other functions of the chip, such as soft start, tracking, and power-good indication

$= 6.0 \,\mathrm{k}\Omega$

W)

will still function normally.

The downside is that the accuracy of the supply can strongly influence the offset between RSENSE and FB. A precision reference like the ADR5040 has little problem. But if the supply in the above example had a  $\pm 5\%$  accuracy, it would create a ±11% variation in the LED current. A comparison appears in **table 1**.

These tips should be taken as general guidelines for implementing comprehensive LED features into a standard buck regulator. Because these features might be different

| Option 1<br>Use SS/TRK to reduce FB reference                                                                                                                                                       | Option 2<br>Offset RSENSE Voltage                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\pm 5\%$ supply voltage variation gives $\pm 5\%$ error on I <sub>LED</sub> . This is not affected by the V <sub>SENSE</sub> voltage, therefore this method has the best Rsense power dissipation. | Supply voltage variation severely<br>degrades LED accuracy. Higher V <sub>SENSE</sub><br>voltages improve this, but also increase<br>the R <sub>SENSE</sub> power dissipation. |

| P <sub>GOOD</sub> will always remain low.                                                                                                                                                           | Since FB pin still regulates to 600 mV.<br>The P <sub>GOOD</sub> pin functions normally.                                                                                       |

| By keeping the SS/TRK pin lower than<br>normal, some fault modes may not work<br>properly.                                                                                                          | All fault modes work normally                                                                                                                                                  |

Table 1: Comparison of two methods to reduce RSENSE power dissipation

from the intended application for the buck IC, however, it is always best to contact the semiconductor manufacturer to ensure that the IC can be used as described here.

www.analog.com

**References:**

- 1. SSL 2011 manufacturing roadmap, US Department of En-

- **Payton Planar Transformers**

Let PAYTON PLANAR MAGNETICS "Power Your World" with our state-of-the-art planar and conventional magnetics. Our cost is affordable and similar to wound tics. Full engineering design capabilities allow you to specify 10 to 20,000 watts, from industrial / telecom / automotive to space applications.

1805 S. POWERLINE ROAD • SUITE 109 • DEERFIELD BEACH, FL 33442 USA Tel: (954) 428-3326 x203 • Fax: (954) 428-3308 • jim@paytongroup.com

2. Marasco, Ken, How to apply DC-to-DC step-down (Buck) regulators successfully, Analog Dialogue, June 2011

ergy, http://www.ssl.energy.gov

## Flash corruption: software bug or supply-voltage fault?

#### Answer: Both!

#### By: Shyam Chandra, Lattice Semiconductor

mbedded systems commonly use Flash memory to store firmware. Occasionally, the firmware stored in the Flash memory in some systems is accidentally corrupted, preventing the system from booting up after powering on. Flash corruption is commonly associated with a software bug.

However, it is also commonly understood that the probability of Flash corruption increases either during power-cycling tests or during margining tests. The Flash corruption problem tends to be more severe when the number of complex ASICs or SOCs a board uses increases. Fortunately, methods exist to minimize occurrences of Flash corruption that are *not* due to software faults.

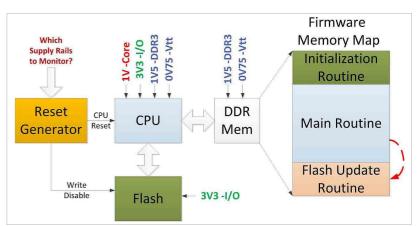

#### Flash memory corruption

Figure 1 illustrates a typical circuit board's CPU circuitry. When the power turns on, the reset generator first activates the CPU reset signal. It then waits until the power to the CPU, the Flash memory, and the DDR memory each reaches its correct

Figure 1: Typical CPU section and firmware memory map level, waits for an additional extended period of time—about 150 ms—and then deactivates the CPU reset signal. When the reset signal deactivates, the CPU begins to execute the initialization routine in the Flash memory, transfers the contents of the firmware stored in the Flash memory into the DDR memory and then executes the program from the DDR memory.

The procedure to load firmware into the Flash memory is: (1) Firmware is downloaded into the DDR memory through a communication interface. (2) Jump to the Flash-update routine to reprogram the Flash with the new firmware. (3) Power to the processor is recycled and the

new firmware takes effect.

An event that causes the code execution to jump inadvertently to the Flash-update routine can corrupt the Flash memory contents. When the board power is cycled, the corrupt version of the code is loaded into the DDR and the board does not function as expected.

The code execution could jump to this Flash-update routine inadvertently due either to a software bug or to a faulty supply voltage rail (during the poweroff event, for example). Normal debugging methods can detect a software bug. However, a faulty power supply voltage is hard to detect, as the supply voltage

error can occur anywhere.

#### Supply-fault-induced execution jumps

All ICs have both minimum and maximum operating voltage specifications. If the system exceeds an IC's maximum voltage specification, damage to the device results. If the supply drops below the minimum supply level, the device no longer operates as specified.

For example, the core-voltage specification of the CPU in figure 1 is 1.2 V  $\pm$ 5%. If the voltage drops below this level, the ability of the CPU's internal instruction execution pipeline to reliably transfer instructions and data is compromised and depending on the CPU's process and operating temperature the instruction can incorrectly execute.

As an example, a move instruction could execute as a pop instruction, and the code execution then jumps to a random memory location determined by the contents of the stack. Depending on the contents of that memory location and the error in execution, the processor can either hang or jump to the Flash-update routine, corrupting the Flash memory and overwriting the Flash memory contents.

A droop in DDR memory voltage or threshold voltage also introduces errors in the

instructions and data transferred between the memory and CPU. This erroneous code execution can also cause a jump to the Flash-update routine, corrupting Flash memory.

#### Supply-voltage droop

The power-supply voltage droop can occur for either of the two following reasons.

Card power down: When the power to the board turns off, not all supplies on the board turn off at the same time because the turn off rate depends on a number of parameters including the supply capacity, load, and supply-output capacitance. Because the power-supply turn-off slew rate is slow in comparison to the processor's instruction execution speed, the processor can experience a supply fault, causing it to misexecute instructions before the supply is fully off or before its reset signal activates.

#### Momentary ground-voltage

rise: The power consumption of some processors can fluctuate dynamically, depending on the executing instructions. When such changes occur, the device draws large amounts of current for brief periods from the power source, and dumps these into the ground. As a result, the supply voltage can momentarily droop and the ground voltage may increase. The duration of such a condition depends on the inductance of the supply path.

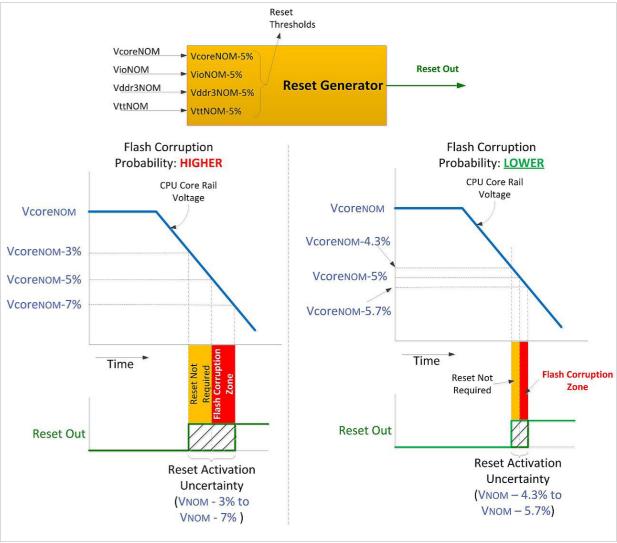

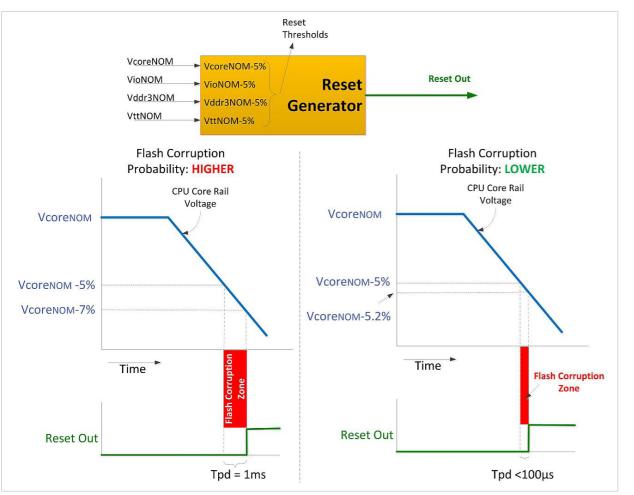

#### Minimizing corruption

The probability of Flash corruption can be minimized by activating the CPU reset when any supply rail drops below its threshold level. This prevents code execution under faulty power supply conditions.

The reset generator activates both the CPU-reset signal as well as the write-protection signal to the Flash memory. In some cases, the reset generator output does not apply directly to the CPU. Instead, it connects to a CPLD, which executes a reset-distribution algorithm. In such cases, the write-protection signal for the Flash should be set because the CPU may not reset as soon as the powersupply voltage becomes faulty. The reset generator IC in figure 1 monitors all CPU rails-1 .0, 3.3, 1.5, and 0.75 V—and activates the reset signal and Flash writeprotect signals when any one of them drops below their operating threshold levels.

#### Selecting a reset generator

The criteria for selecting a reset IC include the number of voltagemonitor inputs, glitch filtering, hysteresis, fault-detection accuracy (across the operatingtemperature and -voltage ranges), and fault-detection speed.

#### Number of voltage-monitor

inputs: The reset-generator IC must monitor all CPU voltage rails for faults-voltage excursions below corresponding operating threshold levels. In the case of figure 1, four inputs are required with thresholds set at 5% below the nominal operating voltage levels. For example, Lattice power management ICs support six to 12 voltage-railmonitor inputs, and the reset generation threshold levels can be programmed from -0.5% to -20%.

#### Errors to avoid: Some designs

use a single-rail reset generator that usually monitors only, for example, 3.3 V. This will not be sufficient, because the 3.3V rail may turn off at a different rate than the core voltage or the DDR voltage.

This arrangement could work only if all critical loads used the 3.3 V as their input supply. In most circuit boards, however, the power supply for the core and DDR use different input-voltage

Figure 2: Flash corruption probability vs. reset-generator accuracy

#### POWER SYSTEMS DESIGN JANUARY/FEBRUARY 2013

sources due to power dissipation, and so reset generation using only 3.3V cannot avoid Flash corruption. The same argument holds if the reset generator monitors only the core supply rail.

Glitch filtering: When the reset generator has single-ended, as opposed to differential, sensing of voltage rails, differences in the ground voltage between the reset IC and the CPU memory can genCOMPUTING

#### Figure 3: Flash corruption probability vs. reset-generator fault-detection speed

erate false reset signals. To make sure that the reset is actually due to a fault in the supply voltage and not a momentary ground voltage difference, reset ICs include glitch filters. For example, when their input glitch filters are enabled, Lattice power-management ICs ensure that the fault persists for 64 microseconds before activating the reset signal.

Reset generators using ADCs and microcontrollers to monitor voltages implement ADC sampleaveraging algorithms to eliminate the effects of glitches, resulting

in false reset activation. The averaging algorithm derives the actual ADC voltage by calculating the average of four ADC voltage samples.

Hysteresis: Most voltage rails source from switched-mode power supplies. The output of these supplies usually contain ripple. This ripple can cause a reset signal glitch when the supply level is close to the reset threshold. To avoid this, reset generators must have hysteresis voltage levels ranging from 0.5% to 1% of the voltage monitored.

Reset generators using ADC and microcontrollers to monitor voltages should implement hysteresis in software to prevent glitches in the reset output.