November 2012

Power Systems Design: Empowering Global Innovation

Special Report: Communication, Data, and Computing (pg37)

# Charge **BIG** Batteries Fast

#### High Voltage, High Current, High Efficiency Charger

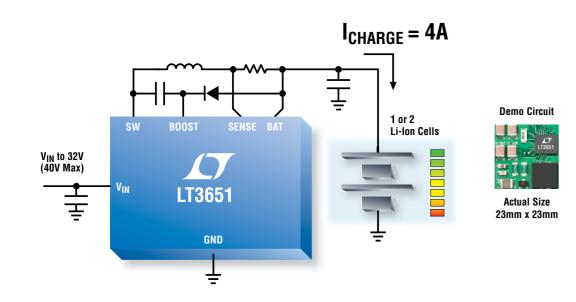

The LT<sup>\*</sup>3651 enables fast charging of Li-Ion/Polymer batteries by delivering up to 4A of continuous charge current with minimal power loss. This is due to its high efficiency switchmode topology, including on-chip synchronous MOSFETs. Its autonomous operation means no microcontroller is necessary and the device integrates an onboard C/10 or timer charge termination. The LT3651's programmable input current limit with PowerPath™ control regulates charge current to maintain a constant supply current, preventing the input supply from collapsing.

#### **Features**

- Charge Current up to 4A

- Wide Input Voltage Range: 4.8V to 32V (40V Max)

- Programmable Switching Frequency: 200kHz to 1MHz

- C/10 or Timer Onboard Charge Termination

- High Efficiency Operation Minimizes Power Loss

- Programmable Input Current Limit

- Compact 5mm x 6mm QFN Package

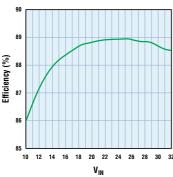

#### Efficiency vs V<sub>IN</sub>

[J], LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PowerPath is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

Europe Sales offices: France 33-1-41079555 Italy 39-02-38093656 Germany 49-89-9624550 Sweden 46-8-623-1600 UK 44-1628-477066 Finland 358-9-88733699 Distributors: Belguin ACAL 32-0-2-705983 Finland Tech Data 338-9-88733382 France Arrow Electronique 33-1-49-784978, Tekelec Airtronic 33-1-56302425 Germany Insight 49-89-611080,

Setron 49-531-80980 Ireland MEMEC 353-61-411842 Israel Avnet Components 972-9-778-0351 Italy Silverstar 39-02-66125-1 Netherlands ACAI.31-0-402502602 Spain Arrow 34-91-304-3040 Turkey Arrow Elektronik 90-216-6465090 UK Arrow Electronics 44-1234-791719, Insight Memce 44-1296-330061

#### WWW.POWERSYSTEMSDESIGN.COM

Visit us online for exclusive content; Industry News, Products, Reviews, and full PSD archives and back issues

#### **VIEW**point

Power Design

Things of the internet are power players too By Gail Purvis, Europe Editor, Power Systems Design

**POWER**line

Murata introduces new power supplies with medical approvals

**POWER**player

DBV architecture saves power in datacenters By Patrick Le Fèvre, Ericsson

#### MARKETwatch

Power products a big piece of the data center infrastructure pie By Jason dePreaux, IMS Research

**DESIGN**tips

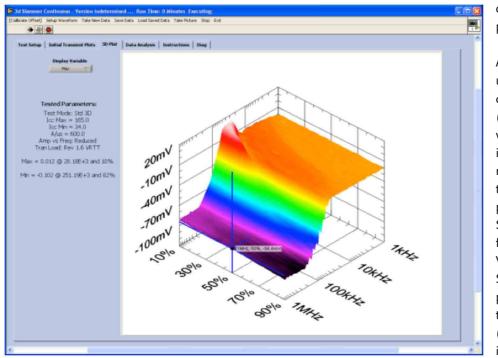

Input impedance measurements and filter interactions: Part II By Dr. Ray Ridley, Ridley Engineering

#### COVER STORY

<sup>14</sup> Higher power, smaller, and cooler

By Eddie Beville and Afshin Odabaee, Linear Technology

#### **TECHNICAL FEATURES**

#### Power Devices

Making the switch to silicon carbide By Bob Callanan and Julius Rice, Cree

#### Designing a DiSEqC-antenna phantom power supply By Andrea Longobardi, Maxim Integrated

Thermal Design

Thermal design considerations for thin power MOSFETs By Ralf Walter, Infineon Technologies AG

#### Communication

New technology and acquisitions benefit wireless sensing By Harry Forbes, ARC Advisory Group

#### R&D

IEDM, where the device is king By Gail Purvis, Europe Editor, Power Systems Design

#### SPECIAL REPORT: COMMUNICATION, DATA,

AND COMPUTING

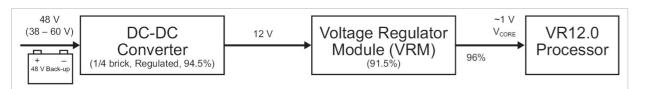

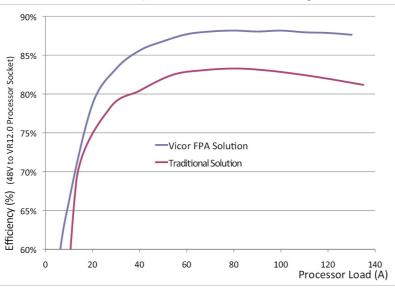

#### Direct 48 V to Intel VR12.0 **DC-DC** conversion

By Stephen Oliver, Vicor

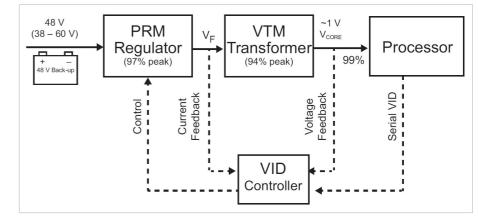

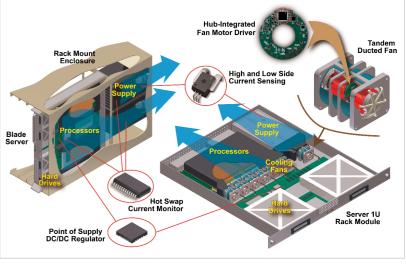

#### Improve server efficiency with

#### advanced control electronics

and Thomas Rowan. Allegro MicroSystems

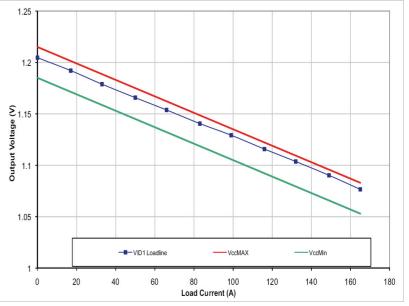

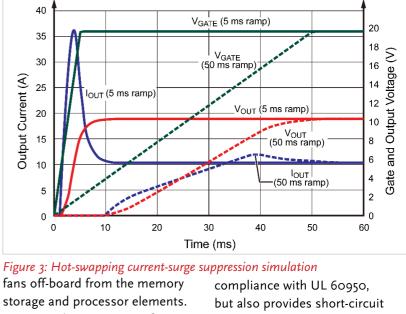

#### Voltage mode versus peak-

### current mode

By Milan Marjanovic, Texas Instruments

#### By Mark Gaboriault, Alexander Latham

#### POWER SYSTEMS DESIGN NOVEMBER 2012

Higher power, smaller, and cooler PoL **DC-DC** regulation

Title (pg 14)

Highlighted Products News, Industry News and more web-only content, to: www.powersystemsdesign.com

SPOTLIGHT on Power Technology

By David G. Morrison, Editor, How2Power.com

#### GREENpage

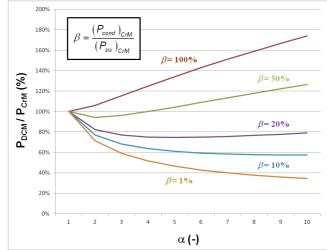

single-phase PFC stages

Software security urged for medical devices and networks By Gail Purvis, Europe Editor, Power Systems Design

AGS Media Group 146 Charles Street Annapolis, MD 21401 USATel: +410.295.0177 Fax: +510.217.3608 www.powersystemsdesign.com

#### Editor-in-Chief

Joshua Israelsohn, Editor-in-Chief, Power Systems Design joshua@powersystemsdesign.com

#### **Contributing Editors**

Gail Purvis, European Editor, Power Systems Design Gail.Purvis@powersystemsdesign.com

Liu Hong, Editor-in-Chief, Power Systems Design China powersdc@126.com

Ash Sharma, IMS Research Ash.sharma@imsresearch.com

Dr. Ray Ridley, Ridley Engineering RRidley@ridleyengineerng.com

David Morrison, How2Power david@how2power.com

#### **Publishing Director**

lim Graham jim.graham@powersystemsdesign.com

#### Publisher

Julia Stocks Julia.stocks@powersystemsdesign.com

#### **Circulation Management**

Kathryn Philips kathryn.phillips@powersystemsdesign.com

Magazine Design Louis C. Geiger

louis@agencyofrecord.com

#### **Production Manager**

Chris Corneal chris.corneal@powersystemsdesign.com

Registration of copyright: January 2004 ISSN number: 1613-6365

AGS Media Group and Power Systems Design Europe magazine assume and hereby disclaim any liability to any person for any loss or damage by errors or ommissions in the material contained herein regardless of whether such errors result from negligence, accident or any other cause whatsoever.Send address changes to: circulation@powersystemsdesign.comFree Magazine Subscriptions,

go to: www.powersystemsdesign.com

Volume 9, Issue 9

## Things of the Internet are power players too

One of the more intriguing approaches to the increasing intertwine of IT and electronics is being undertaken by Finland's VTT Technical Research Centre which together with its Japanese partner, the University of Tokyo, is developing uID or a universal identification technology.

Research Professor, Heikki Ailisto says this will enable the identification and tracking of individual products, components, and food items that will allow the information on origin, manufacture and history to be attached to the most commonplace items over their entire life cycle. A timber plank, for instance, can be tagged with information on which forest the timber was cut from, where it was sawn, how many times it has been painted, and with what paints."

Ailisto says that the Internet of Things (IoT) is the third of identifiably big telecommunication waves. The phone connected 500 million places. The mobile phone connects 5 billion people. IoT will connect 50 billion devices, machines and objects. Objects do not require an actual data connection, but can be named and connected to background systems, with identifiers.

Ubiquitous computing and the IoT will revolutionise technology and business and VTT has been developing its ubiquitous computing applications and basic technology in the OPENS (Open Smart Spaces) programme. The achievements to date include the implementation of interoperability platform Smart M3, which enables various appliances and objects in the home or office to converse, understand each other, and share information.

US technology research consultancy, Gartner, has recently named its top 10 strategic technologies for organisations in 2013, ranking IoT the 5th slot. It is preceded by after the mobile device battles and the need to support a variety of form factors with Windows 8, Google' Android, and Apple iOS; more Web apps as HTML5 becomes capable with enterprises facing complex app stores models in turn delivering mobile apps through their own private application stores, and providing an apptrepreneurs support ecosystems.

The PC (personal cloud) is becoming the location of choice for individual personal content and how consumers will connect with the numerous web of devices they choose to use during different aspects of their daily lives.

And of course the Cloud is an essential element for IoT, which Gartner simply sees as enabling a wide range of new applications and services, while raising many new challenges. Mobile, points out Gartner, no longer refers only to cellular handsets or tablets but is being embedded among things, as in pharmaceutical containers and automobiles.

Objects like smart meters, now communicate via NFC, Bluetooth, LE, and Wi-Fi to a wide range of devices and peripherals, such as wristwatch displays, healthcare sensors, smart posters, smart shirts and clothing, as well as home entertainment systems.

The IoT is a power player and an enabler, offering a wide range of new applications and services, but in turn raising many new challenges.

#### Gail Purvis

Europe Editor

Power Systems Design

#### 2SP0115T Gate Driver

Unleash the full power of your converter design using the new 2SP0115T Plug-and-Play driver. With its direct paralleling capability, the scalability of your design into highest power ratings is unlimited. Rugged SCALE-2 technology enables the complete driver functionality on a single PCB board, exactly fitting the size of 17mm dual modules. Combined with the CONCEPT advanced active clamping function, the electrical performance of the IGBT can be fully exploited while keeping the SOA of the IGBT. Needless to say that the high integration level provides the best possible reliability by a minimzed number of components.

### ONCEPTINTELLIGENT POWER ELECTRONICS

# Unleash **Sheer Power!**

SAMPLES AVAILABLE!

#### Features

Plug-and-Play solution 1W output power 15A gate current <100ns delay time ± 4ns jitter Advanced active clamping Direct- and halfbridge mode Direct paralleling capability 2-level and multilevel topologies DIC-20 electrical interface Safe isolation to EN50178 UL compliant

#### www.IGBT-Driver.com

# Murata introduces new power supplies with medical approvals

urata has introduced the MVAC series of highly efficient, 3" x 5" open frame AC-DC power supplies from Murata Power Solutions. Suitable for use in a wide variety of industrial factory automation, communications, and medical equipment, the series comprises two single output models, the 250-W MVAC250 and the 400-W MVAC400 units.

Both models accommodate the universal AC input voltage range from 90 to 264 V AC with active PFC (power factor correction) and active inrush-current control. Each model is available with a nominal output voltage of 12, 24, or 50 V DC. In addition, a 12-V-DC 1-A fan supply and an auxiliary 5-V-DC 2-A output are provided across the range.

With typical efficiency ratings of 94%, Murata Power Solutions packages the units in an industry standard 1U open frame format measuring just 127.00 x 76.20 x 35.56 mm (5 x 3 x 1.4 inches). These low-profile power converters have significantly better convection-cooled performance

characteristics than other competing designs. The MVAC250 can deliver up to 170-W output and the MVAC400 up to 250-W without the need for any forced airflow.

With their high convectioncooled ratings, the use of the MVAC series allows OEMs to eliminate the fan and fan controllers in their traditional power designs. In addition to the cost savings, removing cooling fans also allows designers to increase their product MTBF while decreasing system noise.

The MVAC250 and the MVAC400 comply with the third edition of UL60601-1—the harmonized standard for medical electrical equipment recognized by publichealth authorities in most countries—making them suitable for use in medical applications in multiple geographies. The units also meet the IEC60950/ UL60950 safety specifications and EN55022 standard for conducted emissions.

Each power supply is suited for

*The MVAC250 and the MVAC400 comply with the* UL60601-1 3<sup>rd</sup>-edition medical safety standard, the IEC60950/UL60950 safety specifications, and EN55022 standard for conducted emissions.

use in a broad range of operating temperature environments. They are capable of operating on full power from -10 to +50 °C with a start-up temperature down to -20 °C and derated operation up to 70 °C.

Protection features include over voltage, over current, and over temperature. A remote-sense input and power OK signal are provided across the range. Optional droop current sharing allows multiple supplies to operate in parallel.

With lead-times of stock to 12 weeks, pricing at 1,000-pcs for MVAC400 series products is approximately \$130.00 per unit, while pricing for MVAC250 units depending on the model ranges from approximately \$102.00.

www.murata-ps.com

# Powerex SCRs & Diodes Have What It Takes for Your Low & Medium Voltage Application

LIABILIT

ш

RTI

ш

d X

11

- Reliable supply chain with strategically facilities – USA & Tangiers, Morocco

- 40 years of experience in the manufacture of power semiconductor solutions

- Commitment to future innovation through investment in research and design

- Experienced applications engineers, serving as an extension to your design team

- Global network of experienced manufacturer sales representatives & authorized distributors

For further information, contact Kelly Bandieramonte kbandieramonte@pwrx.com (Please type "PSD-Europe" in your subject line.)

located manufacturing

Power Semiconductor Solutions 001 724-925-7272 www.pwrx.com

# **DBV** architecture saves power in datacenters

By: Patrick Le Fèvre, Marketing and Communication Director, Ericsson

he increasing demand for more internet services and cloud computing is driving both the expansion and building of new datacenters around the world. A key challenge for operators is the minimization of energy expenditure at the board level.

A significant aid to this process is the use of advanced DBV (dynamic-bus-voltage) architectures. Advanced boardpower-consumption monitoring and control technologies enable significant energy savings at the board level.

Static bus goes dynamic Today, the standard power architecture increasingly being used is the IBA (intermediate-bus architecture), which uses IBCs (intermediate-bus converters) to convert a traditional 48-V-DC distribution-level power line used in telecoms typically to a static 12 V DC. This first down-conversion 12-V level feeds a number of POL (point-of-load) DC-DC regulators, which supply the final load voltages at a chip's logic supply levels of 3 V or below.

The choice of 12 V DC has been

made to ensure a high enough voltage to deliver all the power required by the board, or load, in times of high data traffic. However, this approach becomes highly inefficient when the traffic demand is low.

The DBV architecture is an evolution of the IBA and provides the possibility to adjust dynamically the power envelope to meet load conditions. It achieves this by adjusting the intermediate bus voltage, previously the 12-V-DC fixed bus voltage. As implemented by Ericsson, the DBV architecture accomplishes this through the use of advanced digital power control and optimized hardware combined with an energyoptimizer series of algorithms. This can lead to reductions in both energy consumption and power dissipation, which in turn contributes to a reduction in the amount of cooling that is required.

DBV is a technology that makes possible to reduce board power consumption from anywhere between 3% and 10%, depending on the board application. The potential for energy saving is a

very substantial one, especially when taking into account the fact that 1 W saved at the board level can result in a 3 W saving at the power grid level.

Advanced DBV Conversion Technology Converters for the DBV architecture can be adjusted within an operation range of 13.0 to 8.2 V and adjusted further down to 4 V to power below-5-V sleep modes, which today requires an extra power-module. The energy optimizer not only optimizes switching parameters to reduce energy consumption, but also offers features including the ability to handle input voltage transients with slew-rates up to 0.5 V/ $\mu$ s, while keeping the output voltage within  $\pm 10\%$ . This ensures that the output voltage does not trigger over-voltage protection. It also very efficiently manages pre-bias start-up operation and shut down is fully controlled avoiding voltage spikes that cause avalanche conditions in the secondaryside synchronous rectification MOSFET, making a contribution to further improve reliability.

www.ericsson.com

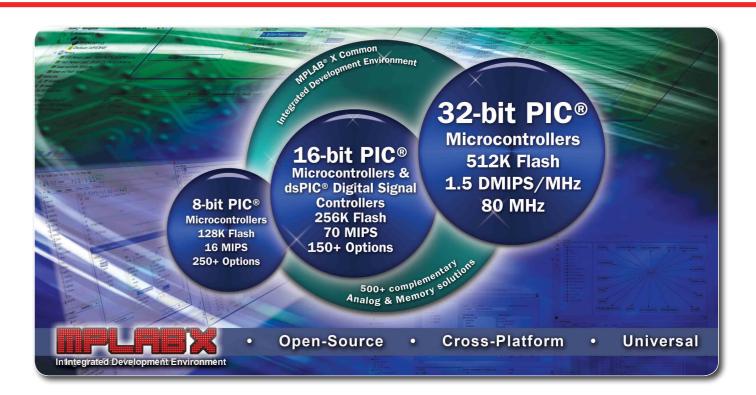

## One platform for 8-, 16- and 32-bit development - with Microchip's MPLAB® X IDE

MPLAB® X IDE is the free, integrated toolset for all of Microchip's 900+ 8-, 16- and 32-bit PIC<sup>®</sup> Microcontrollers, dsPIC<sup>®</sup> Digital Signal Controllers, and memory devices. Based on the open-source NetBeans platform, MPLAB X runs on Windows® OS, MAC® OS and Linux, supports many third-party tools, and is compatible with many NetBeans plug-ins.

MPLAB XC compilers help increase code speed of any PIC® Microcontroller or dsPIC<sup>®</sup> digital signal controller by 30%, whilst also cutting code size by 35%. These new compilers give designers the choice of Free, Standard or Pro code optimisation levels for 8-bit, 16- or 32-bit development, or a single C compiler suite to support all Microchip Microcontrollers and digital signal controllers.

Microchip's tool chain of compatible compilers and debugger/programmers operate seamlessly within the universal, cross platform and open-source MPLAB® X integrated development environment, reducing both learning curves and tool investments.

#### Evaluate MPLAB X today! www.microchip.com/get/eumplabx

#### Microcontrollers • Digital Signal Controllers • Analog • Memory • Wireless

#### **START DEVELOPING TODAY**

Download a free copy of MPLAB X and choose from a choice of new C compilers:

- MPLAB XC8 for 8-bit MCUs

- MPLAB XC16 for 16-bit MCUs and DSCs

- MPLAB XC32 for 32-bit MCUs

- MPLAB XC Suite for all 900+ PIC MCUs and dsPIC DSCs.

Renewables

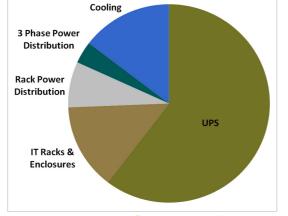

# Power products a big piece of the data-center infrastructure pie

By: Jason dePreaux, Associate Director, IMS Research, IHS

n a recent report, Data Center Infrastructure Yearbook, IMS Research forecast that the market for power and cooling products supporting data centers will grow to more than \$15 billion by 2014. Power backup and distribution equipment will comprise over 2/3 of this figure.

Fastest growth is forecast for products that improve datacenter efficiency. For example, the need to monitor electricity use is reshaping the power-distribution market with intelligent hardware, which commands higher prices than do their dumb counterparts. Cooling equipment is changing to cope with high-density computing environments. Even enclosures are evolving to facilitate increased airflow and power cabling.

In power, one of the biggest shifts is in rack-level power distribution. Traditionally an afterthought, the trend has been to bring monitoring and switching to these products. PUE (power-usage effectiveness) is becoming a ubiquitous, if not somewhat flawed, metric to compare total data-center power use to server power. Deploying intelligent rack PDU help datacenter managers get a better handle on their PUEand what they can do to lower it.

Single-phase units make up more than half of the UPS market. At the large end, static UPS modules are creeping up above 1 MVA to satisfy growing power demands. Transformerless UPSs

using IGBTs now account for more revenues than SCR-based units do. These new UPSs offer better efficiency, especially under partial load, where UPSs spend most of their lives.

Future growth in the data-centerinfrastructure market will be a balance between opposing forces (figure 1): Digitization continues unabated. Mobile data, electronic health records, and internet connectivity drive data-processing and storage needs, demanding more data centers. However, new servers offer greater efficiency, which reduces the need for additional infrastructure. Today, economic conditions often serve as tiebreaker. The cloudy economic picture

Figure 1: Data Center Infrastructure Market: Revenue Breakdown—2014 (Source: IMS Research) dampens companies' willingness to spend on capital-intensive projects like data centers.

> Still, big multinationals are expanding their reach into datacenter products and services. Over the past five years, three vendors have consolidated their positions by acquisition. Schneider Electric, Emerson, and Eaton combined to hold 47% of the 2011 data-centerinfrastructure market. These big *three* have each made multiple acquisitions to enhance product portfolios and extend geographic reach. Beyond this are hundreds of vendors with smaller niches around the world.

www.imsresearch.com

World's Most Powerful 1700V Dual IGBT Module for High Power

# **Energy Conversion**

for a greener tomorrow

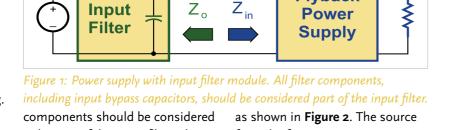

# Input impedance measurements and filter interactions: Part II

By: Dr. Ray Ridley, President, Ridley Engineering

#### ntroduction

In this article, Dr. Ridley continues the discussion of power supplies with input filters. He shows how the output impedance of the input filter is measured, and demonstrates the importance of input filter damping.

#### Input Filter Measurements

As discussed in the last article of this series [1], an input impedance measurement gives information about the characteristics of the power supply's input terminals. We use this information in conjunction with measurements of the output impedance of the input filter to assess whether a system interaction is likely to occur. This is important since it can lead to instability of the power supply control loop.

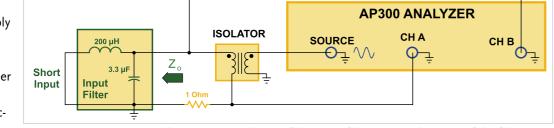

**Figure 1** shows a block diagram of

a switching power supply connected to an input filter. In order to assess filter interactions correctly, all filter

Z

to be part of the input filter. This includes any bypass capacitors at the input of the switching power supply, and any other filter components that may be included at the front end of the power supply. In the last article of this series [1], the measurement of the input impedance of the power supply was demonstrated, and the effect of a small bypass capacitor was shown.

Input

In this article, the techniques for measuring the input filter itself are presented. The output impedance of the filter can be measured from the frequency response analyzer is isolated through a wideband transformer [2], and connected to the input filter in series with a current-sense resistor. If a 1-ohm resistor is used, no scaling is needed on the gain-phase measurement from the analyzer to convert to impedance values.

**Flyback**

The node between the sense resistor and the filter under test is connected to a ground reference. Channel A of the analyzer measures the voltage across the resistor (current signal) and Channel B

Figure 2: How to measure the output impedance of the input filter. Notice the input of the filter must be shorted for a proper measurement.

# the world needs innovative electronics. they are on display here.

25th International Trade Fair for Electronic Components, Systems and Applications Messe München November 13–16, 2012 www.electronica.de

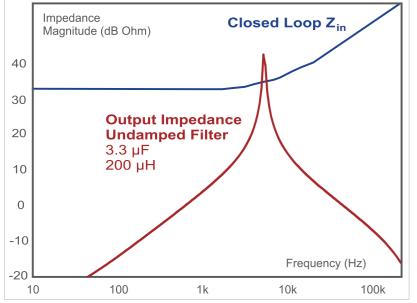

Figure 3: Comparison of measurements of power supply input impedance and input filter output impedance. With an undamped filter, the output impedance exceeds the input impedance of the power supply.

measures the voltage across the filter (voltage signal). The ratio B/ A of these two test signals gives the impedance of the input filter.

Notice that a short-circuit is placed across the input terminals of the input filter to properly make this measurement. Notice also that the filter impedance test is usually done without any power applied to the circuit. This greatly simplifies the setup and makes it a safe and straightforward test.

Figure 3 shows the results of impedance measurements for a switching power supply and the input filter.

The blue curve of Figure 3 shows the closed-loop input impedance of the power supply, measured as described in [1]. The effect of the 3.3 µF bypass capacitor has been re-

moved from this measurement. and this component is included in the filter measurements.

The red curve of Figure 3 shows the output impedance of the input filter with the 3.3 µF capaci- dissipation of the filter. tor, and a 200  $\mu$ H inductor. The capacitor has a very low ESR, and this produces a filter network with very little damping. At the resonant frequency of about 6.2 kHz, there is a very sharp peak in the output impedance, and its value exceeds that of the closed-loop input impedance of the power supply. There will be dramatic changes in the loop gain of the power supply,

and this will be discussed in detail

in the next article of this series.

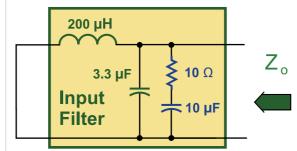

It is not advisable to have such an undamped filter at the input of the power supply, and the filter should be modified to avoid this. Figure 4 shows one possible network that can be used to damp this input filter effectively. A 10 µF capacitor in series with a 10 ohm damping resistor is connected in parallel with the original  $3.3 \,\mu\text{F}$  capacitor. The new capacitor branch carries very little switching current and has minimal dissipation. (It is, however, a sizable component when compared to the 3.3 µF MLC capacitor.) This particular damping arrangement is chosen since it provides the same attenuation

*Figure 4: One possible network for damping the* input filter. This network applies damping at the filter resonance without affecting the attenuation or

> as the undamped filter at higher frequencies, and filter performance is not compromised for the sake of damping.

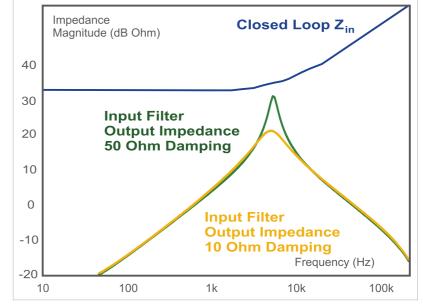

Figure 5 shows the effect of damping on the impedances of the power system. If a 50 ohm resistor is used, the output impedance of the filter is reduced to a value just a little less than the input impedance of the power supply. A 10

Figure 5: Input filter impedance with added damping network. ohm resistor provides much better damping, and greatly reduces the Q of the input filter. This is a good design choice.

The filter configurations used to meet conducted emissions standards of modern switching power supplies will be much more complex than the simple LC filter discussed here. However, damping networks can be applied in a similar manner, and the technique for measuring remains the same. Many power supply designers overlook the needs of damping the input filter, and often underestimate the amount of space needed for damping networks.

#### Summary

This article discusses how to measure and damp the output impedance of an input filter. This is a critical step for power supply design, and it must be done carefully. It is especially crucial for high density power supplies where capacitors have very small values of ESR, and high-Q filters are often created.

In the next article of this series. measurements of loop gains with and without the input filter in place will show the dramatic effects that result when the filter is not designed properly.

#### References

- Ridley Engineering Design 1. Center, www.ridleyengineering. com/index.php/design-center. html, Article [60] "Input Impedance Measurements and Filter Interactions."

- 2. Ridley Engineering Design Center, www.ridleyengineering.com/index.php/designcenter.html, Article [63] "Why You Only Need One Injection Isolator."

www.ridleyengineering.com

#### Future precision. Future performance. Now available.

#### **CAS-CASR-CKSR**

The transducers of tomorrow. LEM creates them today. Unbeatable in size, they are also adaptable and adjustable. Not to mention extremely precise. After all, they have been created to achieve great performance not only today – but as far into the future as you can imagine.

- Several current ranges from 6 to 50 A<sub>BMS</sub>

- PCB mounted

- Up to 30% smaller size (height)

- Up to 8.2 mm Clearance / Creepage distances +CTI 600 for high insulation

- Multi-Range configuration

- +5 V Single Supply

- Low offset and gain drift

- High Accuracy @ +85°C

- Access to Voltage Reference

- Analog Voltage output

#### www.lem.com

At the heart of power electronics.

# Higher power, smaller, and cooler PoL DC-DC regulation

Point-of-Load regulators benefit from innovative packaging

By: Eddie Beville, Power Module Design Manager and Afshin Odabaee, Product Marketing Manager, Linear Technology Corp.

ach generation of highend processors, FPGAs, and ASICs burdens power supplies with heavier loads. System designers, however, rarely allocate precious additional system-board space to correspond to the power inflation.

Compounding the squeeze on power supplies is the widespread requirement for greater numbers of dedicated board-mount power supplies, which provide POL (point-of-load) regulation for multiple voltage rails. Individual rails must increasingly support from tens to over a hundred amperes at low voltages—as low as 1 V or less—requiring an initial accuracy of ~1% and superb loadtransient deviation of less than a few percent. The challenge, therefore, is to find POL supplies that are accurate, can deliver high load currents at low voltages, while taking little system board space.

Once system designers find a suitably powerful regulator, they must evaluate it for power loss and thermal resistance. These two parameters can break an otherwise good regulator design if it can't

meet system heat requirements, especially when the system must operate at an elevated ambient temperature.

Obviously, conversion efficiency must be high in order to limit power loss, and the package design must feature low internal thermal resistance and a low thermal resistance connection to the ambient environment. As POL packages shrink, the thermal path between the regulator and the board decreases in area, making it increasingly difficult to keep the board cool because the power regulator usually conducts most of the power loss back into the system board, increasing the internal system temperature.

#### Heat and cost of cooling

System and thermal engineers spend a lot of time modeling and evaluating these complex electronic systems in order to develop designs that remove power loss in the form of heat. Airflow and heat sinks are typical means to remove this unwanted heat. Compounding the problem, modern processors, FPGAs, and custom ASICs usually dissipate

significantly more power as the internal system temperature increases.

This characteristic, unfortunately, results in greater power demand from the power regulators, increasing their internal power loss and the system temperature even further. So high-density power components must limit their losses and remove heat effectively. However, most compact-packaged power devices either dissipate too much power or cannot effectively remove the heat and therefore cannot operate at elevated temperature without significant de-rating.

It's no surprise that to keep the temperature of a high-power design to reasonable levels attention to cooling methods is crucial. System-design constraints have forced designers to implement cooling methods that rely on fans, cold plates, heat sinks, and sometimes submerging the system in special liquids. All are costly, but necessary. However, a high-power POL regulator that can deliver the required power while dissipating heat evenly and efficiently reduces the requirements for cooling that

portion of the circuit, saving on cooling size, weight, maintenance, and cost.

Top Side Heat Sinking

Bottom Side Heat Sinking

Power density is misleading The topic of high-power-

regulators is misleading because it does not address the device's temperature behavior. System designers should seek more information from the device's data sheet once they decide on a product that meets the system's electrical, physical, and power requirements for a DC-DC regulator. For example: If a DC-DC regulator in a 2 x 1 cm package delivers 54 W to a load, its power density is 27 W/ cm<sup>2</sup>. This number may impress a few designers and satisfy their search with their desired power, size, and price. However, what's forgotten is heat, which finally translates into temperature. The key data to study are the DC-DC regulator's thermal impedances: junction to case, junction to air, and junction to PCB.

Figure a

Continuing with the above example, the device has another attractive attribute. It operates at an efficiency of 90%. It dissipates 6 W while delivering 54 W output in a package with 20 °C/W junction-toair thermal impedance. Multiply 6 W by 20 °C/W and the result is 120 °C rise on ambient temperature. At 45 °C ambient temperature,

Power MOSFET Stack Power Inductors Figure b density DC-DC Figure 1: Side-view rendering (a) and an unmolded LTM4620 (b) junction temperature of the pack-26 A. The package supports both age of this seemingly impressive top and bottom heat sinking for DC-DC regulator is calculated at excellent thermal performance. 165 °C, which is not acceptable for two reasons: It's above the maxi-The LTM4620 consists of two mum temperature of most silicon high-performance synchronous ICs—120 °C—and it requires special attention to keep the junction range is 4.5 to 16 V; the output temperature at a safer value below voltage range is 0.6 to 2.5 V and 120 °C.

> The DC-DC regulator that seemed to address all the electrical and power requirements failed to meet thermal guidelines of the system or proved too costly to use due to additional measures to operate at a safe temperature. It's important, therefore, to study the thermal performance of a DC-DC regulator.

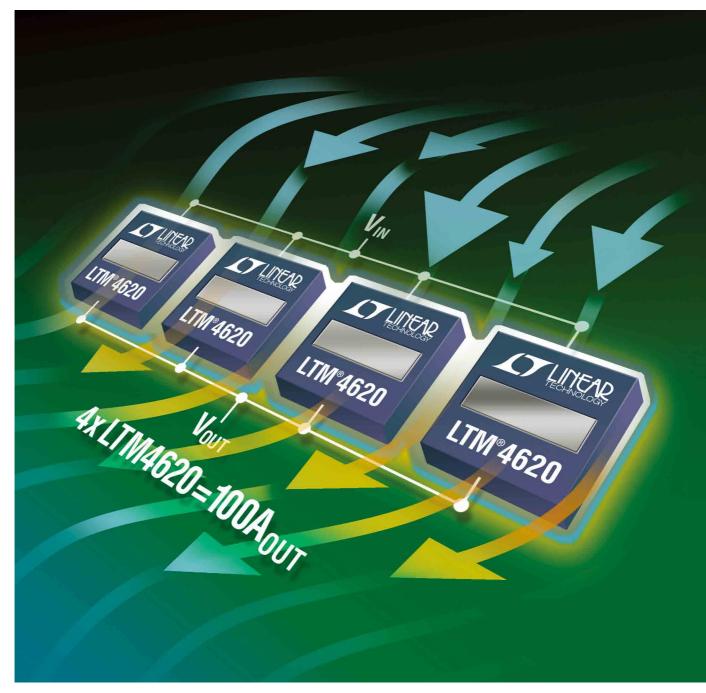

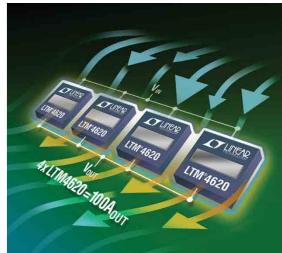

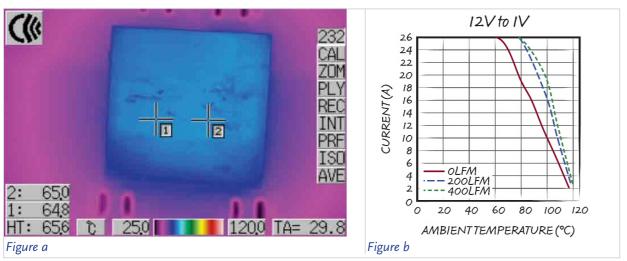

> Alternatives include, for example, high-density scalable regulators such as the LTM4620 µModule, that combine excellent electrical performance and low power loss with a thermally enhanced LGA package designs to help resolve high-power-density challenges. The LGA package measures  $15 \times 10^{-10}$ 15 x 4.41 mm. The µModule is capable of driving two independent 13-A outputs, or a single output at

buck regulators. The input voltage 0.6 to 5.5 V for the LTM4620A. The regulator provides ±1.5% total output accuracy, 100%-tested accurate current sharing, fast transient response, multiphase parallel operation with self clocking, programmable phase shift, frequency synchronization, and an accurate remote-sense amplifier. The regulator provides output over-voltage protection, fold-back over-current protection, and internal temperature-diode monitoring.

#### Package Design

A side-view rendering and topview photo of an unmolded LTM4620 shows that the package design comprises a highly thermally conductive BT (bismaleimide triazine) substrate with adequate copper layers for current-carrying capacity and low

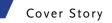

Figure 2: Thermal image (a) and de-rating curve (b)

#### Figure 3: Two-phase parallel outputs combine to deliver 26 A at 1.5 V.

thermal resistance to the system board (figure 1). A proprietary lead-frame power-MOSFET stack provides high power density, low interconnect resistance, and high thermal conductivity to both the top and bottom of the device.

The proprietary heat sink design attaches to the power MOSFET

stacks and the power inductors to provide effective topside heat sinking. System designs can add an external heat sink to the topside exposed metal to remove heat with airflow. Airflow alone with no heat sink removes heat from the topside due to construction of the integral heat sink and the mold encapsulation. requires no de-rating to ~80 °C. The thermal data confirms the merits of a thermally enhanced high-density regulator.

#### **Electrical Performance**

Operating the LTM4620 in currentsharing mode results in a highdensity 1.5-V, 26-A design (**figure 3**). This configuration ties the

Figure 4: Two-phase 1.5-V efficiency (a) and current sharing (b)

pairs of Run, Track, Comp,  $V_{FB}$ , Pgood, and  $V_{OUT}$  pins together to implement the parallel operation. The design shows one way of monitoring the device's internal temperature diode using an LTC2997 temperature-sensor monitor. Many different devices that monitor diode-connected transistors can monitor the temperature-sense diode.

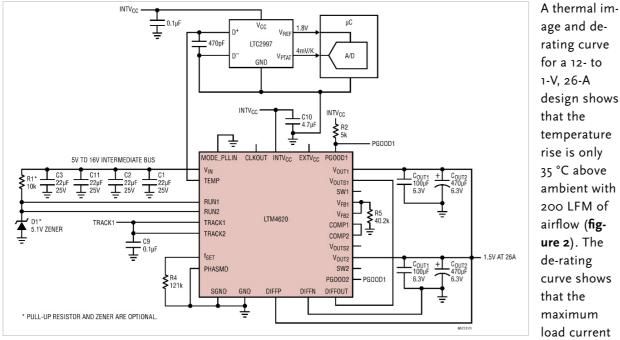

The 86% efficiency for the twophase parallel output and the two-channel current-sharing performance is very respectable for such high-density design (**figure 4**). As shown in figure 2, the temperature rise is modest due to a low  $\Theta_{JA}$  thermal resistance after board mount. The effective top and bottom heat sinking enables the regulator to operate at full power with low temperature rise.

The high-efficiency and fasttransient-response current-

*µModule 100-A regulator design* mode architecture fits well with the low-voltage core powersupply requirements for highperformance processors, FPGAs, and custom ASICS. The outputvoltage initial accuracy and the differential remote sensing provide proper DC-voltage regulation at the load point. The thermal capabilities and the

16 WWW.POWERSYSTEMSDESIGN.COM

#### Figure 5: Current sharing for an eight-phase, four-

excellent current sharing allows for scaling the output current capability to > 100 A.

Multiphase operation does not require external phaseshifted clock sources for each regulator channel. Each LTM4620 has Clock-

in and Clock-out pins with internal programmable phase shifting for clocking the paralleled channels. Designs can select either external frequency synchronization or internal on-board clocking. These clocking features further enable power scaling.

Extending this design to an eightphase, four-µModule

regulator design delivers 100 A with excellent current sharing (figure 5). The 100-A design requires about 1.95 in<sup>2</sup> of board space. A heat sink across all four modules can remove heat with airflow to minimize dissipation into the system board.

www.linear.com

# Making the switch to silicon carbide

Silicon-carbide MOSFETs outperform silicon IGBTs in high-frequency switching

By: Bob Callanan, Applications Manager and Julius Rice, Applications Engineer, Cree

o demonstrate the advantages of siliconcarbide MOSFETs versus silicon IGBTs (insulated-gate bipolar transistors) when used in high-power, high-frequency circuits, it is necessary to employ a test platform that will showcase each device's power handling characteristicsespecially switching losses-under hard-switched conditions. A SEPIC (single-ended primary-inductance converter) test platform provides a means to emulate a set of established circuit parameters, such as switching frequency, voltage, current, and temperature. It also provides a means to calculate the differences in device losses between the two different powerswitching technologies.

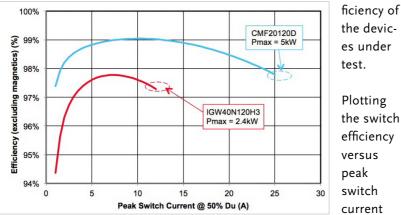

This demonstration compares a Cree CMF20120D1 1.2-kV. 20-A silicon carbide MOSFET (reference 1) and an Infineon IG-W40N120H32 1.2kV, 40-A silicon IGBT, which is a trench-stop field power device (reference 2). The IGBT exhibits a

|         | Parameter                                                 | SIC MOSFET<br>CMF20120D         | Si IGBT<br>IGW40N120H3          |  |

|---------|-----------------------------------------------------------|---------------------------------|---------------------------------|--|

| 1<br>1- | Breakdown<br>Voltage                                      | 1.2kV                           | 1.2kV                           |  |

|         | Max Current                                               | 17A, Tc=100°C                   | 40A, Tc=100°C                   |  |

| -       | Forward<br>Voltage at<br>20A                              | 1.68V,TJ=25°C<br>1.98V,TJ=150°C | 1.70V,TJ=25°C<br>1.79V,TJ=150°C |  |

|         | Total Gate<br>Charge                                      | 91 nC, V <sub>GS</sub> = 20V    | 185 nC, V <sub>GC</sub> = 15V   |  |

|         | Total Gate<br>Energy<br>(V <sub>G</sub> *Q <sub>G</sub> ) | 1.82 µJ                         | 2.78 µJ                         |  |

Table 1: SiC MOSFET and Si IGBT comparative

forward voltage

at 20 A that closely matches the SiC MOSFET. Both devices were packaged in TO-247 plastic packages and mounted on identical connectorized daughter-boards with equivalent heat sinks, which enabled the two components to be swapped out quickly and efficiently for the test procedure. Table 1 compares the specifications for the two devices.

specifications

#### Selection of the SEPIC platform for circuit comparison

Developing a single test platform to compare the switching performance of these two device technologies required a transformer-

less DC-DC converter design that re-circulated the load current back MOSFETs and Si IGBTs.

into the input link. This avoids the hardware issues that arise with transformers operating at high frequencies, such as proximity and skin effects in the windings and excessively high switching losses. The SEPIC platform delivers the flexibility to buck or boost without inverting the output voltage, making it a good choice to compare the relative switching performance and device losses between SiC With the SEPIC platform, it is possible to demonstrate the switching performance of the power devices

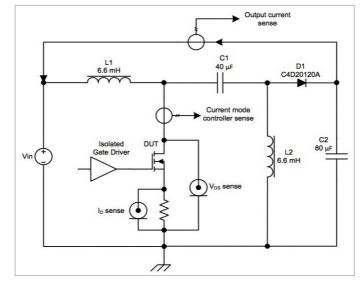

#### Figure 1: SEPIC demonstration platform schematic

without re-designing and retrofitting each potential application (motor drives, power-factor-correction circuits, grid-interfaced solar and wind inverters, and uninterruptible power supplies) with SiCbased devices and then comparing the overall system performance for each application.

The SEPIC demonstration platform features a simple buck-boost design with the ability to re-circulate the converter's output current back to the input side, while maintaining the devices under test (the power switches) at a duty cycle of approximately 50% (figure 1). This results in the voltage across the switch being twice the output current. Therefore, the input DC supply is only required to deliver half the desired switch voltage. Also, by referencing the switches to ground, accurate measurements of their voltage and current are easy to perform.

The SEPIC schematic consists of

and a diode, D1. As shown by the directional arrows, the output

current feeds back into the input source, VIN. A peak-mode current controller feeds from the current transformer to the DUT's drain connection. Meanwhile, the input for this controller is supplied from an amplifier that regulates the recirculated output current. A Halleffect sensor monitors this output.

Other diagnostic elements of the SEPIC platform include a high-frequency current-monitoring resistor that senses the DUT current, and a voltage probe featuring a Kelvin connection to measure the DUT

The results of this test platform

demonstrate that SiC MOSFETs

operating frequency with the same

efficiency, only 10% of the turn-off

losses, and significantly lower rela-

tive switching losses as compara-

Comparison of switching perfor-

bly rated Si IGBTs at 30 kHz.

mance

have up to three-times higher

#### POWER SYSTEMS DESIGN NOVEMBER 2012

the DUTs (device under test), which are the swappable power switches being tested; a blocking capacitor, C1; two inductors, L1 and L2;

voltage. Isolating the gate driver eliminates the potential to form a ground loop around the resistor.

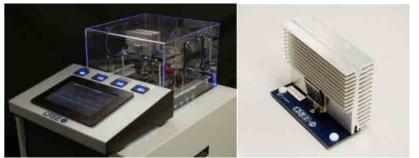

The high-voltage components and logic power supplies used in the SEPIC demonstration platform and the inductors share an enclosure, with the control panel and converter hardware on top of the assembly protected by an acrylic safety barrier (figure 2). Test results display on a monitor that shows voltage and current waveforms for the devices under test and meters display total delivered power, total delivered current, total system losses, and input power. Performance comparison at

#### Figure 2: SEPIC demonstration platform display and daughter card assembly

#### 30 kHz

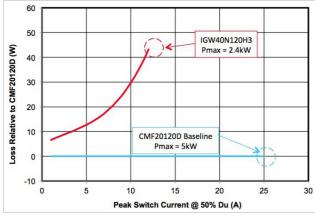

Using the input power versus peak switch current for the SiC MOS-FET as a baseline, the comparative switching losses are shown by subtracting this data from the input power versus peak switch current of the Si IGBT. The devices were tested under identical conditions of voltage, current, and frequency using the same circuit. The difference in input power between the two devices, therefore, is a direct measurement of their respective switching losses.

The Si IGBT's input power loss relative to the SiC MOSFET was plotted against the peak switch current (figure 3). For this portion of the testing at 30 kHz switching frequency, the input voltage to the SEPIC circuit was 400 V, resulting in a switch voltage of 800 V. The test terminated when it exceeded the DUT's thermal limits.

The SiC MOSFET achieved the highest switch current—25 A with 5 kW of delivered power; while the Si IGBT reached a maximum switch current of 12 A

Figure 4: Relative efficiency (without magnetics losses) of 1.2 kV demon-SiC MOSFET versus Si IGBT at 30 kHz; VDS = VCE = 800 V strates

with 2.4 kW of delivered power; with the IGBT's switching losses being the limiting factor.

100% (%)

989

96%

94%

929

90%

88% 86%

It is also possible to show the devices' relative efficiency as opposed to relative power losses. The switching devices themselves have low-loss characteristics, although the inductors (as part of the SEPIC circuit) have much larger losses (I2R); however, these losses are predictable. Therefore, by subtracting out these inductor losses from the total system losses, it is possible to see the relative switching ef-

Figure 5: 1.2 kV SiC MOSFET efficiency (without magnetics losses) at 100 kHz; VDS = VCE = 800 V that the SiC MOSFET is the

10 15 20 Peak Switch Current @ 50% Du (A)

higher efficiency device, delivering 5 kW of power; while the Si IGBT delivers just 2.4 kW, with an efficiency about 1.2% lower than the SiC device (figure 4).

T

CMF20120D

Pmax = 3.6kW

25

#### Switching performance at 100 kHz

While testing at a frequency of 100 kHz, the silicon IGBT exhibited switching losses that are so high that hard-switched operation was impractical. Conversely, the SiC MOSFET achieves a switching current of 17 A, with delivered power of 3.6 kW at this higher frequency operation, achieving both high efficiency and low losses (figure 5).

#### www.cree.com

#### References

- 1. http://www.cree.com/products/pdf/CMF20120D.pdf

- 2. http://www.infineon.com/ cms/en/product/PSLPopup. html?productType=db3a3044 252fod6f01257e72d2163909

# It's all you need.

## The AP300 Frequency Response Analyzer

Designed for switching power supplies, it is simply the best product on the market for all of your frequency response measurement needs.

WWW.POWERSYSTEMSDESIGN.COM

20

**Ridley Engineering, Inc.** 3547 53rd Ave W, Ste 347 Bradenton, FL 34210 US +1 941 538 6325

**Ridley Engineering Europe** Chemin de la Poterne Monpazier 24540 FR +33 (0)5 53 27 87 20

# Designing a DiSEqC-antenna phantom power-supply

A simple phantom power supply design allows power, a control link, and the received radio signal to coexist on the coax

By: Andrea Longobardi, Product Definer and Corporate Applications Engineer, Maxim Integrated

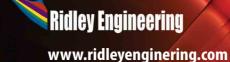

he DiSEqC (digital satellite equipment control) standard is a communication protocol developed by Eutelsat used between a satellite receiver (decoder), defined as the master, and satellite peripheral equipment such as dish switchers, LNBs (low-noise blocks), and dish positioners, defined as slaves. The DiSEqC communication system uses only the existing coaxial cable, thus making DiSEqC well suited to reduce cost and improve reliability. The DiSEqC is an open standard with nonproprietary commands.

To allow one-way DiSEqC communication on the antenna cable, the radio head unit must transmit a 22-kHz tone burst, which the remote antenna must receive. The voltage amplitude of this tone burst is 650 mV, as the DiSEqC standard requires. Note that the antenna coax cable also feeds the LNA (low-noise amplifier) and carries the received radio signal. For this reason, the DiSEqC receiver must be able to reject the radio signal on the cable.

#### **Application Circuit**

In a DiSEqC application circuit, a dual high-voltage, current-sense LDO/switch is used in LDO mode and the regulated output voltage is dynamically changed to generate the DiSEqC pulses (figure 1). The blue block is the radio head unit, which includes the remote antenna power supply used also as DiSEqC tone-burst transmitter

Figure 1: The DiSEqC application circuit

and the tuner. The red block is the remote antenna formed by the physical antenna, the LNA, and the DiSEqC receiver (a low-power comparator, such as a MAX9311).

The coax cable enables the communication between the radio head unit and the remote antenna (radio signal and DiSEqC toneburst) and is also used to feed the remote LNA, saving cost and cable weight.

The automotive LDO/switch is configured in LDO mode with a 5-V voltage output when the external NMOS is turned off (DiSEqC tone-burst off). Choosing resistors R1 and R2 determines this output voltage, as indicated in the device's data sheet (reference 1) and related application note (reference 2). If a different remote antenna feed voltage (VOUT) is required, use the following equation to choose R1 based on R2:

$$R_1 = \left(\frac{V_{OUT}}{V_{FB}} - 1\right) R_2$$

where VFB is the voltage at the feedback pin in regulation (1 V, nominal) and R2 must be less than or equal to 1 k $\Omega$ .

When the external NMOS turns on, resistor R3 connects in parallel with R2. This brings the LDO regulator output voltage to 5.65 V. With this circuit configuration, a user can easily generate a DiS-EqC 22-kHz tone burst by turning the external NMOS on and off through the microcontroller. If

a different remote-antenna feed voltage is required, choose a value for resistor R<sub>3</sub> using the equation

$$R_3 = \frac{R_1 R_2}{\left(\frac{V_{OUT} + 0.65}{V_{FB}} - 1\right)}$$

RLIM and RSENSE set the output current limit to 200 mA and the ADC full-scale range to 4 V (reference 3). For reasons of clarity, only one channel of the LDO/ switch appears on the schematic, but the same considerations are valid for the second channel.

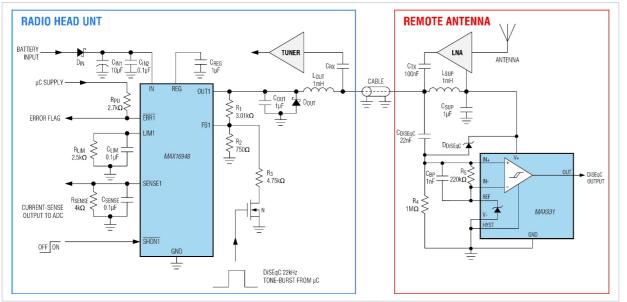

The output inductor, LOUT, is necessary to filter out the radio signal and to not conflict with the LDO regulator. Considering the AM band's lower frequency of 148 kHz, a 1-mH output inductor is sufficient. The tuner extracts the radio signal from the coax cable with a bypass capacitor, CRX. The remote antenna power supply used to feed the LNA is obtained through a lowpass filter built with inductor, LSUP, and capacitor, CSUP. To a first approximation, the power-supply filter is an RLC lowpass filter (figure 2). The -3dB passband must be below the frequency used for DiSEqC communication.

Figure 2: Power supply filter

#### POWER SYSTEMS DESIGN NOVEMBER 2012

$R_{2} - R_{1}$

The low-power comparator acts as the DiSEqC receiver and is supplied with the same voltage supply as the LNA. The negative comparator input, IN-, is connected to the REF voltage provided by the comparator itself, while the positive comparator input, IN+, is polarized with a resistor divider, R4 and R5, in order to have zero voltage output on the DiSEqC output in the absence of a DiSEgC tone-burst.

To sense the DiSEqC tone-burst, a 22-nF capacitor, CDiSEqC, connects between the coax cable and the negative comparator input. When a tone-burst is sent on the coax cable, the IN+ voltage exceeds the IN- voltage, which generates a pulse on the output of the comparator. A protection Schottky diode, DDisEqC connects between IN+ and the comparator power supply input, V+, to avoid an over-voltage fault on the IN+ pin.

To avoid false output pulse triggering due to the radio signal travelling on the cable, a 1-nF bypass capacitor, CBP, is placed between the comparator inputs, from IN+ to IN-. The radio signal received from the remote

$R = R_{LNA}$  $\begin{cases} R & L = L_{OUT} + L_{CABLE} + L_{SUP} \\ C = C_{SUP} \end{cases}$  antenna and amplified with the LNA is injected onto the cable with a capacitor Стх.

#### Figure 3: RF signal at 148 kHz and 500-mV amplitude

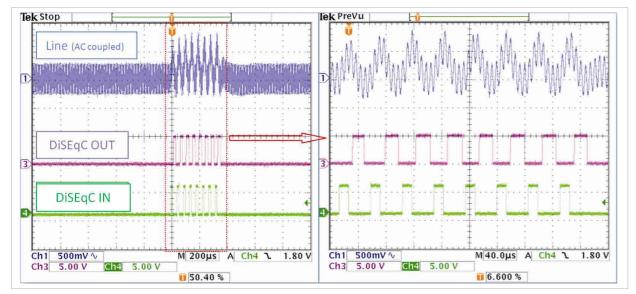

**Bench Tests** Bench tests were performed, which generated eight 5-V-amplioscilloscope monitored the output of the comparator to confirm whether the sent tone-bursts were

signal at 148 kHz and 500-mV amplitude, which coincides with the lower AM band frequency.

#### Figure 4: RF signal at 37 kHz and 500-mV amplitude

tude 22-kHz tone-bursts with a waveform generator connected to the gate of the external NMOS. A sinusoidal 500-mV amplitude RF signal was obtained with another waveform generator and injected with the CTX capacitor, emulating the LNA output radio signal. An received and to ensure that the injected radio signal did not influence the DiSEqC communication.

Figure 3 and Figure 4 illustrate the scope traces corresponding to the performed tests. Figure 3 shows the results with an injected radio

Figure 4 shows the results with an injected radio signal at 37 kHz and 500-mV amplitude, which is the second subharmonic of the lower AM band frequency, 148 kHz,.

The DiSEqC application circuit is

a low-cost and flexible design for an antenna phantom power supply that is compatible with the DiSEqC communication standard. Additional bench test results have confirmed that DiSEqC communication still operates when selecting the DiSEqC tone-burst frequency in the range between 100 Hz and 30 kHz. This provides the flexibility to tune the most suitable frequency for DiSEqC communication, thus minimizing interference with other RF signals on the coax cable. Product designers can also regulate the tone-burst duty cycle and add hysteresis to the comparator to attain the best DiSEqC communication performance.

This application circuit enables one-way DiSEqC communication. If a receive-acknowledge signal is needed from the remote antenna, it can be generated by modulating the load current of the LDO/switch. A simple way to do this would be to connect an extra load in parallel to the LNA supply inside the remote antenna once the DiSEqC message is received. The microcontroller in the radio head unit can receive the acknowledgment by sampling the load current variation on the MAX16948's current-sense output, SENSE. The switched extra load could be easily built up with an NMOS switch in series with a pullup resistor connected to the LNA supply inside the remote antenna.

#### www.maximintegrated.com

#### References

- MAX16948 data sheet: http://www. maximintegrated.com/MAX16948

- 2. Maxim application note 5271, Selecting External Components for an Automotive Dual Remote Antenna Current-Sense LDO/Switch, http://www. maximintegrated.com/AN5271.

- 3. Maxim application note 5271, Selecting External Components for an Automotive Dual Remote Antenna Current-Sense LDO/Switch, http://www. maximintegrated.com/AN5271.

## SUBSTITUTE FOR TRANSFORMERS – 5 LETTERS

#### LOW OHMIC PRECISION AND POWER RESISTORS

#### SMD SHUNT RESISTORS SAVE SPACE AND OFFER A NUMBER OF ADVANTAGES:

- \_ High pulse loadability (10 J)

- \_ High total capacity (7 W)

- \_ Very low temperature dependency over a large temperature range

- \_ Low thermoelectric voltage

- \_ Customer-specific solutions (electrical/mechanical)

#### Areas of use:

Power train technology (automotive and non-automotive applications), digital electricity meters, AC/DC as well as DC/DC converters, power supplies, IGBT modules, etc.

Isabellenhütte Heusler GmbH & Co. KG Eibacher Weg 3–5-35683 Dillenburg · Phone +49 (0) 2771 934-0 · Fax +49 (0) 2771 23030 sales.components@isabellenhuette.de · www.isabellenhuette.de

# Thermal design considerations for thin power MOSFETs

Applications with high pulse currents benefit from thin, low RDS(on) MOSFETs but demand care in thermal design

By: Ralf Walter, Application Engineer, Infineon Technologies AG

hermal challenges accompany almost all advances in powerelectronic designs. Load cases not covered under a datasheet's parameters are often particularly problematic.

Each new MOSFET generation generally marks a significant reduction in the area-specific onstate resistance—the product of RDS(on) and area. This means that a MOSFET with the same chip size offers dramatically reduced RDS(on) figures.

Many optimization steps are required to achieve this outcome including altering the cell structures and scaling individual areas. The thickness of the silicon is usually also reduced, which can bring about shifts in thermal behavior. The reduction in silicon thickness lowers the thermal resistance, also reducing the amount of silicon available for temporary high loads.

The challenge to the developer is to calculate these changes in the thermal behavior for each specific

application and to optimize the design as appropriate. Datasheet values and the PSPICE library may not provide sufficient indicators for special cases, such as temporary loads, and analyses carried out using a thermal camera for such fast processes do not provide reliable values for the temperatures within the power device's package.

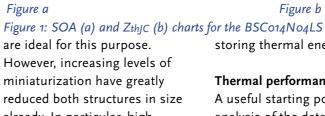

Thin MOSFETs, such as Infineon's 40- and 60-V OptiMOS power MOSFET generation, feature on-state resistances to about half of the previous generation's values without changing chip sizes. This was only possible by reducing the thickness of the silicon. Chip thickness values in this voltage range are typically still in tenths of millimeters.

Besides conventional switchedmode power supplies (such as synchronous rectifiers on the secondary side), typical applications in these voltage classes include motor controls in cordless power tools like screwdrivers and similar

products. These designs must withstand high loads for short periods as they are often subject to such peaks under real operating conditions. It is therefore completely normal that a multiple of the rated current is permissible for a second, for example, when fully and securely driving a screw into a material.

The resulting losses in the MOSFETs are briefly much higher than in rated operation. One possible design choice would be to reduce the losses by massive parallelization. However, this is not practical (or even possible in some cases) for cost and space reasons. On the other hand, such overload cases are one*time* events from a thermal point of view since a repetition is not likely until many seconds later (for the next screw).

Now, however, it is possible to buffer the power loss occurring during this short peak load and to dissipate it slowly over the lengthy period before the next power impulse. Silicon and the copper lead frame

already. In particular, highperformance packages, such as the SuperSO8, have fewer options for storing thermal energy due to their small volume.

Manufacturers can use special IMS (insulated metal substrate) PCB designs for such SMD components. These consist, in principle, of an aluminum or copper substrate—usually between 0.5 mm and 3 mm thick-with a thin laminated insulation layer of enriched epoxy. The copper conductors and the SMD components are located on that layer. The metal substrate can operate as a thermal tank for

storing thermal energy.

Figure b

#### Thermal performance

A useful starting point is an analysis of the datasheet areas that describe thermal behavior in relation to time and power dissipation. For example, the SOA and ZthJC charts (figure 1) depict the performance of a BSC014N04LS 40-V MOSFET that offers an RDS(on) of 1.4 $m\Omega$  in a 5- x 6-mm SuperSO8 package.

As the figure depicts, the MOSFET reaches a quasistatic state within 10 ms. An examination of thermal equivalent circuit diagram for the different silicon generations indicates that the chip volume plays a role only for short events

#### POWER SYSTEMS DESIGN NOVEMBER 2012

below 100 µs. Even for very short load impulses, thermal energy can no longer be stored in the chip, but must instead dissipate first to the solder and lead frame and, after several

milliseconds, to the environment. This means that chip volume does not play any measurable role in the case of impulses lasting at least one second. This is also clear when regarding the thermal properties of the materials-silicon, solder, and copper-in combination with their volume. This thermal behavior also reflects in the equivalent circuit diagram or **PSPICE** parameters.

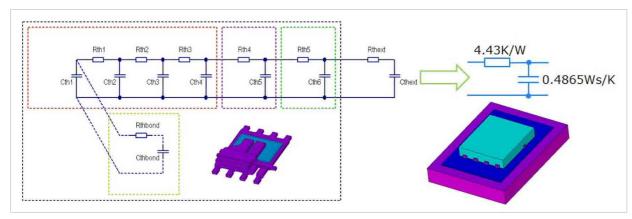

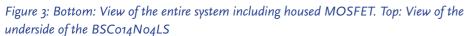

A thermal-equivalent circuit can depict the thermal system including the substrate (Figure 2). In this example, the BSC014N04LS in its SuperSO8 package combines with the properties of an acceptably priced IMS. Here the specific thermal conductivity of the IMS's

Figure 2: BSC014N04LS on IMS with thermal equivalent circuit diagram of the complete structure

insulation layer is 1.3 W/(m x K) with a layer thickness of 76 µm.

Calculating the system's temperature rise results in a value for theoretically homogeneous energy distribution, for which a  $\Delta T$  of about 51 K is generally acceptable. In a real system, however, the time constants play a major role. Purely mathematically,

$$R_{th}C_{th} = 4.43 \frac{\text{K}}{\text{W}} \cdot 0.4865 \frac{\text{Ws}}{\text{K}} = 2.155 \,\text{s},$$

and non-homogeneous distribution of the temperature is to be expected. The real world behavior—the heating of the

individual components in the system—is very much removed from the ideal model.

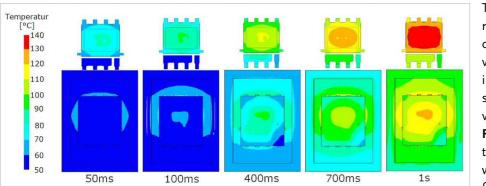

The finite-element method offers a way of obtaining realistic values for each individual point of such a system, and of visualizing the values. Figure 3 shows how the temperature changes within one second for an assumed 25-W load. This corresponds to considerably more than 100-A drain current with 100% turn-on as a typical excess

load that occurs when driving in

a screw.

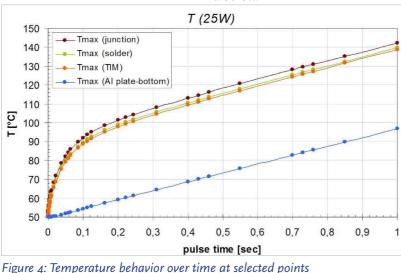

After several hundred milliseconds, the MOSFET's plastic housing becomes hot while the aluminum profile remains noticeably cooler due to non-homogeneous. After the second expires, the outer housing temperature of 120 °C has risen more than considerably and has reached the vicinity of the maximum permissible value. The underside of the component (top row of images) reaches a temperature near 140 °C. The temperature behavior can be seen in greater detail in the timing diagram (Figure 4).

As a result of the MOSFET cells' good thermal connection to the copper lead frame, the maximum temperature difference between the chip and lead frame is only about 4 K (dark red and orange lines). Also clear is a short nonlinear interval-up to about 100 ms-after which all temperature behaviors are more or less linear. This is due to the previously mentioned short time constants within the component, as Figure 1 indicated earlier. Figure 4 also shows that these findings can easily transfer to another situation (power loss, turn-on relationship, starting temperature, impulse length, etc.) with sufficient precision. In the case of lower power losses or turn-on ratios, the line moves down in the according ratio. A shift upwards corresponds to greater power losses. Given the linear characteristics beyond about 100 ms, extending the lines displays longer impulse lengths.

The 143-°C results for the example shown are close to the BSC014N04LS's permissible thermal limits—TJ(max) = 150°C. The fact that the simulation assumes worst-case values offers additional security. It would be problematic, of course, if, for example, the impulse lengths were greater or if the power losses were more than 25 W because the reliability of the application could suffer under certain conditions without a change in the setup. An unacceptable reduction in the lifetime of the chip would be the consequence.

Regarding the task in detail, there are a number of possibilities for improving the situation. Due to the non-homogeneous temperature distribution on the aluminum profile, it does not make much sense to increase it in size. The mounting volume may then no longer be acceptable and the costs would increase.

It is much more advantageous to increase the thickness of the profile, which can greatly increase the effectiveness of the thermal tank for this brief impulse. However, this can result in cost and space disadvantages. Yet another design alternative would be to use an IMS material with superior thermal conductivity. The sharp rise in costs for this special material represents a drawback though.

#### POWER SYSTEMS DESIGN NOVEMBER 2012

A further possibility is careful selection of power devices from the extensive range of available components. The developer can select an optimum combination, balancing cost and performance.

In the setup shown above, a MOSFET with a low RDS(on), such as the 1-m $\Omega$  BSC010N04LS, proved to be a good choice with the added bonus of enhanced switching performance. Also available are 40-V chips with monolithic integrated Schottkylike diodes such as the BSC010N04LSI, which offer advantages, in particular, for fast switching.

When assessing modern silicon technologies, consider whether the improvements in certain parameters, such as RDS(on), will result in disadvantages in other areas including thermal management. As the example given here shows, a reduction in the thickness of the silicon layer does not present a disadvantage in this or similar applications. Instead, the reduced thickness even lowers the thermal resistance between the MOSFET cells responsible for power loss and the copper lead frame, and the thermal capacity only suffers to an insignificant degree. The latter property only has an effect in the microsecond range in any case.

www.infineon.com

WWW.POWERSYSTEMSDESIGN.COM 29

# New technology and acquisitions benefit wireless sensing

Maturing WSN technologies from established sources ready for mainstream applications

By: Harry Forbes, Senior Analyst, Automation, ARC Advisory Group

ireless sensing is the most important new technology in process measurement to appear in decades. For this reason alone, it has attracted the sustained attention of ARC Advisory Group and other industry analyst organizations. While growth of wireless measurements in industrial applications has proven to be slower than most forecasts, wireless continues to grow much faster than the overall automation market.

Looking at the changes in WSN (wireless sensor networking) during the past year, ARC is most impressed by the greater maturity of the industry along with significant new technical achievements. We believe that both will spur market growth because they enable WSN to serve a much larger set of customers. The events of the last year at WSN leader Dust Networks provide an excellent example of how these developments have changedand will continue to change—the wireless-sensing market.

#### **Commercial Maturity**

Greater WSN industry maturity has come through a steady series of acquisitions. At present, much larger companies have acquired almost all the pioneering sensornetworking ventures. Most of the acquirers are well-established semiconductor suppliers, which have now snapped up virtually all the fabless WSN firms. Dust Networks has become one of the more recent, acquired in late 2011 by specialist Linear Technology.

Fortune 1000 companies must carefully manage the technologies they employ if they are to meet their customer expectations. A technology sourced from a group of venture-stage fabless semiconductor firms represents a major supply-chain risk to global firms whose customers expect product support for many years going forward. Today the list of WSN suppliers no longer represents an exceptional risk to the supply chain of global giants like Emerson, GE, Honeywell, and Siemens (figure 1).

For Dust Networks, besides

Figure 1: Emerson Rosemount's 3051S series wireless instrumentation exemplifies the benefits WSN brings to industrial applications: It can reduce total installation costs by 45% and total deployment time by as much as 75%, eliminating design and installation time and cost associated with wiring, conduit, cable trays, and junction boxes. joining a \$1.5 billion chip company with global presence, the acquisition has enabled

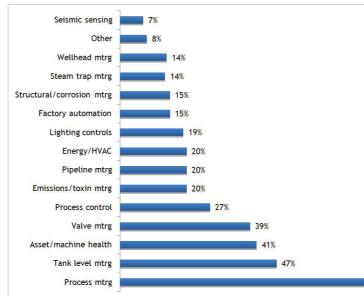

#### Figure 2: Industrial applications for WSN products. (source: OnWorld, 2012)

Dust to adopt a mature testing and commercialization process. Linear uses this internal rigor to ensure the high quality it uses as a differentiator. Roughly, 40% of Linear's business is with industrial customers, so Linear is familiar with their demands. Similarly, Dust Networks chose to focus on industrial WSN applications from its earliest days (figure 2). Through dialog with industrial customers, Dust developed its product mantra of low power and reliable delivery. These two attributes have governed Dust's design decisions for years and skillfully pursuing both goals accounts for Dust's market-share leadership in industrial WSN applications.

Dust has adopted Linear's processes for its latest product release. The Dust acquisition, then, is not merely a plan to grow volume through wider distribution. Rather, it also adds

#### value through improvements to Dust's internal development and commercialization processes. **Technical Growth**

WSN has also grown technically during the past year. The most important development is the completion of the *e* revision to the IEEE 802.15.4 standard. Though the 15.4 standard published years ago, most commercial WSN applications have used nonstandard MAC (medium access) rules to optimize the performance of their own networks.

WirelessHART, ISA100.11a, ZigBee, and IPv6 sensor networks all depended on a customized MAC layer to achieve low power consumption and reliable end-toend message delivery. This limits the value of the IEEE standard, because applications needed their own specialized MACs.

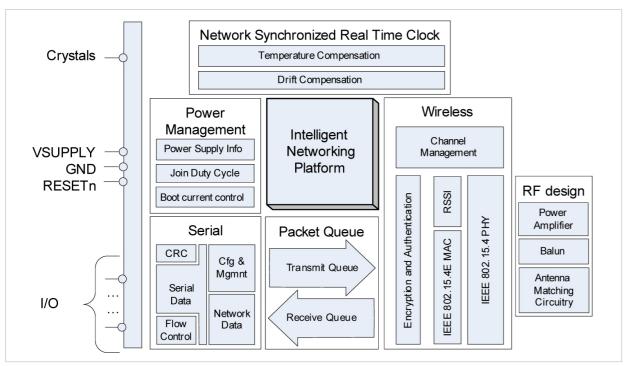

IEEE 802.15.4e makes important Dust now employs its most recent changes to the defined MAC layer. chip design, which conforms

It creates a standard and fully defined MAC that can support diverse types of networks. This includes 6LoWPAN-compressed IPv6 networks. It also supports the synchronized TDMA (time division multiple access) network properties used in industrial low-power applications such as WirelessHART and ISA100.11a. Finally, 15.4e accommodates extensions, so that these diverse networks-as well as future ones—can extend the standard MAC without violating the standard itself. This decouples WSN development from the threeto four-year long IEEE standardsdevelopment process. It will give the IEEE standard greater value and a much longer life, enable greater interoperability among WSN silicon and network stacks, and enable future WSN technologies to leverage an existing and fully standard MAC.

#### Dust Networks and 15.4e

The new standard incorporates many of the technology enhancements that Dust Networks discovered and championed from its earliest days, and has continued to use right through the newest SmartMesh WH and SmartMesh IP products (figure 3). But, the new standard was developed not only from Dust's technology but also with extensive and enthusiastic contributions from many major suppliers, notably including Siemens.

Figure 3: Block diagram of the LTC5800-WHM SmartMesh WirelessHART MoC (mote on chip).

to 15.4e, in both WirelessHART and IPv6 products. Using the latest chipset is a big benefit for WirelessHART industrial customers, since Dust has driven down the power consumption of its chipsets by roughly 50% with each new generation. In batterypowered industrial devices, this provides an *energy surplus* enabling devices to have longer life and to serve in applications that previously consumed too much battery power.

The ability to serve both WirelessHART and IPv6 applications from a single chip design also positions Dust for growth in both markets. IPv6 applications can use a wider variety of system architectures. In particular, they can route packets from field sensors to analytics and applications that

are truly location-independent, including cloud-based applications. It remains to be seen what impact the Cloud will have on the wireless sensing market, but the combination of high scalability and low cost offered by cloud services may well enable new applications that are not feasible when built using traditional WSN gateways.

Dust Networks continues to focus on products that lead the market in terms of low energy consumption. This lengthens the life of devices in industrial applications, which is particularly valuable to both industrial OEMs and their customers.

Dust Networks also uses its huge experience base to optimize its network manager. In most WSN

applications, the network manager is both extremely active and mission-critical. Active network management permits a sensor network to achieve highly reliable end-to-end service combined with low energy use. This is possible only because the network manager continuously makes decisions that dynamically reconfigure the network so that it operates reliably over point-to-point links that are inherently unreliable.

Another area to watch may be energy harvesting. Though energy harvesting represents an ongoing technical challenge, it is a very active development area. Low power products will be the first to benefit from any new harvesting components that emerge.

www.arcweb.com

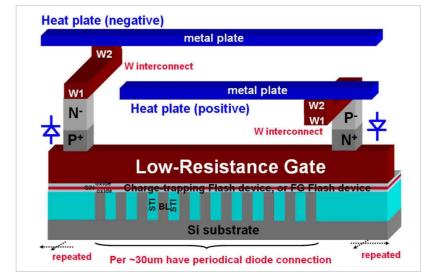

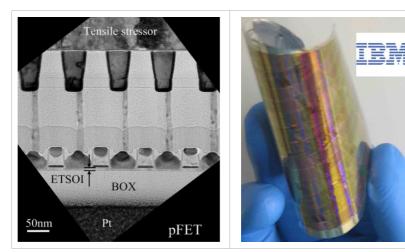

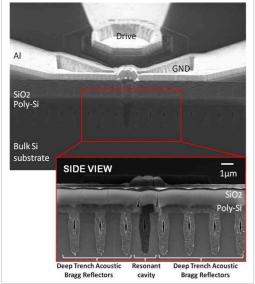

## IEDM, where the device is king but the material base suggests new approaches to manufacture

By: Gail Purvis, Europe Editor, Power Systems Design

ith a 60-year pedigree the IEDM (IEEE International Electron Devices Meeting) is that pre-eminent forum where the world reports technological breakthrough in the areas of semiconductors, electronicdevices technology, design, manufacturing, physics, and modeling. It is the realized R&D dream, the first steps to producing eventually the electronic components, devices, systems, and applications of the biennial Electronica, now in its 25th year, and alternating with Productronica manufacturing slant.

IEDM has also become the flagship conference for nanometer-scale CMOS transistor technology, advanced memory, displays, sensors, MEMS devices, novel quantum, phenomenology, optoelectronics, power, energy harvesting, and high-speed devices, not to mention process technology, device modeling, and simulation.

This year in December at San Francisco, those who have the thrill of attending will see an increased emphasis on circuit

and device interaction. With the ever-increasing transistor count, nanometer design rules, and layout restrictions, circuitdevice interaction is becoming highly critical to provide viable technology.

This is seen as one new emphasis that includes technology and circuit co-optimization, power to performance to area analyses

Figure b

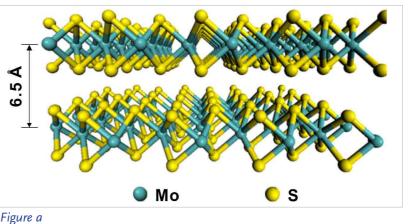

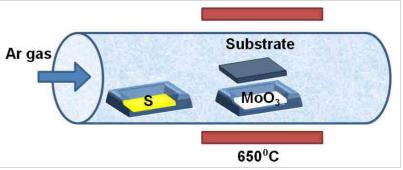

Figure 1: The MoS lattice structure (a) and a schematic of the CVD process for growing single layer MoS, which shows great uniformity and coverage (b).

design for manufacturing and process control, as well as the better known, more traditional CMOS platform technology with its continuous scaling.

Among some 220 presentations, which of course includes Intel unveiling its *hot* trigate manufacturing technology and Europe's imec presenting a plenary talk, two invited

presentations, one tutorial, and nine papers with imec researchers as first authors and co-authored, there are several new material straws revealed for future devices.

MoS (molybdenum sulphide) is one of the new entrants cheerfully determined to nudge grapheme slightly off its pedestal. A 2D material, MoS has grapheme characteristics, but unlike grapheme, it also has a wide energy bandgap, which enable fabricators to build transistors and circuits directly from it.

MIT researchers will be describing the use of that traditional workhorse CVD (chemical vapor deposition) process to grow the uniform, flexible, single molecular layers of MoS, comprising a layer of Mo atoms sandwiched between two layers of S atoms (**figure 1**).

They then exploited the material's 1.8-eV bandgap to build MoS transistors and simple digital and analog circuits, namely a NAND logic gate and a 1-bit ADC converter. The transistors have demonstrated record MoS mobility > 190 cm<sup>2</sup>/Vs, an ultra-high onoff current ratio of 108, record current density of  $\sim 20 \,\mu$ A/ $\mu$ m, and saturation, as well as putting on the first ever GHz RF performance from MoS. These results would seem to show MoS as suitable for mixed-signal applications, and useful for those that require both high performance and mechanical

| Project                             | Pros                                                                                                                                                                               | Cons                                                                                   |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Darpa<br>SyNAPSE<br>(IBM)           | <ul> <li>256 neuron chip.</li> <li>256k CMOS SRAM synapses.</li> <li>Received substantial SyNAPSE funding.</li> </ul>                                                              | Axon-neuron crossbar does<br>not scale well.     Interconnection problem               |

| LETI                                | <ul> <li>PRAM synapse.</li> <li>Pattern recognition.</li> </ul>                                                                                                                    | Crossbar may not scale well.                                                           |