September 2012

Power Systems Design: Empowering Global Innovation

SPECIAL REPORT: GRID POWER (PG39)

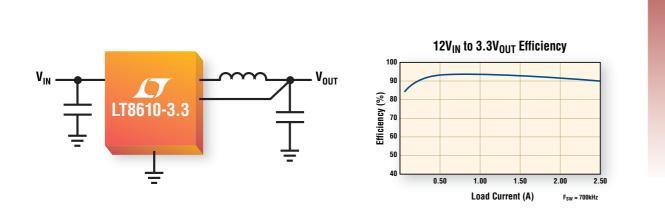

## 42V, 2MHz Sync Buck

#### 2.5A Output Current, 2.5µA I<sub>0</sub>, 94% Efficient

The LT<sup>®</sup>8610/11 are our first constant frequency, ultralow quiescent current high voltage monolithic synchronous buck regulators. They consume only 2.5µA of quiescent current while regulating an output of 3.3V from a 12V input source. Their low ripple Burst Mode<sup>®</sup> operation maintains high efficiencies at low output currents while keeping output ripple below 10mV<sub>P-P</sub>. Even at >2MHz switching frequency, high step-down ratios enable compact footprints for a wide array of applications, including automotive. The LT8611 enables accurate current regulation and monitoring for driving LEDs, charging batteries or supercaps, and for controlling power dissipation during fault conditions.

#### **Features**

- 3.4V to 42V Input Range

- 2.5µA Io Regulating @ 12VIN to 3.3VOUT

- Output Ripple <10mV<sub>P-P</sub>

- 99.9% Duty Cycle for Low Dropout

- 94% Efficiency at 1A,  $12V_{IN}$  to  $3.3V_{OUT}$

- >2MHz Operation even with High Step-down Ratios

- Accurate Input/Output Current Regulation, Limiting and Monitoring (LT8611)

#### LT8610 Demo Circuit

Actual Size

15mm x 18mm

www.linear.com/product/LT8610 +49-89-962455-0

V Info & Free Samples

http://video.linear.com/114

C, LT, LTC, LTM, Linear Technology, the Linear logo and Burst Mode are registered trademarks of Linear Technology Corporation All other trademarks are the property of their respective owners.

Europe Sales offices: France 33-1-41079555 Italy 39-02-38093656 Germany 49-89-9624550 Sweden 46-8-623-1600 UK 44-1628-47066 Finland 358-9-8873302 Distributors: Belguim ACAL 32-0-27205983 Finland Tech Data 358-9-88733382 France Arrow Electronique 33-1-49-784978, Tekelec Airtronic 33-1-56302425 Germany Insight 49-89-611080,

Setron 49-531-80980 Ireland MEMEC 353-61-411842 Israel Avnet Components 972-9-778-0351 Italy Silverstar 39-02-66125-1 Netherlands ACAL 31-0-402502602 Spain Arrow 34-91-304-3040 Turkey Arrow Elektronis 80-216-6455090 UK Arrow Electronics 44-1234-791719, Insight Memce 44-1296-330061

Power Systems Design: Empowering Global Innovation

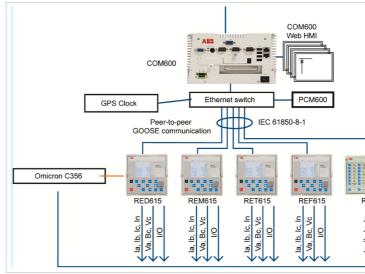

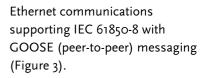

IEC 61850 Increases Grid Reliability By Howard Self and Cleber Angelo ABB

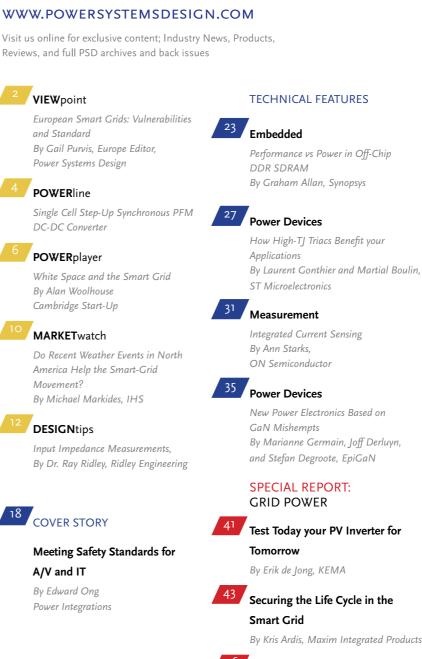

#### 18 COVER STORY

#### POWER SYSTEMS DESIGN SEPTEMBER 2012

Meeting Safety Standards for A/V

Highlighted Products News, Industry News and more web-only content, to: www.powersystemsdesign.com

CAREERdevelopment

#### GREENpage

Smart-Grid Chemical Power Plans: The Batterv By Gail Purvis, Europe Editor, Power Systems Design

POWER SYSTEMS DESIGN

AGS Media Group 146 Charles Street Annapolis, MD 21401 USATel: +410.295.0177 Fax: +510.217.3608 www.powersystemsdesign.com

#### Editor-in-Chief

Joshua Israelsohn, Editor-in-Chief, Power Systems Design joshua@powersystemsdesign.com

#### **Contributing Editors**

Gail Purvis, European Editor, Power Systems Design Gail.Purvis@powersystemsdesign.com

Liu Hong, Editor-in-Chief, Power Systems Design China powersdc@126.com

Ash Sharma, IMS Research Ash.sharma@imsresearch.com

Dr. Ray Ridley, Ridley Engineering RRidley@ridleyengineerng.com

David Morrison, How2Power david@how2power.com

#### **Publishing Director**

lim Graham jim.graham@powersystemsdesign.com

#### Publisher

Julia Stocks Julia.stocks@powersystemsdesign.com

#### **Circulation Management**

Kathryn Philips kathryn.phillips@powersystemsdesign.com

Magazine Design Louis C. Geiger

louis@agencyofrecord.com

**Production Manager** Chris Corneal

chris.corneal@powersystemsdesign.com

Registration of copyright: January 2004 ISSN number: 1613-6365

AGS Media Group and Power Systems Design Europe magazine assume and hereby disclaim any liability to any person for any loss or damage by errors or ommissions in the material contained herein regardless of whether such errors result from negligence, accident or any other cause whatsoever. Send address changes to: circulation@powersystemsdesign.comFree Magazine Subscriptions,

go to: www.powersystemsdesign.com

Volume 9, Issue 7

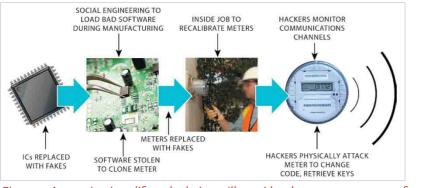

### **EUROPEAN SMART GRIDS:** VULNERABILITIES

#### AND STANDARD

As the smart grid of 2020 is expected to see the growth of smart meter units installed in Europe, perhaps someone needs to take a long hard look at the security of such systems. The cumulative number of smart meter units installed in Europe is set to grow from 7.6 million units in 2010 to 106 million units in 2020 at a CAGR of 30.2%. There is particular focus in Europe on the implementation of smart meters, especially in France, Spain, and the UK, all of which have strong smart-meter deployment plans.

For example, according to reports in June, Siemens had fixed the vulnerability in its industrial control kit similar to those the Stuxnet worm exploits. In August, however, it received notification of a different breach by the US ICS-Cert (United States Industrial-Control Systems Cyber Emergency-Response Team) over a vulnerability discovered in RuggedCom's operating system that would give attackers a way to decrypt traffic between an end user and the router. RuggedCom, acquired by Siemens in March, manufactures Ethernet switches, network routers, wireless devices, serial servers, media converters, and other communications equipment used in harsh electrical and climatic environments found in electrical-power substations, oil refineries, military installations, or roadside traffic-control cabinets.

Perhaps Europe could learn from the Swedish experience since 100% smart meter penetration was achieved by July 2009, when it became the first country to do so. It achieved this by mandating monthly meter-value collection by utilities. An increase in customer awareness of smart grid technologies, however, is leading to data-security concerns.

Interesting to note, increased awareness of smart meters has raised concerns over security and customer-privacy rights in Europe. These concerns have led the EC (European Commission) to issue a mandate to ESOs (European Standardisation Organisations) to develop technical standards for smart grids taking a privacy-by-design approach. Industry watchers expect the reference architecture for smart grids in Europe and an essential set of standards to issue by the end of 2012.

Best Regards,

Gail Purvis

Europe Editor Power Systems Design Gail.Purvis@powersystemsdesign.com

Editor's note: For more on security in Smart-Grid applications, see the article Securing the life cycle in the smart grid in this issue's Special Report section.

Vicor gives power system architects the flexibility to choose from modular, plug-and-play components, ranging from bricks to semiconductor-centric solutions with seamless integration across all power distribution architectures. From the wall plug to the point of load.

Don't let inflexible power products slow you down. Choose from limitless power options to speed your competitive advantage.

#### Flexibility. Density. Efficiency.

Trust your product performance to Vicor.

Distributed

Factorized

**Power Management**

Innovation

Integration

Performance

Speed

Efficiency

Density

### More Flexibility

Support

Expertise

Productivity

Reliability

Oualified

The Power Behind Performance

### SINGLE CELL STEP-UP SYNCHRONOUS PFM **DC-DC CONVERTER**

XC9140 series is a new synchronous step-up DC-DC converter from Torex Semiconductor.

ntegrating a 0.6  $\Omega$  N-channel driver transistor and a 0.8  $\Omega$  synchronous P-channel switching transistor, the XC9140 offers high levels of efficiency and superior performance for demanding battery-powered applications.

The IC allows the use of ceramic capacitors and draws very low quiescent current due to the combination of PFM (pulsefrequency modulation) control and CMOS structure. The 1.2 MHz nominal switching frequency makes it possible to use a small multilayer coil and, together with two ceramic capacitors, the PCB mounting area is approximately 74% smaller than that of the previous product.

Able to start operation from input voltages as low as 0.9 V, the XC9140 is suitable for use with single alkaline or nickel metal hydride cells. Like all step-up DC-DCs, the output current that the XC9140 can supply will depend on the VIN and VOUT conditions, but the converter can supply up

to 100 mA with VIN = 1.8 V and VOUT = 3.3 V. With VIN = 0.9 V,the device can supply more than 50mA.

The output voltage is set internally between 1.8 and 5.0 V in 0.1 V increments with an accuracy of  $\pm 2\%$ . The SX9140's quiescent current is only 6.3  $\mu A$  (typ), reducing to 0.1  $\mu A$ (typ) during standby, helping to maximise battery life in portable applications.

The XC9140 series also features a soft-start circuit, an enable pin to turn the IC on and off, and a load disconnect function that prevents the battery charge from leaking to the output while the IC is not operating (XC9140A). An optional CL discharge function can quickly discharge the output capacitor when the IC is turned off and an input by-pass mode function type is also available to keep the connection between the input and output side during shutdown (XC9140C).

An optional UVLO function

can also reduce the leakage of potassium hydroxide from small batteries by stopping IC operation while battery voltage is declining. The standard UVLO release voltage is 2.15 V (±3.0%) and selectable voltages range from 1.65 to 2.2 V.

The XC9140 is now available in the USP-6EL package for applications that require a small form factor or in the industry standard SOT-25 package. Additionally a fully populated EVB is available upon request.

#### Feature Summary:

Input voltage: 0.9 to 5.5 V Output voltage: 1.8 to 5.0 V Output current: 100 mA Supply current: 6.3 µA Switching frequency: 1.2 MHz Packages: SOT-25, USP-6EL Options: Load disconnect Input bypass

www.torex-europe.com

#### 2SP0115T Gate Driver

Unleash the full power of your converter design using the new 2SP0115T Plug-and-Play driver. With its direct paralleling capability, the scalability of your design into highest power ratings is unlimited. Rugged SCALE-2 technology enables the complete driver functionality on a single PCB board, exactly fitting the size of 17mm dual modules. Combined with the CONCEPT advanced active clamping function, the electrical performance of the IGBT can be fully exploited while keeping the SOA of the IGBT. Needless to say that the high integration level provides the best possible reliability by a minimzed number of components.

#### $C \equiv PT$ INTELLIGENT POWER ELECTRONICS

### Unleash **Sheer Power!**

SAMPLES AVAILABLE!

#### Features

Plug-and-Play solution 1W output power 15A gate current <100ns delay time ± 4ns jitter Advanced active clamping Direct- and halfbridge mode Direct paralleling capability 2-level and multilevel topologies DIC-20 electrical interface Safe isolation to EN50178 UL compliant

#### www.IGBT-Driver.com

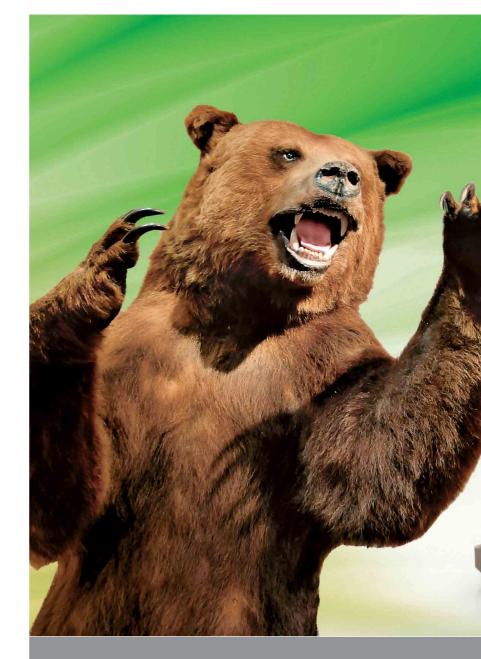

# WHITE SPACE AND THE SMART GRID

By: Alan Woolhouse

Smart Grid and Smart Home are inextricably linked for one key reason:

he data that adds intelligence to the distribution and transmission of power derives from the point of consumption—the home. Adding communications within the home to enable greater efficiency can benefit from the inclusion of the power company in the data loop.

M2M (Machine-to-machine) is typically a misnomer. Machines do not tend to talk to other machines; rather they talk to databases or similar. For example, a smart meter does not talk to another smart meter. Instead, it sends readings to a database, which the energy company uses for billing and other purposes.

Nevertheless, there are some applications that one might consider truly M2M, for example a home thermostat talking to the boiler to bring the heating on.

Figure 1: NeuINET is a production white-space radio system for M2M communication.

This is a short-range application and most approaches are based around a dedicated link, which at present, is almost always a wire between the two. Even if wireless, most would assume use of a short-range Bluetooth or Wi-Fi technology. There are compelling reasons, however, why it is better to use a longrange technology like Weightless. Our natural inclination is to view the idea of a signal from a thermostat to boiler going via a wide area network as illogical. The long journey seems unnecessary. This is based on our human perception of moving objects around rather than electrons. The overhead of a signal traveling a few miles rather than a few meters is trivial. If it were to go via a central network there would be many advantages. A process could apply intelligence in the central network. For example, if the weather forecast predicted rising temperatures, the process might delay activation of the boiler.

The homeowner could access readings while away from the home, perhaps if concerned whether a home left unattended while on holiday was freezing during an unexpected cold spell. Multiple thermostats installed around the home could give a better overall temperature assessment. Linking sensors and devices would be much simpler because it could be performed using a device like a computer or tablet, rather than trying to teach the boiler that it had a new thermostat it should listen to.

In addition to the value of adding distributed intelligence over a wide area network, and the value added to the power-generation and distribution organisation to enable it to build greater efficiency into its operations to deliver lower priced services to its consumers, there are direct tangible technology benefits to the homeowner. A short-range technology like Bluetooth may in fact prove problematic over the sorts of distances that typically separate devices that may be required to communicate within the home such as a heating system and a thermostat or a Smart Meter. Whilst most homes may already have an IEEE 802.11 network installed, changes made to IDs and passwords for routers could render important parts of the house-such as the heating-inoperable without attention to IT.

This potential weak link is unacceptable to the majority of consumers. Unexpected benefits accrue from the existence of a Weightless network in the community. Once established a wide area network has applications beyond power management and embraces other elements in the Smart Home mix including

### IT'S TIME TO BRING ANALOG **TOGETHER**.

maxim integrated.

security, fire safety, health, remote care, and convenience. The downside of the long distance link might be the cost of data transmission since the network operator would make some charge for carrying the data. For sensors that transmit relatively little data this cost is in fact very low, more than offset against savings made elsewhere as lower fuel bills resulting from more efficient control of heating or better use of lower-priced gas. Just because two parts of an application are close together, we should not immediately assume that it is best to use a shortrange wireless solution to link them up.

Weightless is a new wireless standard (see www.weightless. org) designed specifically for M2M applications. It is well suited to both Smart Grid and Smart Home applications due to its unique characteristics and is already attracting attention from both power generation and distribution organisations as well as developers of Smart Home applications and devices.

Low cost, it can be designed into many more devices than otherwise possible. Low power means that battery powered applications can be developed that will operate without maintenance or mains power for years. Lastly, it has excellent signal propagation range (several miles) and in-building penetration characteristics so it can operate reliably in any type of property, in challenging locations and terrains.

Alan Woolhouse Founder Cambridge Start-Up

#### www.cambridgestartup.co.uk

#### Editor's note:

Neul has, this year, deployed the world's first city-wide, fully functional wireless network in Cambridge, UK, using white space, an approach to wireless networking that uses licencefree TV white space spectrum within existing global TV bands. The costs of spectrum, network infrastructure, back haul, maintenance, and deployment has been minimised, allowing customers to build & operate their own Neul networks. The architecture is based on the royalty-free, open network standard 'Weightless.' The terminal BoM is less than \$5 in volume from 2012 going down to \$1/chip set by 2014. Battery life is 15 years for low bandwidth smart meters M2M apps.

#### THEY SAY:

### "ANALOG INTEGRATION CAN'T BE DONE."

# **"WEJUST**

TRANSLATION

#### IT'S TIME TO BRING ANALOG TOGETHER. www.maximintegrated.com

### DON'T REALLY WANT TO DO IT."

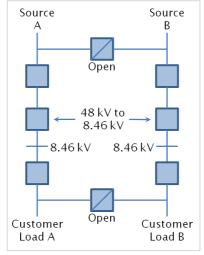

### DO RECENT WEATHER EVENTS IN NORTH AMERICA HELP THE SMART-GRID MOVEMENT?

By: Michael Markides

In late June 2012, a severe storm hit parts of the eastern US, leaving residents and businesses without power for upwards of one week (http://

yhoo.it/RjpxAn).

ver the past several vears in North America, these events seem to have become more common. or at least more visible, often leading to intense criticism directed towards the electric utilities responsible for taking too long to restore power. This latest outage left some residents without electricity during a record-breaking heat wave, with temperatures reaching above 100 °F.

Overhead power lines present a significant liability in North America, as a large violent storm can take out lines across a large service area. This leaves behind a mess for the operating utility, who must locate all downed lines and restore power, often requiring manpower beyond

what may be regularly on hand. Utilities and residents alike acknowledge that downed lines are inevitable; however, growing anger from residents is rooted in the excessive time needed to restore power, particularly during harsh weather.

New regulations, along with increased understanding and deployment of new technology are being implemented to cut downtime. IMS Research has recently published an update to its annual market study on the distribution automation market, highlighting utility investment in new technology on the medium voltage layer of the electric grid. IMS Research forecasts more of the available utility funds will be shifted towards investment on distribution automation equipment and

related platforms, with a critical portion going towards FDIR (fault detection, isolation, and restoration) schemes. Automated switches, smart reclosers, retrofit switch-control modules, and communicating fault detectors are all forecast to see increased sales globally, with the highest market volumes seen in North America.

Michael Markides, Associate Director Metering & Energy Management Group IHS

www.ihs.com

#### Does your digital power-supply design controller require high performance flexible on-chip peripherals?...

**Control complex Digital Power applications and save power**

Microchip's new dsPIC33F 'GS' Series DSCs provide on-chip peripherals including high-speed Pulse-Width-Modulators (PWMs), ADCs and analogue comparators, specifically designed for high performance, digital power supplies.

The powerful dsPIC33F 'GS' series is specifically aimed at power control applications and can be configured for a variety of topologies, giving power-supply designers the complete freedom to optimise for specific product applications. Multiple independent power control channels enable an unprecedented number of completely independent digital control loops. The dsPIC33F 'GS' series offers the optimal digital power solution supported by royalty free reference designs and advanced power design tools.

Typical applications for the new 'GS' series DSC include: Lighting (HID, LED, fluorescent), uninterruptable power supplies, intelligent battery chargers, AC-DC and DC-DC power converters, solar and pure sine-wave inverters, induction cooking, and power factor correction.

- Digital control loops with up to 18 high-speed, 1 ns resolution PWMs

- Up to 24 channels 10-bit on-chip ADCs

- 2 to 4 Million Samples Per Second (MSPS) ADC for low latency and high-resolution control

- Pin range: 18 to 64

- Up to 64KB Flash memory

#### For more information, go to: www.microchip.com/power

#### 10 WWW.POWERSYSTEMSDESIGN.COM

#### Microcontrollers • Digital Signal Controllers • Analog • Memory • Wireless

#### **GET STARTED IN 3 EASY STEPS:**

- 1. Purchase a 'GS' Series Plug-In Module

- 2. Download Digital Power **Reference Design**

- 3. Order samples and start designing! www.microchip.com/power

dsPIC33F 'GS' Series Plug-In Module (MA330024)

### INPUT IMPEDANCE **MEASUREMENTS**

By: Dr. Ray Ridley

In this third part of this series of articles, Dr. Ridley discusses the fourth important frequency-response measurement made during

full characterization of a switching power supply. The closedloop input impedance is measured to be a negative resistance at low frequencies. The input impedance of a power supply is also complicated by the inclusion of input filter parameters in most practical measurements that are made.

ower Supply Transfer Function Measurements There are four fundamental transfer functions that characterize the small-signal performance of a switching power supply. They are as follows:

- 1. Loop gain and phase determines the stability of your design, and available margin to accommodate variations in components.

- Output impedance -2. determines the output regulation, dynamic load response, and susceptibility to complex loading.

- Audiosusceptibility deter-3. mines the transmission of noise from input to output.

- Input impedance determines 4. the sensitivity of the power system to input filter or input power system components.

The first three parameters, loop gain, output impedance, and audiosusceptibility were discussed in the first two articles of this series. It is highly recommended that all three of these measurements are made on every switching power supply that you design and build. The loop measurement is essential to guarantee stability over the lifetime of the power supply, and the output impedance gives comprehensive information about the performance in the presence of load variations. The audiosusceptibility is measured is very useful for showing the rejection of noise from input

An input impedance measurement gives information about the characteristics of the power sup-

source to output.

ply input terminals. It is usually a requirement of the documentation package in the aerospace industry. As with the audiosusceptibility measurement, a signal must be injected on top of the high-power input rail. Once you have set up your test equipment to do audiosusceptibility measurements, input impedance measurements are straightforward to do.

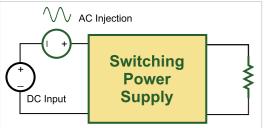

#### Input Impedance Measurements

The input impedance measurement can predict how well the power supply will integrate into a system. If the input impedance is too low, it can load down the source and provide adverse system interactions. In order to measure input impedance, a voltage source must be injected in series with the input of the power supply as shown in Figure 1.

### New! Type 947D **High Density, DC Link Capacitors**

### **DC** link power film capacitors

Next generation inverter designs for renewable energy demand reliable DC link capacitors with higher capacitance values, voltage, and current ratings. Available in new case sizes and ratings, Cornell Dubilier's Type 947D power film capacitors offer the highest bulk energy storage, ripple filtering and life expectancy for wind and solar power inverter designs, as well as electric vehicle applications. Select from hundreds of standard catalog listings, or connect with CDE engineers to develop special designs to your requirements.

For sample requests or more technical information, visit www.cde.com/psdna

#### **TYPE 947D POWER FILM CAPACITORS**

85, 90, 100 & 116 mm CASE SIZES CAPACITANCE VALUES TO 3600 µF APPLIED VOLTAGE TO 1500 Vdc RIPPLE CURRENT RATINGS TO 90 Arm

Figure 1: Input impedance is measured by adding a voltage signal at the input terminals of a power supply and measuring input voltage and input current perturbations.

input source, and will allow sufficient signal to be injected for most applications.

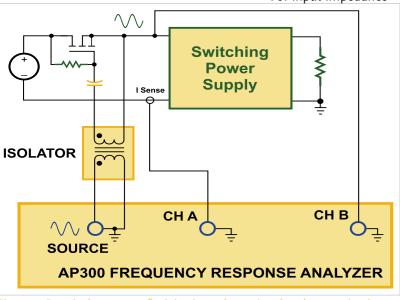

The only difference between this setup and the setup for audiosusceptibility is that the signals sent to the analyzer are different. For input impedance

Figure 2: Practical test setup for injecting voltage signal and measuring input

Figure 2 shows how this is implemented practically using a frequency response analyzer and a few discrete devices. The output of the analyzer is connected to widebandwidth isolator which is then AC coupled to a FET hooked up as a voltage follower. The size and rating of the FET may vary according to the power level and voltage level of the converter that is being driven. This injection technique is much simpler and more cost effective than inserting a highpower amplifier in series with the

measurements, Channel B of the analyzer measures the input voltage perturbation, and Channel A measures the input current perturbation. The current is measured with some kind of transducer - either a small sense resistor, current transformer, or active probe. Dr. Middlebrook, in his famous paper on input filter interactions, specified that the input impedance of a converter

should be analyzed and measured at the switching cell input. This is the point at which the interaction analysis can be properly applied to predict whether the input filter will affect the control loop. However, in most practical situations, the input impedance measurement includes some or all of the input filter components in parallel with the input impedance of the power supply. This can lead to false low measurements that are not relevant to Middlebrook's original discussions. More information on this topic can be found in [3].

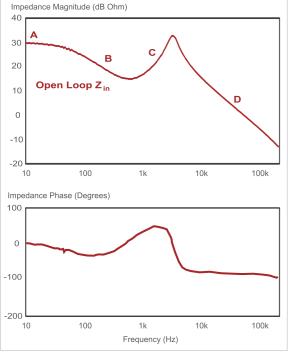

Before closing the control loop on a converter, it is useful to measure the open loop input impedance of the power supply. The results of this measurement are shown in Figure 4. There are four asymptotes to gain curve of this figure. The first, A, is proportional to the load resistance of the converter. Notice that the phase of the impedance at this point is zero degrees, denoting a positive value of resistance.

#### Just before 100 Hz, the

Figure 3: Flyback converter with input filter capacitor. In most cases, practical measurements require some input filter components to be included in the impedance measurement.

### Catch the Wave

Appliance power monitoring is the wave of the future

#### CS5484/80/90 AFEs: Energy Measurement Made Easy

Cirrus Logic's CS5484/80/90 family of analog front end (AFE) energy measurement ICs provide performance, flexibility and cost benefits for new generations of appliances when combined with your choice of MCUs. With an energy measurement accuracy of 0.1 over 4,000:1 dynamic range, the CS5484/80/90 family offers superior measurement performance with no user programming required, up to 10X faster calibration, and at the industry's lowest cost.

Stay current with innovation. Learn more and request a sample at www.cirrus.com/psde

CIRRUS LOGIC<sup>®</sup>

#### Figure 4: Open-loop input impedance measurement of a flyback converter.

asymptote B is due to the output capacitance of the power supply, and the input impedance starts to drop. This continues until to the resonant frequency of the LC filter of the power supply, and then the impedance climbs along asymptote C, according the value of the flyback inductance.

Eventually the impedance of the input filter capacitor becomes lower than the impedance of the inductor, so the final impedance follows the asymptote D. Notice that the final value of the phase of the input impedance is -90 degrees, corresponding to a capacitive value.

The open-loop input impedance is quite a complex curve, even with just a single capacitor as the input filter. With more complicated input filters

included in the measurement, the complexity of the measured or predicted impedance will increase.

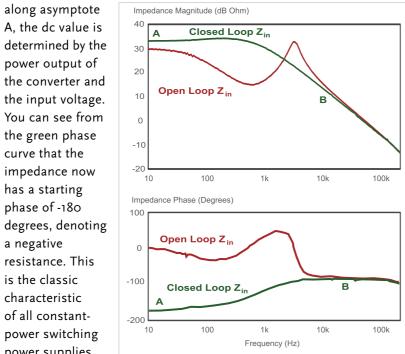

Figure 5 shows the input impedance of the same converter with the control loop closed.

The green curve of Fig. 5 shows the closed-loop input impedance of the

converter. At low frequencies,

power output of

the green phase curve that the

impedance now

has a starting

phase of -180

resistance. This

is the classic

characteristic

of all constant-

power switching

power supplies,

and it is at the

heart of the

a negative

stability problem that can arise when coupling switching power supplies with input filters.

This closed-loop input impedance stays relatively constant until the impedance of the input filter capacitor becomes lower than the starting negative resistance. The impedance then follows the asymptote B, with a 90 degree phase delay, as observed for the open-loop characteristic.

Notice that there is not the same simple relationship between the open-loop and closed-loop input impedance and loop gain that exists for the audiosusceptibility and output impedance. For these two quantities, the open-loop characteristic was attenuated

Figure 5: Closed-loop and open-loop input impedance measurements of a flyback converter.

by 1+T(s). Input impedance is different. When there is significant loop gain, the input impedance is transformed into a fixed-value negative resistance. Without any input filter components, the input impedance rises with frequency after the crossover frequency. However, as can be seen in this example, the input impedance is heavily influenced by the present of the input filter capacitor.

#### Summary

This article discusses the significance of power supply input impedance, and shows how it can be practically

Power Systems Design: Empowering Global Innovation

#### References

1. Ridley Engineering Fr Response Analyzer fro AP Instruments, www ridleyengineering.com/index. php/analyzer.html

#### **POWER SYSTEMS DESIGN SEPTEMBER 2012**

| ce          |

|-------------|

| supply      |

| ement       |

| s the       |

| ower        |

| ms. In      |

| ance        |

| ie          |

| lter,       |

| proper      |

| ok's        |

| teria. [3]. |

|             |

|             |

| equency     |

| om          |

| V.          |

2.

3.

| Ridley Engineering            |

|-------------------------------|

| Design Center, www.           |

| ridleyengineering.com/index.  |

| php/design-center.html        |

| "Power Supply Design.         |

| Volume 1: Control", by Dr.    |

| Raymond B. Ridley. Full-color |

| textbook available at http:// |

| www.ridleyengineering.com/    |

| index.php/books.html.         |

|                               |

|                               |

Dr. Ray Ridley President Ridley Engineering

www.ridleyengineering.com

### MEETING SAFETY STANDARDS FOR A/V AND IT

#### Capacitor-discharge ICs provide IEC-62368 safety-standard compliance without sacrificing standby power

#### By: Edward Ong

The convergence of consumer and information technologies has stimulated the development of new safety standards and a new approach to ensuring the safety of electronic systems.

ew components, safe-by-design, allow the system developer to address these new challenges. It is no exaggeration to state that electronics technology has undergone a revolution in recent years, resulting in products such as the smart phone. Smart phones represent the ultimate convergence of computer, communication, and consumer technologies into a single hand-held device. A similar convergence with mains-powered equipment is right around the corner: smart TVs with Ethernet connections are already capable of browsing networks and provide a gateway to streaming media services. TVs with more powerful processors become capable of delivering an internetbrowsing experience similar to that of PCs. At the same time, consumers frequently use PCs now to listen to music and watch

video clips, streamed TV shows, and movies.

These developments are being echoed by changes in the evolution of safety standards. Not so long ago the IEC (International Electrotechnical Commission) hosted several technical committees, individually covering Audio/Video, Information, and **Communications Technology** equipment, and each producing its own safety standards. As the technologies and applications continued to merge, it became clear that the duplication should stop and the different specifications should combine into one common standard. The first sectors to combine were Office Equipment (IEC 380) and Data Processing Equipment (IEC 435). This merger gave rise to the Technical Committee TC74 and the creation of IEC 60950 covering Information-Technology Equipment.

On the consumer side, Technical Committee TC92, covering

Audio, Video, and Similar Apparatus, had meanwhile developed IEC 60065, which was significantly different from IEC 60950. Combining computer and consumer sectors into a new single standard was to be much more than a merging of specifications. The new standard, IEC 62368-1, produced by Technical Committee TC 108, was based on a new principle—HBSE (hazard-based safety engineering)—covering Audio/Video, Information and Communication Technology Equipment (References 1 and 2).

#### Hazard-based safety engineering

Hewlett-Packard first formalized the principles of HBSE, which ECMA, Europe's prominent computer-industry association, subsequently introduced in an industry standard. Following HBSE, the developer first

identifies potentially hazardous energy sources then analyzes the mechanisms by which energy could transfer to the user. Finally, the developer must either reduce the potentially hazardous energy level to a noninjurious magnitude, or prevent the transfer mechanism from operating. This results in a product that remains safe under multiple fault conditions.

Engineers can always design products to provide a physical barrier between the user and AC mains supply voltages with the exception of the AC mains plug. While the appliance may seem harmless when unplugged

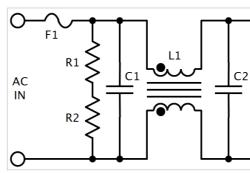

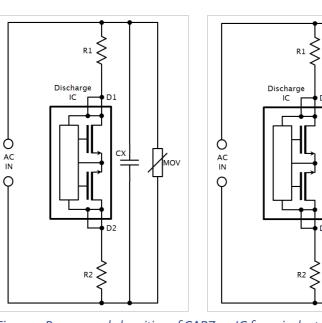

Figure 1: Example EMI filter stage of a switching power converter using a choke, two class-X capacitors (C1, C2) and discharge resistors (R1, R2).

because there are no high voltages present, the fact is, due to the energy stored in the input filter, it is still possible to get a shock.

Products that operate with off-line switching power electronics-now ubiquitous in computer and consumerelectronics equipment-have

high-voltage and highcurrent switching waveforms that generate EMI. To reduce EMI, power-supply designs include a filter stage at the AC input (Figure 1).

As part of this filter, capacitors commonly connect directly across the AC input terminals to reduce differential mode EMI. As the capacitance appears across the input terminals, a voltage, up to the peak of the across the pins of the AC plug. This could

> potentially cause an electric shock to the user if touched. To prevent this risk, safety agencies mandate that capacitance values above 100 nF discharge automatically with a time constant < 1 s when the appliance is unplugged. Typically, designs meet this

requirement by placing discharge resistors directly across the capacitor. Two resistors usually connect in series to meet safety agency single-point-of-failure testing. Should one resistor short, then the presence of the second prevents a short circuit across the AC input.

Power loss

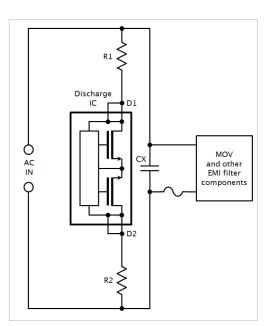

incoming AC, can appear Figure 2: Capacitor-discharge ICs like CAPZero devices connect across a class-X capacitor. A loss-of-AC detector turns the back-to-back MOSFETs on when mains power is removed.

Unfortunately, the presence of discharge resistors results in a constant power loss while AC is applied. With the stringent noload and standby input-power requirements demanded by ENERGY STAR and EuP (energyusing-products directive) Directive Lot 6, for example, this power loss represents an unacceptable portion of the overall power budget. For instance, a power supply that uses a capacitance of 1 µF across the incoming AC will require a maximum discharge resistance value of 1 M $\Omega$  which dissipates 53 mW at 230 VAC independent of the output load. Designs can eliminate this power loss by including an automatic capacitor-discharge IC such as those from Power Integrations' CAPZero family (Reference 3).

Capacitor-discharge ICs like CAPZero devices integrate a lossof-AC detector with back-to-back MOSFETs (Figure 2).

When the AC input voltage is present, the discharge IC remains in an off state, blocking current flow in the discharge path and eliminating power loss. When the AC disconnects, the device automatically turns on, connecting the resistors and discharging the input filter capacitance. The discharge IC is self-powered from the AC line with a power consumption of less than 5 mW at 230 VAC.

As the capacitor-discharge device is typically placed at the AC mains input of an appliance, it is a key contributor to compliance for equipment under the scrutiny of IEC 62368-1's approach to HBSE. In particular, no single point of failure can result in a user exposure to a hazard. The practical result of this is that the IC must continue to provide the full protection function with any single pin either open or shorted. The CAPZero IC's package and pinout design ensures compliance with this requirement for single-point-of-failure testing.

There are two dedicated pins for the D1 and D2 terminals, which add redundancy during singlepoint-of-failure testing (pinshort / pin-open testing). If one pin disconnects from the device or PCB, the IC will continue to function normally. During pin

| Class | lass Differential Common<br>Mode Surge Mode Surge |                      | Comments                                                                                                |  |  |

|-------|---------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|--|--|

|       | $Z_{OUT} = 2\Omega$                               | $Z_{OUT} = 12\Omega$ |                                                                                                         |  |  |

| 1     | No<br>requirement                                 | 0.5 kV               | Protected environment                                                                                   |  |  |

| 2     | 0.5 kV                                            | 1 kV                 | Electrical environment where cables are well separated                                                  |  |  |

| 3     | 1 kV                                              | 2 kV                 | Electrical environment where cables (power and electronic) run<br>in parallel (residential environment) |  |  |

| 4     | 2 kV                                              | 4 kV                 | Electrical environment where cables (power and electronic) run<br>in parallel (industrial environment)  |  |  |

| 5     | > 2 kV                                            | > 4 kV               | Severe surge environment (rural/sparsely populated areas)                                               |  |  |

Table 1: Surge-voltage levels (per IEC 61000-4-5).

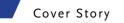

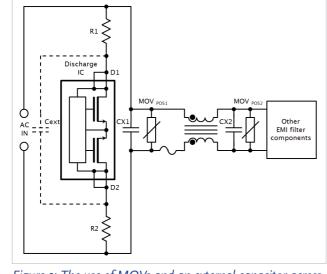

supply's AC-input design. Other components and the board layout influence the surge performance. Figure 3 indicates possible options

for the

one element

of the power

Figure 3: The use of MOVs and an external capacitor across the CAPZero device reduces voltage stress during a surge event.

shorting, the outcome is the same as if the device had not been used and simply results in the discharge resistors being connected in series continuously—a safe condition.

#### Surge severity

Another factor in HBSE is the ruggedness of the equipment to withstand damaging electrical surges. The IEC 61000-4-5 standard defines the severity of surge signals. Table 1 describes the surge-voltage levels, which depend on the power supply's operating environment. The capacitor-discharge IC is ss during a surge placement of MOVs (metal oxide varistors) and capacitors to provide the required level of

Figure 4 shows the test circuit and results for surge testing of a typical CAPZero application.

surge tolerance (Reference 4).

The waveform scales are 200 V/div, vertical and 50 µs/div, horizontal. Peaks (a) Through (e) represent the voltage measured across a CAPZero capacitordischarge IC with differentialmode input-surge voltages of 1, 1.5, 2, 2.5, and 3 kV, respectively. The MOV in this test was a 14mm 275-VAC device. Exhaustive

### It's all you need.

#### The AP300 Frequency Response Analyzer

Designed for switching power supplies, it is simply the best product on the market for all of your frequency response measurement needs.

Ridley Engineering, Inc. 3547 53rd Ave W, Ste 347 Bradenton, FL 34210 US +1 941 538 6325 Ridley Engineering Europe Chemin de la Poterne Monpazier 24540 FR +33 (0)5 53 27 87 20

EMPOWERING GLOBAL INNOVATION CHINA : NORTH AMERICA : EUROPE WWW.POWERSYSTEMSDESIGN.COM

Figure 4: Recommended position of CAPZero IC for a single stage EMI Filter (a). Waveforms show peak voltage across a CAPZero capacitor-discharge IC in the presence of an MOV (b).

testing has been undertaken using many different power supply configurations at voltages up to 6 kV, far beyond the requirements of current and envisaged standards.

#### Working to the new standard

IEC 62368-1 provides greater flexibility in deploying new technologies, but it also places new demands and a new discipline on the design engineer. The example of capacitordischarge ICs illustrates that compliance with IEC 62368-1 does not necessarily involve extra cost or compromise. The device provides the means to reduce power consumption in the input filter of a power supply while its safety features inherently support compliance to IEC 62368-1, both in new designs or as a retrofit to existing products.

Edward Ong Senior Product Marketing Manager **Power Integrations**

#### www.powerint.com

#### References:

- 1. IEC 62368-1 Technical Brief. Underwriters Laboratories Inc. 2010.

- 2. The ABCs of IEC 62368-1, An Emerging Safety Standard. Tom Burke. 2010.

- 3. CAPZero Family Zero Loss Automatic X Capacitor Discharge IC. Power Integrations Inc. November 2011.

- 4. Application Note AN-48 **CAPZero Family Design** Considerations. Power Integrations Inc. December 2011.

#### EMBEDDED

### PERFORMANCE vs POWER IN **OFF-CHIP DDR SDRAM**

#### Memory-system management reduces dissipation while meeting application-performance demands

#### By: Graham Allan

To deliver new features and higher performance in consumerelectronic products, SoC developers constantly look to integrate more functionality into their designs.

oCs with more features and performance typically operate with higher clock

frequencies, which require faster access and greater bandwidth to memory. DDR (double-data-rate) SDRAM, the most cost-effective off-chip memory, is the memory of choice to meet the increasing bandwidth needs of today's SoCs.

DDR-SDRAM subsystems offer cost and performance benefits, but higher performance usually translates to increased power consumption. Whether the design is for mobile or wired applications, it is critical that designers optimize their DDR-SDRAM subsystems to manage power consumption while maximizing system performance. Designers can build a complete DDR subsystem that balances power and performance requirements by drawing on their application knowledge and

taking advantage of available DDR SDRAM power-management features.

Issues for mobile products Power management is a primary concern in mobile-product designs because battery capacity limits the product's available source energy. The less power the product consumes, the longer it can operate before the user must recharge the battery. Even though battery technology is dramatically improving, the desire to support multi-tasking applications increases the power requirement. Multi-tasking applications demand higher bandwidth from the DDR-SDRAM subsystem, which often translates to a faster clock rate that requires more power.

Mobile products do not operate constantly, so power management targets two areas: active power (power consumed

while the product is in use) and standby power (power consumed while the product is on but inactive). Because of the sensitivity to both active and standby power, mobile products typically use low-power SDRAM such as LPDDR2 (lowpower DDR2) or LPDDR3 (lowpower DDR<sub>3</sub>). Low-power DDR SDRAM consumes less power in active mode. For example, the low-power variants forgo the common parallel termination mainstream DDR2 and DDR3 devices use. They also reduce power in standby mode by, for example, forgoing the on-chip DLL (delay-locked loop) that standard DDR memory includes.

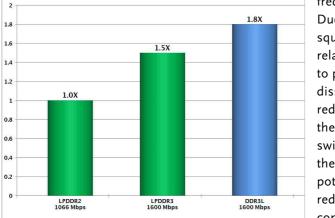

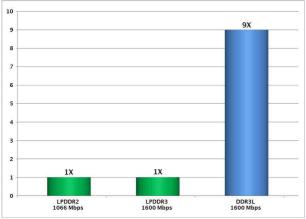

In contrast to LPDDR3 SDRAM, mainstream DDR3L memory consumes slightly more power for the same operating frequency in active mode but approximately nine times more power in standby mode (Figures 1 and 2).

#### Figure 2: Relative standby power

Between LPDDR2 and LPDDR3, several features support the low-power requirements of mobile products including low I/O supply voltage, PASR (partial array self-refresh), and deep power down. Mobile SoC developers leverage these and other LPDDR SDRAM features to minimize power in the SDRAM interface.

Low I/O supply voltage: Switching power in CMOS chips is directly proportional to CV2f where C is the capacitance of the switching node, V is the voltage swing, and f is the operating frequency. Due to its square-law relationship to power dissipation, reducing the voltage swing has the greatest potential to reduce power

> consumption. As a result, LPDDR2 and LPDDR3 SDRAMs offer a low I/O supply voltage of 1.2 V as compared to DDR3 SDRAM's 1.5

SDRAM's 1.35 V.

V or DDR<sub>3</sub>L

PASR: Because their data is stored on small capacitors, SDRAMs require periodic refresh operations to maintain their data integrity. Self-refresh is a mode that puts the SDRAM into a low-power state and the device manages its own refresh requirements to maintain data integrity without intervention from the memory controller. SDRAMs that support PASR allow the system to determine if it needs to maintain all of data stored in the SDRAM or if only a portion of the entire SDRAM needs to be refreshed. Since any refresh operation consumes power, excluding parts

of the SDRAM from self-refresh saves overall system power. Both LPDDR and LPDDR2 SDRAM support PASR.

Deep power down: Mobile products can also take advantage of the deep-power-down command in low-power SDRAMs. Designers use deep power down when the SDRAM does not need to retain its contents and when the system can handle a longer than normal activation cycle. In deep power down mode, the LPDDR SDRAM can disconnect all internal power from within the memory and will consume the least amount of power as compared to all other modes.

#### Issues for wired products

Power management is also an issue for wired systems including HD TVs, set-top boxes, computers, and other products that draw power from a wall outlet. Power consumption affects wired consumer products on two fronts: cost and conformance to national or international regulations.

To be competitive, consumer products need to be available at the lowest possible cost. Systems that consume more power often require advanced packaging to dissipate the heat chips generate and may require cooling elements such as heatsinks or fans, increasing total cost. LPDDR SDRAM is not a good option for non-mobile consumer devices because it is

| Frequency | Power<br>Reduction |  |

|-----------|--------------------|--|

| (MHz)     | (%)                |  |

| 1600      | 0                  |  |

| 1066      | 33%                |  |

| 800       | 50%                |  |

| 400       | 75%                |  |

| 200       | 88%                |  |

| 100       | 94%                |  |

| 50        | 97%                |  |

#### Table 1: Frequency reduction andpotential active power savings

more expensive compared to mainstream DDR SDRAM and it typically cannot support the performance requirements those products impose. Therefore, wired devices usually use mainstream DDR SDRAM such as DDR<sub>3</sub>.

DDR<sub>3</sub> SDRAM does not support as many power saving modes as LPDDR SDRAM because the target use model typically has not been as sensitive to power as mobile devices. In addition, DDR3 SDRAMs are often in systems with 8 to 16 SDRAMs requiring features such as onchip DLLs and ODT (on-die termination) to accommodate the large number of SDRAMs driven by one controller. DDR3 SDRAM supports both active powerdown and precharge power-down modes. The SDRAM disables its on-chip DLL during precharge power-down and consumes less power than in active power-down, which doesn't disable the DLL.

DDR power options

Although DDR SDRAM's power features can help reduce memory-subsystem dissipation, the realized energy savings typically are not sufficient to be competitive. To improve power management of a DDR subsystem further, SoC and system designers can leverage their knowledge of how their system accesses the DDR SDRAM.

Designers can apply active and standby power-management techniques to DDR SDRAM subsystems. These techniques can apply to both mobile and wired applications.

Active power management: To determine the best active powermanagement structure for a DDR subsystem, recall the switching power determined by the CV2f relationship. The capacitance is usually fixed so designers focus on how to manage the voltage, which has a squared contribution, and the frequency, which contributes linearly.

The largest consumer of active power is the I/O interface, which drives commands and data offchip during write operations, and receives data during read operations. Designers can reduce power consumption by using DDR3L instead of DDR3, which will cut the voltage from 1.5 V to 1.35 V, saving nearly 20% of the memory device's power .

In addition to I/O voltage reduction, system designs can reduce

#### POWER SYSTEMS DESIGN SEPTEMBER 2012

active power by scaling the operating frequency. Part of the drive for more performance is that consumers are demanding more capabilities in electronic products. Not all of these applications operate all the time, nor do they often operate simultaneously. Additionally, not all of the applications require the same amount of bandwidth from the SDRAM. Conceptually, designs can add intelligence to a DDR SDRAM subsystem that will manipulate the operating frequency depending on the running applications' bandwidth requirements. Through frequency scaling, a DDR SDRAM subsystem can consume less power (Table 1). Systems can implement frequency scaling in either low-power or mainstream DDR SDRAM but it is favored in low-power SDRAM due to its lack of an on-die DLL.

Standby power management: When a modern consumer product connects to its energy source, it is always consuming some power. Even if an SoC stops reading and writing data to SDRAM, it still consumes power, albeit at a lower rate. Reducing this standby power is the second type of power reduction and requires other system power-management techniques.

One technique removes the power from your chip or SDRAM interface by disconnecting the source. When power removal is a practical option, the system must be capable of controlled and

rapid power switching. In addition, the system must be able to pick up where it left off so as not to consume unnecessary time cycling through an entire power up sequence.

Features for power reduction: Certain power-reduction techniques depend on feature support in the DDR controller and PHY (physical layer). SoC designers must understand the bandwidth demands each of the IC's applications impose, and then leverage these techniques to architect a lower-power system.

For example, in frequency scaling, the DDR controller and PHY

must be able to communicate with each other to manage the frequency transitions. Likewise, when enabling system power shut down, the controller and PHY provide the appropriate handshakes to ensure the complete DDR SDRAM interface operates appropriately throughout the different modes. Therefore, not only must the DDR controller and PHY support these modes, but their implementations must be mutually compatible. This typically occurs only when the complete DDR interface IP comes from a single supplier and the memory controller can interoperate with the PHY to

optimize performance and power conservation.

A complete, integrated DDR subsystem can support other power-management techniques as well. For example, a tightly integrated DDR controller and PHY can leverage the controller's look-ahead capability to manage the PHY's power intelligently by enabling and disabling certain PHY functions and capabilities at appropriate times.

Graham Allan Senior DDR IP Product Marketing Manager

www.synopsys.com

- iMP/iVS/uMP/MP Series

- Available power from 400 4920 watts

- 60601-1 3rd Edition Compliant

#### CONTACT A POWER SPECIALIST

Contact us by phone at +44 (0) 238 062 1260 or email us at sales@peigenesis.com www.peigenesis.com/psdenpeu

### HOW HIGH-TJ TRIACS BENEFIT YOUR APPLICATIONS

#### Designers gain flexibility exploiting the benefits of hightemperature power devices

#### By: Laurent Gonthier and Martial Boulin

High-temperature TRIACs present several benefits particularly useful in applications demanding high current density or imposing high-temperature environments.

hese applications include vacuum cleaners, electric ranges, water heaters, air blowers, and small home appliances such as blenders, rice cookers, and bread makers.

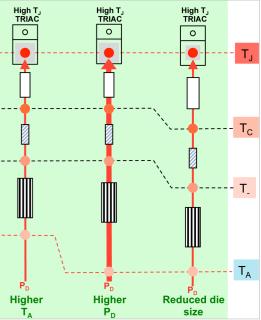

High-temperature TRIACs those that are able to work up to a TJ (junction temperature) of 150 °C—help designers design more efficient control boards by offering enhanced features compared to standard TRIACs.

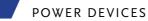

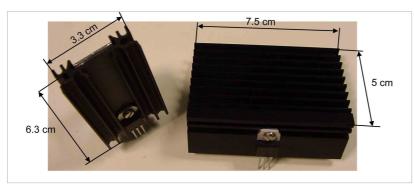

Figure 1: Two TRIACs operating near their Tj(max): The BTB16-600CW standard TRIAC (a) and the T1635H-6T hightemperature TRIAC (b).

The benefits of these hightemperature devices are evident in four cases: Applications working at elevated ambient temperatures, those without enough space for a fullsize heatsink, cost-sensitive

applications that use lowercurrent-rated TRIACs, and applications controlling a higher load current without upgrading the device rating.

#### **Higher-TA** operation

To validate experimentally that a TRIAC can operate at a higher TA (ambient temperature), STMicroelectronics engineers mounted two different TRIACs on 3.7 °C/W heatsinks. A test circuit ensured that each device dissipated the same power by applying 10-A RMS currents to both.

The engineers calculated the TA necessary to operate each TRIAC near its own maximum TJ (junction temperature): 125 °C for a BTB16-600CW sample and 150 °C for a T1635H-6T hightemperature TRIAC. Figures 1a and 1b show the temperature measurements as reported by an IR camera during the tests. They set the TA, confirmed by thermocouple measurement, at the calculated values: 80 °C for the standard TRIAC and 110 °C for the high-TJ TRIAC.

The measured values of TC (case temperature) confirmed the calculated TJ using the formula:

$T_I = T_C + P_D Rth(J - C)$

where P<sub>D</sub> is the dissipated power

$$P_D = \frac{2\sqrt{2}V_t I_{RMS}}{\pi} + R_D I_{RMS}^2$$

and Vt is the TRIAC's on-state forward voltage.

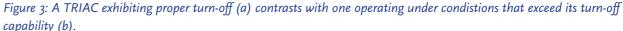

Figure 2: The heatsink-size reduction, when switching from standard to a high-temperature TRIAC, can approach 4:1.

The BTB TRIAC junction temperature was, then, TJ = 115 $+ 0.95 \times 9 = 123.5$  °C, and the T1635H junction temperature was  $TJ = 143.7 + 0.95 \times 8.7 = 152$  °C. These tests results demonstrate that the high-TJ TRIAC is able to withstand 30 °C higher TA than the standard TRIAC.

Alternatively, with these two TRIACs in the same ambient environment at 80 °C, the high-TJ TRIAC has a temperature margin of 30 °C with respect to its 150 °C maximum TJ while the standard TRIAC is already reaching is maximum TJ. This temperature margin has a direct positive effect on device reliability.

#### Heatsink size

The next test placed both previous TRIACs into an ambient temperature of 80°C with the high-TJ TRIAC on a 7 °C/W heatsink and the standard device on a 3.7 °C/W heatsink (Figure 2). With both devices conducting the same 10-A RMS current, TC measured 115 °C and 132 °C for the BTB16-600CW and the T1635H-6T, respectively. Using

previous formula, the BTB TRIAC  $TJ = 115 + 0.95 \times 9 = 123.5 \text{ °C}$  and the T1635H TJ =  $132 + 0.95 \times 9.4$ = 141 °C. Junction temperatures were below the maximum allowed temperatures for each device, but the temperature margin was better for the T1635H-6T device despite its smaller heatsink.

Designers facing size constraints can take advantage of the heatsink-size reduction achievable with a high-TI TRIAC. The heatsinks these tests used show a thermal resistance increase by a factor of 1.8, implying a heatsink-size reduction of around 4:1, which reduces costs as well.

#### **TRIAC current rating**

High-TJ TRIACs are able to drive loads at higher junction temperatures without parameter derating, so they can allow designers to specify lower current rated TRIACs in place of standard TRIACs.

For example, the STMicroelectronics engineers performed tests to evaluate a

High T<sub>J</sub> TRIAC

0

•

150°C max

125°C max

Standard TRIAC

0

- -

R<sub>th(jc)</sub>

R<sub>th(interf)</sub>

R<sub>th(heatsin</sub>

12-A high-TJ TRIAC (T1235H-6T) replacing a 16-A standard TRIAC (BTB16-600CW). They mounted both devices on 3.7 °C/W heatsinks and applied the same 10-A RMS load to both.

Measurements of the BTB16-600CW revealed a TC of 115 °C while dissipating 9 W

in an 80 °C TA. Corresponding measurements of the T1235H-6T indicated a TC of 144 °C while dissipating 9.3 W in a 105 °C TA.

The BTB TRIAC junction temperature was 123.5 °C and the T1235H junction temperature was 154 °C—slightly above maximum allowed temperature but not

#### Reduced heatsink Figure 4: Benefits of high-TJ TRIACs critically so for experimental purposes. These results clearly shows an advantage to high-TI TRIAC since the TA can be set 20°C higher (or 16°C if one wants to keep T1235H-6T TJ below 150°C) than for a standard TRIAC.

#### Higher TRIAC current

The engineers mounted two

#### **POWER SYSTEMS DESIGN SEPTEMBER 2012**

16-A TRIACs (BTB16-600CW and T1635H-6T) now on two identical 3.7 °C/W heatsinks and put them into the same 80 °C ambient temperature. This test increased the load current until each TRIAC was operating at its own maximum allowed junction temperature. For the BTB16-600CW, that applied RMS current was 10 A, at which point

the device dissipated 9 W and its TJ was 125 °C. For the T1635H-6T, was able to pass 14 A, dissipating 14.59 W with a TJ of 148 °C.

One key parameter in the choice of TRIACs operating at a high TJ is the turn-off capability the ability to remain in the off state even in the presence of a fast voltage excursion after the current has fallen to zero. The turn-off constraint is higher with inductive loads due to the current-voltage phase shift and thus the high dV/dt occurring at TRIAC turn-off.

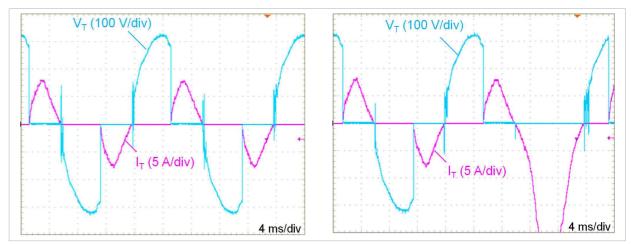

Figure 3a shows an application example where a TRIAC in phasecontrol mode is properly driving a universal motor. The load current (pink waveform IT) goes to zero at each half cycle and remains at zero.

Figure 3b, by contrast, shows another TRIAC under the same drive and load conditions. This device loses control of the load because the operating conditions exceed its turn-off capability at high TI: The high level of the load current during the negative half period shows that the load remains energized even when the TRIAC's drive is off.

Compared to standard TRIACs (T][max] = 125 °C), hightemperature TRIACs (T)[max] = 150 °C) provide significant benefits such as reduced heatsink size, higher TA working capability, higher load-current capability (higher power-dissipation capability), or smaller-current rated device selection potential, reducing die size and cost (Figure 4).

Laurent Gonthier and Martial Boulin Application Development Managers ST Microelectronics

www.st.com

### www.apec-conf.org

#### MEASUREMENT

### **INTEGRATED CURRENT** SENSING

#### Simple two-chip method results in ultra-low-loss measurement

#### By: Ann Starks

#### Competitive markets put pressure on OEMs to improve energy efficiency in their product designs.

ccordingly, it is important to be able to monitor accurately currents through critical paths to support power-management and systemperformance optimization. There are several different currentmonitoring methods in current use. However, each of these common methods has distinct disadvantages. The need for a precision current-sense method has led to the creation of an integrated two-chip approach that provides accurate, ultralow-loss current sensing with minimum affect to PCB layout and component count.

#### **Existing Current Sense Techniques**

The conventional current sensing method uses a precision sense resistor in the path of the subject current. A measurement of the voltage drop across the precision resistor allows a calculation of the current through the resistor. However, this method can incur significant power losses, especially at high currents. Other common

current sensing techniques include the use of MOSFET RDS(on), inductor ESR, inductor voltage, or a current transformer.

MOSFET RDS(on): Using the MOSFET on resistance eliminates the need for additional components, but the RDS(on) exhibits unit to unit variations, and the on-resistance value changes over temperature with up to a 35% difference in on-resistance from 27 to 100 °C.

Inductor ESR: The inductor's ESR (equivalent series resistance) can sense the load current. A simple low-pass RC network filters the voltage across the inductor ESR. This method depends on known inductor characteristics to be effective, however. Inductor partto-part variations can be as much as 20%.

Inductor Voltage: This method measures the inductor voltage and calculates the current using Equation 1. The inductance can vary by 20% or more from part

to part, limiting this method's accuracy. (eq 1)

$$V_L = L \frac{dI_L}{dt}$$

Current Transformer: Most commonly used in high power systems, this method uses a current transformer to sense a fraction of the inductor current. This method is expensive to implement, however, and the transformer occupies considerable board space.

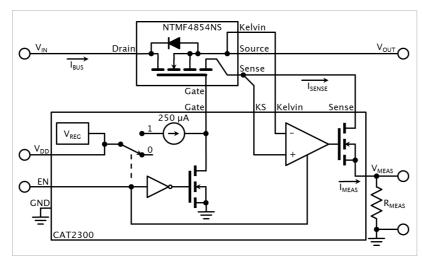

#### SENSEFET current sensing

The new ultra-low-loss measurement method uses a single MOSFET die, which features a small number of isolated source cells that connect to a separate sense pin, creating a matched internal mirror MOSFET. The ratio of source cells to sense cells is large. When current flows through the main MOSFET, a proportionally smaller current passes through this mirror MOSFET. The relationship between the two currents is IRATIO-the current ratio—and is defined in Equation 2.

A typical IRATIO value is 400. The measurement circuit must hold the source and sense terminals at the same potential for the IRATIO to remain a known constant. (Eq. 2)

$$I_{RATIO} = \frac{I_{SOURCE}}{I_{SENSE}}$$

The main MOSFET and mirror MOSFET share common gate and drain connections, but have separate sources. A Kelvin connection to the main MOSFET source provides the means to monitor the source voltage without affecting its value. This single-die MOSFET allows for ultra-low-loss current monitoring by measuring the small current flowing through the mirror device. The measurement minimally affects system efficiency because it takes place outside the main current path: A typical value of ISENSE is 1/400th of ISOURCE. Accordingly, it's possible to measure the sense current and accurately calculate the load current. On Semiconductor calls its single-die mirror MOSFETs SENSEFETs.

For example, one implementation of this precision, ultra-low-loss current-sensing method uses a SENSEFET and SENSEFET controller (Figure 1). The CAT2300 IC is a SENSEFET controller and current monitoring device for load switch applications. It can monitor load currents from 1 to 25 A for power supply rails ranging from 0.9 to 1.5 V. It serves the dual purpose of ultra-low-loss current sensing and controlling the SENSEFET's on-off state.

Figure 1: Current-measurement circuit

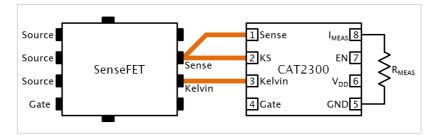

#### Figure 2: PCB trace connection of Sense & KS signals

The CAT2300's logic-level EN pin controls the SENSEFET gate. A logic-high or -low amplitude turns the SENSEFET on or off. Add a pull-up resistor between VDD and gate to speed the turn-on time. Alternatively, add a capacitance between gate and source to gain a softer turn-on.

The current-sense circuit consists of an amplifier with a MOSFET follower stage. The Kelvin signal serves as a voltage reference, and the operational amplifier and follower stage accurately track the sense current by holding the Sense terminal at the same potential as the Kelvin terminal. An additional KS (Kelvin Sense) pin is included in the CAT2300 design as a connection for the mirror MOSFET source (the Sense pin), in order to eliminate any voltage drops in the PCB's sense trace.

For a true Kelvin connection, the KS trace must be a dedicated connection, completely separate from the Sense trace and must begin directly at the Sense pin (Figure 2). Good layout practices are important to minimize loss in the PCB traces. Ideally, the layout design locates the CAT2300 as close to the SENSEFET as possible, keeping PCB trace lengths short and using proper Kelvin connections. On Semiconductor recommends a PCB with a separate ground plane.

An external resistor, RMEAS,

Tickets & Registration: www.electronica.de/en/2012

ee

e

#### electronica 2012 inside tomorrow

25th International Trade Fair for Electronic Components, Systems and Applications Messe München November 13–16, 2012 www.electronica.de

between the CAT2300's IMEAS pin and ground produces a scalable voltage that is proportional to the sense current flowing through the mirror MOSFET. VMEAS as a function of RMEAS is: (Eq. 3)

$$V_{MEAS} = I_{SENSE} \times R_{MEAS}$$

Combining equations 2 and 3 gives the load current: (Eq. 4)

$$I_{LOAD} = I_{RATIO} \frac{V_{MEAS}}{R_{MEAS}}$$

**Measurement Resistor Selection** The value of RMEAS depends on several factors, including the application's voltage rail and load current range. Equation 5 describes the maximum value for RMEAS in a given application. VK is the SENSEFET Kelvin terminal's voltage and IMAX is the application's maximum load current. The SENSEFET device's datasheet specifies IRATIO. (Eq. 5)

$$R_{MEAS}\big|_{MAX} = \frac{V_K\big|_{MAX} - 0.1}{I_{SENSE}} = I_{RATIO} \frac{V_K}{V_K}$$

As an example, assume a circuit that uses the ON Semiconductor NTMFS4854NS SENSEFET in a 1.5-V power rail, with a maximum load of 10 A. You can estimate VK at maximum load current using the maximum RDS(on) value in the SENSEFET datasheet: (Eq. 6)

$$V_{K}\big|_{MAX} = V_{IN} - I_{MAX} \times R_{DS}(on)\big|_{MAX}$$

The NTMFS4854NS has a typical IRATIO of 399 and a maximum RDS(on) of 3.9 m $\Omega$  at VGS = 4.5 V. Using Equation 6: VK = 1.5 V $-(10 \text{ A})(3.9 \text{ m}\Omega) = 1.461 \text{ V}$ . Therefore, the maximum voltage at the CAT2300's IMEAS pin is approximately 1.361 V at a 10-A load current.

Calculate the maximum value of RMEAS by combining Equations 5 and 6: (Eq. 7)

$$R_{MEAS}|_{MAX} = I_{RATIO} \frac{V_K|_{MAX} - 0.1}{I_{MAX}} = 399 \times \frac{(1.461 - 0.1)V}{10 \text{ A}} = 54.3$$

To get the best measurement results across the input voltage range, select a resistor value for RMEAS that produces 0.8 V on the CAT2300's ISENSE pin at the maximum load current: (Eq. 8)

$$R_{MEAS} = I_{RATIO} \frac{V_{MEAS}}{I_{LOAD}} = I_{RATIO} \frac{0.8 \text{ V}}{I_{LOAD}}$$

To obtain 0.8 V on VMEAS at full load for this example, RMEAS becomes: (Eq. 9)

$$R_{MEAS} = 399 \times \frac{0.8 \text{ V}}{10 \text{ A}} = 31.9 \text{ G}$$

To obtain the best measurement accuracy, choose a resistor with a tolerance < 1%.

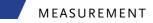

$$\frac{V_K|_{MAX} - 0.1 \text{ V}}{I_{MAX}} \quad \begin{array}{l} \text{Figure 3 illustrates} \\ \text{measured IRATIO} \\ \text{for a load switch} \end{array}$$

Ω loses accuracy for currents below 1 A due to the input offset voltage of the CAT2300's internal operational amplifier. The Source and Sense terminals operate at the same potential to have a constant IRATIO. The input offset voltage of the operational amplifier creates a voltage difference between the two

terminals, introducing measure-

ment error that is most prominent

application with a load current

range of 1 - 10 A using the two-

1. As can be seen, the IRATIO is

virtually flat across the load cur-

rent range. The measured IRATIO

chip measurement circuit of Figure

Ann Starks **Applications Engineer** ON Semiconductor

for currents below 1 A.

#### www.onsemi.com

Figure 3: IRATIO vs ILOAD (1 A to 10 A)

### **NEW POWER ELECTRONICS BASED ON GAN MISHEMPTS**

#### GaN-on-Si may hold the key

POWER DEVICES

GaN appears to be a highly suitable material for power switching devices operating at high frequencies without suffering major losses.

he Promise of GaN This is due to the drastically lower on-state resistance of GaN power transistors, combined with considerably reduced input and output capacitances. The higher switching frequency substantially reduces the volume of accompanying passive components such as inductors, transformers, and capacitors.

Thus, a GaN-based power system is smaller and more lightweight than MOS- or IGBTbased systems. Eventually, GaN power electronics will combine these significantly improved operational properties with lower costs. Active components limit the efficiency of present systems.

Converting GaN's potential into success hinges on scaling production to larger wafer sizes and employing appropriate passivation techniques. There

is a tremendous opportunity for substantially lowering the energy losses associated with AC-DC and DC-DC conversion. If a new generation of devices can combine higher power levels with lower switching losses at higher operating frequencies, they will boost the efficiency of power systems, while trimming size and weight.

#### Making Nitrides Affordable

As wide-band-gap semiconductors, GaN-on-silicon devices belong to a superior class of materials: One of their biggest advantages is their high breakdown voltage, which stems from a breakdown field strength that is an order of magnitude higher than that of silicon. Due to the high carrier mobility and concentration associated with the 2DEG (two-dimensional electron gas) of the AlGaN/GaN heterostructure, nitride devices in switching applications also combine a low on-resistance

with high switching speed. Additionally, their wide-bandgap properties enable them to operate at high temperatures.

Development of nitride power devices has been underway for more than a decade, and their progress has enabled today's switching devices to outperform their silicon rivals. In the performance stakes, SiC is a tougher opponent, but GaN more than holds its own.

GaN-on-silicon is the most cost-efficient wide-bandgap technology. It has developed to a point where it is feasible to deposit advanced heterostructures on silicon substrates up to 150 mm in diameter. In the near future, this will extend to 200 mm. There is also an opportunity to develop process compatibility with standard CMOS technology. This would open the door for further cost reduction by using existing

lines at 200 mm silicon fabs operating around the globe.

No wonder GaN powerelectronics technology is attracting increasing interest. Until very recently, no one was able to achieve a real breakthrough—a reliable device operating at 600 V. This, however, is beginning to change. There have been demonstrations earlier this year of fully qualified 600 V GaN switches and they are slowly finding their way into commercial equipment. Cost, of course, is still an issue, but this reflects the typical learning curve that all novel technologies must undergo.

One of the technical—and economic-challenges is to establish a compoundsemiconductor technology in a field where silicon dominates. Although the performance of SiC diodes is attractive for power converter manufacturers, they are too pricey. In addition, until recently these diodes could not pair with SiC transistors, which had been detrimental to the uptake of this firston-the-market wide-bandgap technology. For GaN technology to be commercially attractive, 600 V devices must be reliably producible on GaN-on-silicon epitaxial structures.

#### Taking out the Strain

EpiGaN's epitaxial growth process tackles the grid strain that arises in processes that

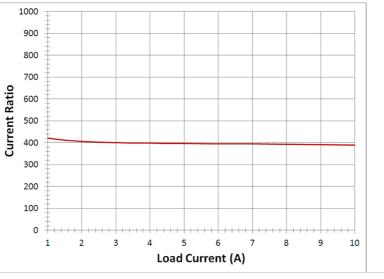

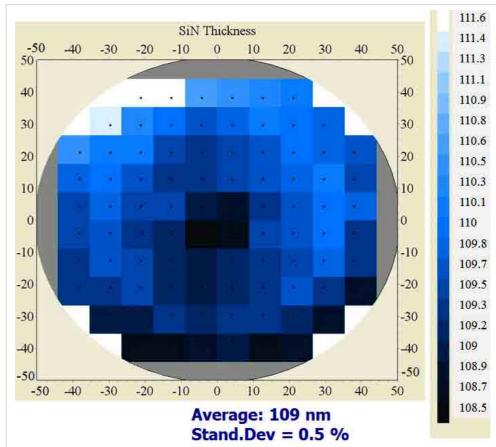

Figure 1: EpiGaN deposits a unique in-situ SiN capping layer, grown by MOCVD on top of HEMT epi wafers.

deposit GaN on silicon. The two materials show different crystalline properties and thermal expansion coefficients. Left unchecked, this can lead to unchecked strain in the epi layer and substrate that can ultimately cause the wafer to bow and even crack.

Carefully managing this strain yields wafers suitable for regular silicon processing lines. The company now routinely manufactures 150 mm epi wafers with a bow well below 50  $\mu$ m typically 20 to 30 µm, depending on wafer specs. Uniformity, in terms of standard deviation of either layer thickness or electrical characteristic, is typically better than 3%.

The process optimizes these epi wafers for high-voltage highfrequency operation, which requires the formation of a buffer layer that withstands high voltages. This is because, in devices formed with high-quality GaN layers, the silicon substrate limits the upper breakdown voltage. EpiGaN's epi wafers for high-voltage devices show a buffer leakage current well below 1 µA/mm at 600 V. Operating frequencies above 100 GHz are possible due to the reduction of buffer traps.

Stress engineering certainly is a challenging aspect of forming GaN-on-Si. Even more challenging is the passivation of surface states. A piezoelectric

#### Figure 2: The uniformity of the in-situ SiN layer

material, GaN has an excellent high-electron concentration associated with high electron mobility—obtained without extra doping.

The price to pay is an extreme sensitivity governing device characteristics, such as current density and threshold voltage on the filling of those surface states, which have a density comparable to that found in the channel. If passivation is poor, the device's dynamic behaviour suffers. To combat this so-called dispersion problem, fabricators must process devices in a carefully controlled manner using high-

quality epi wafers, because this leads to optimized buffers and controlled surface states. Uncontrolled charging or discharging of these surface states, which processing and device operation can modify, can severely degrade the device's dynamic properties. As a countermeasure, EpiGaN deposits a unique in-situ SiN capping layer, grown by MOCVD (metalorganic chemical vapour deposition ) as part of the epitaxy process on top of HEMT (high electron-mobility-transistor) epi wafers (Figure 1). The interface between this capping layer and the top nitride surface

#### **POWER SYSTEMS DESIGN SEPTEMBER 2012**

is incredibly smooth, and it enables excellent passivation of surface states. Many processes use a GaN capping layer, which is less sensitive to the formation of these surface states than the AlGaN barrier in combination with PECVD (plasma-enhanced chemical vapor deposition) SiN that deposits after the MOCVD process as part of the device processing. However, this approach does not have the advantages of the

in-situ deposited SiN.

The capping layer can properly control surface-state filling during device operation. It is believed that SiN can provide enough charge to neutralize the surface charge of the AIGaN barrier layer so that its surface potential no longer contributes to 2DEG depletion. In addition, the SiN layer aids device stability at elevated temperatures.

In-situ deposited SiN films can also lead to lower channel resistance. This enables adjusting the top part of the FET so that it can meet particular

device specifications. GaN FETs are lateral devices, and optimizing their performance demands a trimming of conduction losses. This means that, for switching applications, aluminum-rich barriers are preferred in a typical AIGaN/ GaN structure, because it yields a higher piezoelectric field, higher current density, and lower specific on resistance.

One of the major benefits of the SiN cap layer is that it enables higher aluminum concentration without any significant material degradation. This is not the case in transistor structures with an uncapped or GaN-capped Al-GaN/GaN 2DEG, where relaxation of the strained top AIGaN layer typically prevents high aluminum content in the top layer.