Current Multipliers: The Obvious Choice for Powering AI Processors and Other Demanding Applications

High current density low profile power modules exceed next generation system requirements

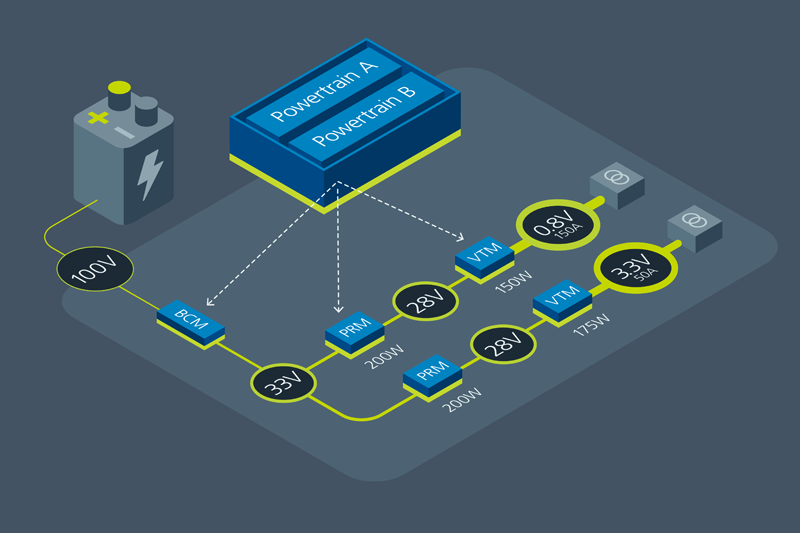

Figure 1: Conventional Intermediate Bus Architectures use a fixed-ratio isolated bus converter (IBC) to step down 48V to a 12V intermediate rail, which then feeds niPOL converters

AI processors can draw up to thousands of amps while operating at voltages well below 1V. This current demand is unprecedented and has turned the power delivery network (PDN) into a major system bottleneck.

With every amp pushed through PCB or substrate copper power planes, conductive losses and, thermal management challenges increase, and bypass capacitance must increase to keep transients in check. Conventional voltage averaging-based architectures, such as Intermediate Bus Architecture (IBA) and multiphase buck regulators, were sufficient when loads were modest, but they’re no longer congruent with today’s sub-1V, kilo-amp requirements. For these low-voltage, high-current applications, current multiplication is a higher performance route than voltage averaging topologies.

Vicor Factorized Power Architecture (FPA) embodies the current multiplication paradigm by rethinking where voltage regulation and conversion occur to optimize high power PDNs. For the most demanding applications, FPA leverages the concept of current multiplication at the point of load, providing a level of efficiency, current density, low noise and load transient response that conventional multi-phase approaches simply can’t match.

Evolution of power delivery architectures

Power delivery has gone through several architectural evolutions as system requirements have scaled throughout recent history.

The earliest approach, centralized power architecture (CPA), generated all voltages from a single supply and distributed them across the board. While workable in lower-power systems, CPA became untenable when loads began requiring an array of lower voltages and higher currents. Namely, distribution losses across long copper traces decrease system efficiency and cause excessive heat.

Distributed power architecture (DPA) was the next stage. Here, designers placed modular “brick” converters near individual loads to reduce conduction losses and improve flexibility. The DPA approach resolved some of CPA’s inefficiencies but consumed large board areas and struggled to meet fast transient requirements.

Intermediate bus architecture (IBA) attempted to balance efficiency and cost. In IBA, an isolated bus converter stepped down 48V to 12V, where the Intermediate Bus Converter (IBC) could be a fixed ratio type with step down ratios of ¼, 1/6 or 1/8 dependent on the preferred intermediate bus arrays of non-isolated point-of-load (niPOL) converters. (Figure 1). This reduced the duplication of functions and initially improved system economics. However, multiphase buck converters used in niPOLs (non-isolated point of loads) faced duty cycle limitations when stepping from 12V to less than 1V, which limited efficiency and transient performance. As load currents rose into the hundreds of amps, the systems needed large bypass capacitance to stabilize voltage rails. Size and cost suffered.

The scaling limits of IBA made clear that simply refining conventional architectures was not enough. Meeting kilo-amp level requirements required an entirely new strategy that could regulate at higher voltages and then transform voltages and multiply current directly at the point of load.

Notably, all of these architectures were based on principles of voltage averaging, where the intermediate bus is stepped down to a fixed voltage and subsequent converters time average that voltage below 1V.

The power of current multiplication and factorized power

For low-voltage, high-current applications, current multiplication has significant advantages over voltage averaging. Current multiplication delivers high current directly to the point of load while keeping the PDN at a higher voltage and lower current, thereby minimizing I2R losses and improving overall PDN efficiency.

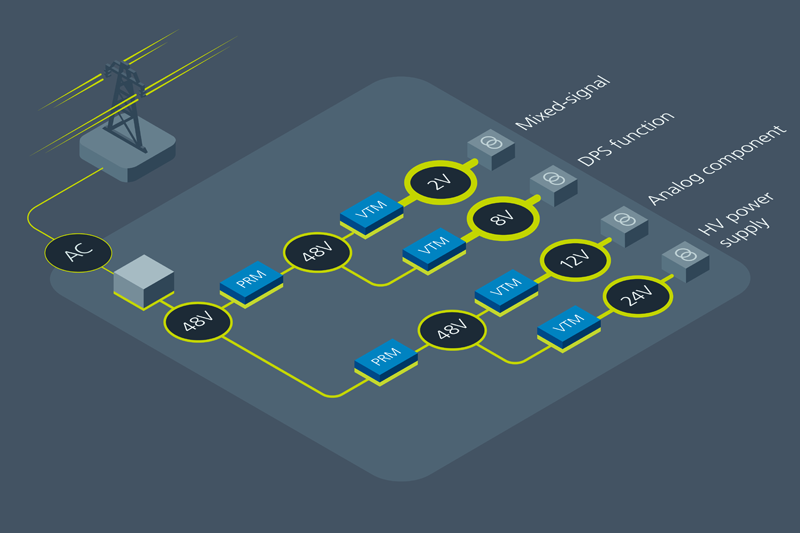

Factorized Power Architecture introduces a completely new way to achieve current multiplication for power-hungry electronic systems. Instead of combining all conversion and regulation functions at the point of load, FPA separates or factorizes these stages into two distinct power modules functions to optimize current density, efficiency, and low noise performance (Figure 2).

The first stage is the Pre-Regulator Module (PRM), a zero-voltage-switching buck-boost regulator. The PRM produces a tightly regulated “factorized bus” voltage that is set based on the chosen downstream Voltage Transformation Module (VTM) conversion ratio. For example, if the target load voltage is 0.9V and the selected VTM has a K-factor of 1/48, the PRM has its output adjusted (set) to approximately 43.2V. In this way, the PRM guarantees delivery of the exact voltage required at the load, all while operating with peak efficiencies approaching 99%.

Click image to enlarge

Figure 2: In a Factorized Power Architecture, the PRM regulates the factorized bus voltage, while the VTM delivers fixed-ratio conversion and current multiplication at the point of load

The VTM is a fixed-ratio sine amplitude converter that performs the transformation and current multiplication at the point of load. Functionally similar to a DC-DC transformer, the VTM steps down the regulated bus voltage while proportionally increasing current. In the example of a 1/48 ratio, one amp entering the VTM at 48V produces 48A at 1V. With efficiencies up to 97%, sub-microsecond transient response, and extremely low output impedance, the VTM reduces the need for large banks of bypass capacitors.

Taken together, these advantages make FPA denser, faster, and more efficient than any conventional power delivery scheme.

Current multiplication is designed for high-performance computing

High-performance computing platforms are among the most demanding environments for power delivery, as modern computing platforms often draw between 500 and 2000A at extremely low voltages. Attempting to deliver this current across a motherboard using conventional schemes often leads to unacceptable conduction losses, excessive voltage droop, and thermal hot spots in PCB copper planes.

Factorized Power Architecture solves this by moving regulation upstream and placing current multiplication at the processor package itself (Figure 3). A PRM regulates the appropriate factorized bus voltage, typically near 48V, and distributes it across the PDN at relatively low current. VTMs located adjacent to the processor convert the factorized bus to the sub-1V operating rail while multiplying current to the hundreds or thousands of amps required. Close placement reduces distribution losses, minimizes inductance, and ensures that the processor receives clean, stable power.

Click image to enlarge

Figure 3: For High Performance Computing, the VTM is placed directly under the processor to deliver high current vertically. By multiplying current at the point of load, FPA minimizes distribution losses and provides stable sub-1V supply rails

Transient response is equally important. AI and HPC workloads cause rapid current swings as xPU cores activate and deactivate. VTMs respond in less than one microsecond (typically 400ns) to supply current instantaneously without the need for oversized capacitor banks. This results in improved computational stability and power utilization efficiency.

FPA is ideally suited to Vertical Power Delivery (VPD) configurations as the current multiplier VTMs are very thin and their packages possess low thermal resistance. They also have a high current density, so fewer VTM components are needed to power high performance processors as compared to alternative solutions. This allows the current multiplier VTMs to share the space under the processor with the reduced-sized decoupling capacitor bank.

For many system architects, FPA is the ideal power delivery solution for HPC because it directly addresses the scale, speed, and density challenges that define the market requirements.

NewSpace embraces the benefits of current multiplication

Power delivery networks for low and medium-Earth orbit (LEO/MEO) satellites need to balance efficiency and low noise with resilience against radiation and thermal cycling. Payload electronics (e.g., networking ASICs and FPGAs) require multiple sub-1V and low-voltage rails at high current, all within mass and volume budgets that leave little margin for oversized power hardware. Conventional architectures, with their large copper planes and bulky capacitance, simply can’t scale to meet these requirements.

FPA offers a different approach. A 100V bus from solar arrays or batteries is converted by a fixed ratio bus converter, a BCM, to 33V (Figure 4). Buck/Boost PRMs regulate this intermediate voltage to precise factorized buses, while VTMs located next to the digital electronics step down the bus voltage and multiply current to the required rails. By transforming current at the load, FPA minimizes distribution losses and improves power density.

Click image to enlarge

Figure 4: Factorized Power Architecture (FPA) factorizes power from the traditional single-function DC-DC converter into two distinct functions and power modules: a pre-regulation module, a PRM and a voltage transformation module, a VTM. The power switching topologies and control systems of each module are optimized for low noise and power losses, with zero-current and zero-voltage switching

A satellite power delivery network built on FPA should also incorporate redundancy and radiation tolerance to bolster reliability. For example, power modules with dual powertrains can provide continuous operation should one path fail, while rad-tolerant, soft-switching designs can help mitigate single-event effects that are common in orbit. Vicor is the only company currently providing radiation-tolerant current multiplication modules with these features and level of performance.

ATE pushes new limits of throughput with current multiplication

Automated test equipment (ATE) is another domain where FPA has been proven to excel. In these cases, test heads used to validate semiconductors are expected to source more than 100A with extremely fast current slews around 7.5A/µs and operate with very low noise specifications. Conventional multiphase buck converters cannot sustain such rapid transients without relying on heavy banks of bulk capacitors that limit how many devices can be tested in parallel and drive up overall system cost. They are also very noisy.

Factorized Power Architecture delivers a more effective approach (Figure 5). A PRM regulates upstream at a higher voltage and distributes this output to the factorized bus across the test system. VTMs located close to the test sockets step the bus voltage down and multiply the current directly at the point of load. Because the VTM is a fixed-ratio converter with no control loop delay, it responds to sudden current demands in less than one microsecond and allows the tester to supply precise currents without relying on oversized capacitance.

Click image to enlarge

Figure 5: In automated test equipment, multiple PRMs regulate the 48V input bus, while VTMs at each load socket transform the regulated bus and multiply current locally

FPA also performs capacitance multiplication, where capacitance on the VTM input is reflected to the VTM output multiplied by the square of the K-factor. With less physical capacitance needed, designers can make test heads lighter and more compact. Through accurate, stable, and rapid delivery of high current, FPA improves throughput in semiconductor validation and allows operators to test processors, FPGAs, and ASICs under realistic dynamic conditions.

Today’s most demanding applications require a current multiplication approach

For low voltage, high current applications, a current multiplication approach is the logical choice when designing a high performance PDN. Vicor Factorized Power Architecture has proven to be the best choice for today’s most demanding power systems designs. FPA delivers power density, responsiveness and flexible design options. As system complexity and current demands continue to rise, the shortcomings of traditional voltage averaging architectures will become even more pronounced. FPA current multiplication provides a proven path forward that unlocks more efficient, power-dense, and scalable power delivery.