Empowering battery-free devices

Eliminating device power requirements with sub-threshold design

There are many factors driving an increased interest in low power semiconductor solutions. Battery-powered products and Internet of Things devices need to ensure a long lifetime to be of use in the consumer markets they target. Energy-harvesting modules, as an alternate source of energy, tend to provide either low amounts of power or power in short bursts. It is probably fair to say that power efficient design today has become more important than the push towards sheer performance as seen in the 1990s. So what options are available to those seeking to achieve the goal of reduced energy consumption?

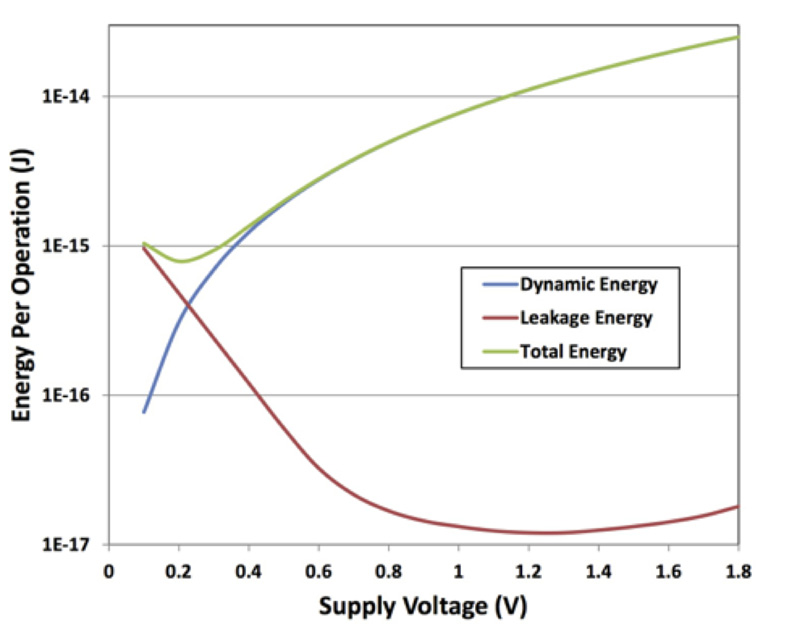

Energy in a CMOS circuit is consumed in two different ways; as leakage or static energy loss when the circuit's state isn't changing, and dynamic energy consumption as the internal nodes are charged and discharged (see Figure 1). Because dynamic energy varies as the square of the operating voltage, that voltage becomes the most important lever for reducing energy consumption. Using, as an example, off-the-shelf semiconductor devices, such as microcontrollers (MCU), it is of course possible to make some high-level design decisions to ensure optimal energy consumption.

Click image to enlarge

Figure 1 – Dynamic current dominates with higher operating voltage

Lowering the input

Reducing the supply voltage has by far the largest impact on dynamic energy consumption of CMOS circuits (the dominating mode of operation), followed by reducing the device's clocking frequency, but both are highly dependent on other components to which the device is connected as part of a larger electrical circuit. In order to improve total energy consumption, most MCU vendors will implement various switching strategies allowing unused or little-used modules to be shut down, put to sleep, or allow them to be clocked from a lower frequency clock signal.

This tinkering at block level to add energy saving functions can only go so far and at some point it is time to take a look at the underlying design of the transistors themselves. In this case, Ambiq Micro has taken on this challenge by making significant advances in sub-threshold circuit design – that is, operating the transistors of a circuit at and below the transistor's Vth.

The energy-saving results of this technology speak for themselves. For example, when compared to a typical circuit operating at 1.8V, a “near-threshold” circuit operating at 0.5V can achieve a dynamic energy improvement of up to 13X. By applying a more aggressive “sub-threshold” design strategy, the same circuit operating at 0.3V can yield a 36X improvement. Leakage losses also have a tangible impact on total energy consumption, but the effects of changes in supply voltage are not as dramatic. Thus, it was back in 2004 that Ambiq Micro decided to take on exactly this challenge with their research into sub-threshold design at the University of Michigan.

Watchmaker tech

Operating transistors sub-threshold is not a new technique. Swiss watchmakers and RFID tag manufacturers were using this technology as far back as the 1970s. The key challenge that held back wider adoption was the need to hand-optimize the few critical transistors needed to achieve low power in the design. Thus, sub-threshold design was typically limited to 10s of transistors within a larger design. Without libraries of functional cells based upon the technology, optimized for commonly available commercial manufacturing processes, and implementation of those libraries into of-the-shelf design tools, sub-threshold transistor based designs could never really catch on.

If sub-threshold transistor design can offer such a radical improvement in power consumption, it begs the question “why has this not been done sooner?”. There are significant challenges around using transistors in this manner, but fundamentally the key reason has been that no-one, until now, had undertaken the massive task of characterization needed to make the technology usable.

The key areas of focus during the period of research were as follows:

• Poor transistor models – since transistors have been primarily used super-threshold, transistor models are very accurate in this zone of operation. However, the sub- and near-threshold performance has never been characterized to the same degree of accuracy. Much of the research went into detailing the performance of devices in this critical 0V to Vth region.

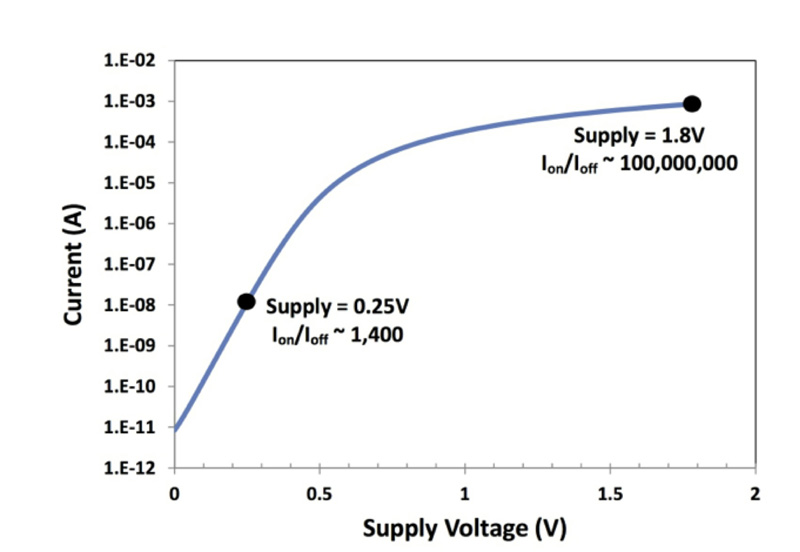

• Logic swings and noise – the output response of a transistor in the sub-threshold region is subtle and detecting it reliably requires great sensitivity. When compared to super-threshold transistors, the ratio of “on” to “off” current in sub-threshold transistors is on the order of 1000 lower – a significant challenge in itself (see Figure 2). The task of detecting logic swings becomes even more difficult when noise from external sources is mixed into the equation.

Click image to enlarge

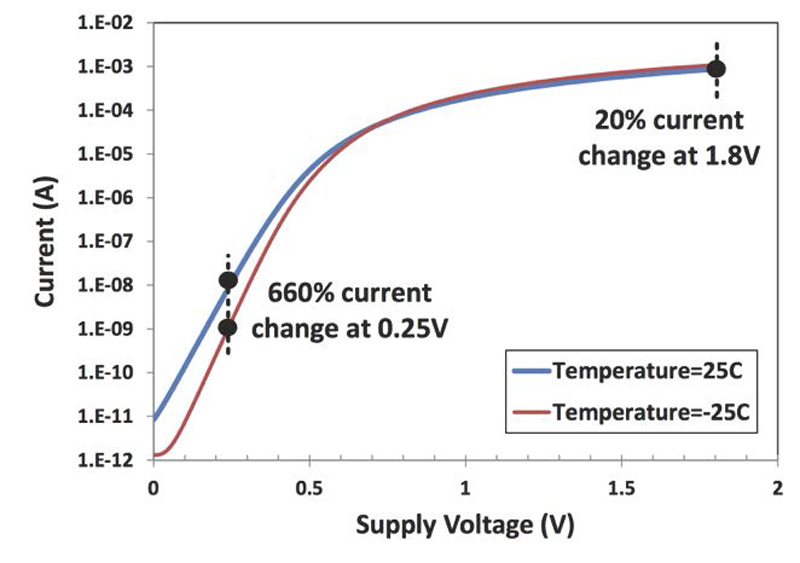

Figure 2 - The on/off current ratio is orders of magnitude smaller in the sub-threshold region

• Manufacturing and operating variances – corner lots are typically used in semiconductor manufacturing to determine the amount of variation the process can tolerate as compared to a die acquired from the nominal process. In a slow process corner the current can be as much as 100 times less than that of the nominal process. In a sub-threshold design, this becomes a significant proportion of the on/off current ratio. In addition, operating conditions, such as temperature, can also have a huge effect on current when operating sub-threshold. As an example, the “off” current at elevated temperatures is similar to that of the “on” current at reduced temperatures, leading to challenges in detecting the transistor state in an uncompensated circuit (Figure 3). This results in extra design effort to ensure that the completed design operates reliably under all specified operating conditions.

Click image to enlarge

Figure 3 – Sub-threshold circuits are exponentially sensitive to temperature

• Characterization and testing – since traditional manufacturing flows are designed and constructed for testing super-threshold silicon products, a new approach had to be found for first characterizing and then testing sub-threshold devices during manufacturing, since the parametric measurement units (PMUs) available were designed to measure microamps of current, and not nano- or picoamps.

With a better understanding of the underlying operational characteristics of transistors in sub-threshold mode from mainstream semiconductor processes, Ambiq Micro then went about redesigning the cells and circuits that used them. The first step was to pare down the cell to understand where sub-threshold transistors would have the largest impact on reducing power consumption. The cells were then redesigned, being careful to manage the extreme sensitivity to the changes in the threshold voltage and operating conditions. In some cases, such as non-volatile memory blocks (NVM), there was little to no advantage in using sub-threshold transistors.

For example, a NVM is typically used to store parameters that are loaded into a register that does use sub-threshold transistors. Since the NVM is typically operated once at device start-up, the NVM and associated data transfer circuit can be implemented using standard super-threshold transistor technology that is then shut-down once it has served it purpose. With this methodology, Ambiq Micro only selects sub-threshold transistor technology for their cells when it makes sense in terms of power-reduction, reverting to the easier-to-design super-threshold technology on the rare occasions where it doesn't.

Starting fresh

Whereas it was relatively simple to convert existing super-threshold digital cells to sub-threshold technology, analog circuits typically demanded a fresh start. The resulting circuits were often substantially different from their super-threshold versions and a disproportional amount of design engineering activity was needed to design and verify them for correct functionality and performance to specification.

The outcome of this intensive research, testing and design activity resulted in the Sub-threshold Power Optimized Technology, or SPOT™, platform. Typically such radical performance improvements demand custom processes or obscure process technologies, but with SPOT the focus has been on making a design library that functions on process nodes that are already known to work well. Most importantly, Ambiq Micro's SPOT technology is well positioned to make use of lower geometry processes as and when they become more mainstream, which will naturally lead to further power savings.

Testing challenges were tackled in a dual-pronged approach. On the one-side, custom probe cards have been developed to handle those measurements that the tester itself cannot handle. On the other, on-chip test circuitry has been implemented to cover the remaining testing needs. The flow for characterization has also be subjected to changes, with a more thorough, detailed set of measurements under significantly more conditions compared to that for a classical super-threshold design. The outcome of this leads to greater confidence in the design and robustness of the resulting products. Additionally, Ambiq's sub-threshold circuits have been subjected to the same battery of reliability tests applied to devices based upon standard silicon technologies, involving multiple lots exposed to extreme conditions over extended time periods as well as other standard tests, such as electrostatic discharge (ESD).

This aggregate approach to sub-threshold design, from transistor characterization through to manufacturing processes and product characterization techniques, ensures that Ambiq Micro's products are indistinguishable from something built upon traditional super-threshold techniques – with the exception of their superior power consumption. The first products to be launched were the Real-Time Clock (RTC) devices AM08xx, and the AM18xx that can additionally cut off ground current on a host microcontroller. Both feature monitoring of main power and can switch to backup power, with key parameters being stored in up to 256B of ultra-low leakage RAM. At 3.0V operating voltage and 25°C, both devices consume as little as 14nA of current when operating from the integrated, power-optimized RC oscillator.