Power Density without Compromise: Designing for Next-Generation FPGAs and SoCs

Semiconductor performance continues to climb at a staggering pace, still echoing the cadence of Moore’s Law — the theory that the number of transistors in an integrated circuit will double every two years.

Figure 1. MicroPOL cross section and SeSUB

Every leap in compute capability, from advanced FPGAs and SoCs to custom ASICs and AI accelerators, comes with steeper demands on power delivery. The challenge is no longer just supplying enough watts. It is doing so within shrinking board space, while maintaining efficiency, reliability, and manageable design complexity.

Traditional point-of-load (POL) regulators, however effective, often force engineers into difficult tradeoffs. Increase power density, and thermal constraints grow unbearable. Shrink size, and design becomes more complex. Simplify the layout, and efficiency tends to suffer. But what if you could have it all instead of making a sacrifice? A new class of substrate-embedded power modules is helping to break the cycle, enabling compact, high-efficiency power delivery that is both thermally robust and fast to design in.

The Power Density Challenge

Modern devices demand dozens of tightly regulated power rails. An FPGA or SoC might require sub-1V supplies at currents above 10A, alongside higher-voltage rails for memory, transceivers, or peripheral logic. Each generation squeezes interconnects closer, increases transient load requirements, and leaves less real estate for the power subsystem.

Discrete POL solutions meet these needs only up to a point. Their reliance on wire bonds, external inductors, and lengthy interconnects adds parasitics that erode efficiency at high switching speeds. More wires and parts often equate to less efficiency. They consume valuable surface area on the board, often leading to compromises in layout or thermal management. As design margins tighten, engineers must get more creative with an extreme focus on efficiency. To do so, they must balance board space, cost, and performance in ways that slow development and limit system capabilities.

Substrate-Embedded Packaging

One way to overcome these limitations is to think outside of the box, taking time to rethink the way power conversion components are packaged. In substrate-embedded modules, regulators, MOSFETs, drivers, and even inductors are built directly into a thin semiconductor embedded substrate (SESUB). This eliminates wire bonds, long a source of parasitic losses, and places every element of the power stage in close proximity.

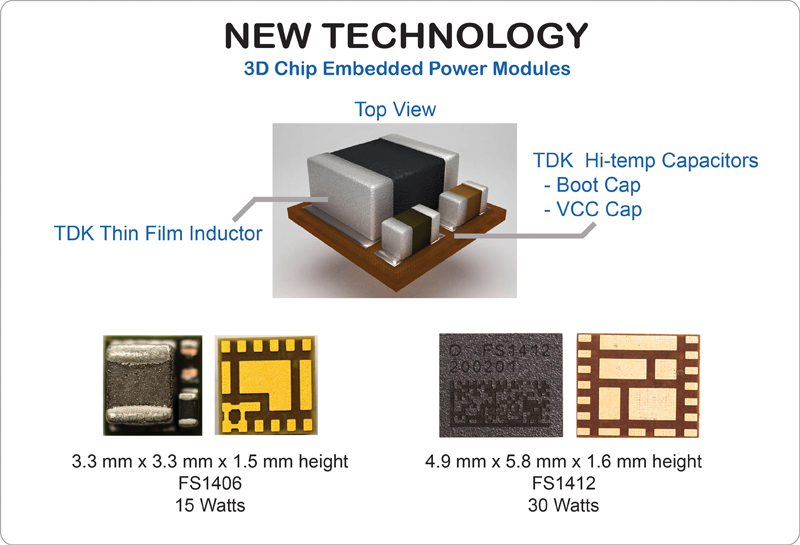

The result is an ultrathin package, often only 1.5 to 1.6 mm in height, that can be mounted on either side of the PCB. Locating the module directly adjacent to the load minimizes interconnect length, reduces noise, and supports faster switching. In many cases, the module can share a heat sink with the device it powers, further saving space.

Integration also improves mechanical reliability by bringing elements closer together. Shock and vibration testing shows these embedded modules withstand the stresses of industrial and mobile environments, from drones to ruggedized edge servers in robust environments.

Managing Thermal Constraints

High power density designs come with challenges that are often accompanied by thermal headaches. Packing more watts into less volume leaves little headroom for heat dissipation, often requiring forced airflow or derating of the current rating. Substrate-embedded power modules address this through patented thermal vias and copper heat-plates embedded in the substrate.

By channeling heat directly from the die through the package into the PCB, these modules achieve massive efficiency and performance leaps: as much as four to eight times better thermal performance than conventional solutions. In practical terms, that means designers can run modules at full rated current without external airflow, even in high-ambient environments.

The difference is especially clear when compared to competing devices of similar size, which often require significant derating as temperatures rise. Robust thermal handling allows embedded modules to deliver up to 1 W per cubic millimeter, such as 15 W in a 3.3 × 3.3 × 1.5 mm footprint, or more than 20 W in a 5.8 × 4.9 × 1.6 mm package.

Ease and Speed of Design

Density and thermal reliability matter little if the solution is too complex to implement. Thoughtful distribution of capacitors on the output is crucial when it comes to minimizing circuit board parasitics that impact the supply of stored energy.

A major benefit of substrate-embedded power modules is how straightforward they are to design in. Connections to each of the power planes, when kept simple and clean, will ensure that there are no lengthy ground loops being created, or schemes that also add a high level of parasitic inductance and/or capacitance. At a basic level, engineers need only identify input and output capacitance, define a voltage divider, and select the module matched to their rail requirements.

Support resources take this simplicity further. Extensive reference designs exist for leading FPGAs and SoCs, covering common rails and tested in collaboration with silicon vendors. Starter schematics and PCB layouts are freely available through Ultra Librarian in formats such as OrCAD, Altium, Mentor, and Eagle. Following these guidelines typically saves 25% to 50% of board space compared to discrete solutions, while minimizing bill-of-materials count.

Modules are available in preset output voltages for the most common rails, but analog-mode versions allow engineers to fine-tune outputs across ranges like 0.6 to 2.5 V or 0.6 to 1.8 V with a simple resistor change. For more advanced designs, digital interfaces such as I²C or PMBus can be used for precise control and monitoring.

Click image to enlarge

Figure 2: New Technology - 3D Chip Embedded Power Modules

Applications and Scalability

The benefits of compact, thermally efficient power delivery extend across industries. In communications infrastructure, high-density modules support 5G base stations, data switches, and edge aggregation devices. In data centers, they power FPGAs and accelerators used in AI training, analytics, and networking. In industrial automation, robotics, and medical imaging, rugged construction and vibration resistance ensure reliable performance.

Scalability is another advantage. While individual modules cover 3 to 12 A outputs, multiphase architectures scale this up dramatically. Current-sharing modules with PMBus support can be paralleled to deliver 200 A or more, enabling them to meet the demands of high-end processors and complex systems. Designers can consolidate multiple rails with common modules, reducing part counts and leveraging economies of scale.

Best Practices for Implementation

As with any power design, careful attention to layout ensures optimal performance. Input capacitors should be placed close to voltage pins to minimize EMI, while output capacitors should be distributed to reduce board parasitics and improve transient response. Adequate thermal vias and sufficient copper weight in the PCB help sustain high currents without exceeding thermal limits.

Engineers are advised to verify voltage divider resistor values with point-of-load measurements and adjust as needed. For applications with high di/dt transients, additional output capacitance may be required, with ESR and ESL values matched to the distribution network. Design support tools and field application engineers are typically available to review schematics, layouts, and thermal strategies before production.

A Path Forward

With continually increasing power demands, semiconductors must continue to push performance boundaries and power delivery must evolve in parallel. Substrate-embedded modules show that engineers no longer need to choose between density, thermal reliability, and design ease—opening a multitude of exciting new innovation opportunities. By combining high integration, patented thermal management, and accessible design tools, these solutions provide a practical path for powering next-generation devices.

From FPGAs in edge servers to ASICs in AI accelerators and beyond, compact embedded modules represent more than an incremental improvement. They offer a new paradigm for how power is delivered, freeing engineers to focus on performance and functionality rather than compromise.