Precision Ultra-Low-Power High-Side Current Sense

The LTC2063’s ultralow input offset voltage, low IOFFSET and IBIAS, and rail-to-rail input, provide precise current measurements from 100 µA to 250 mA.

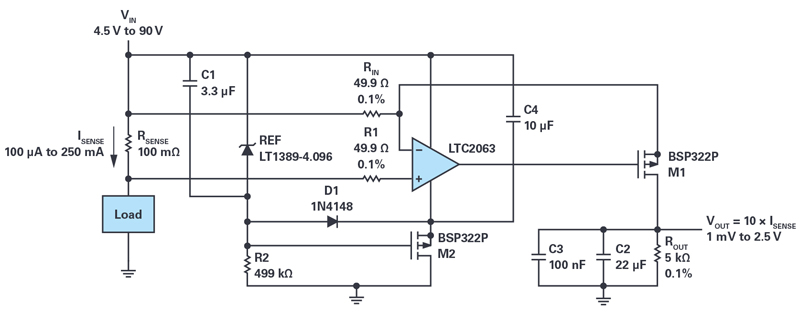

Figure 1. Precision high-side current sense circuit based on the LTC2063 zero-drift amplifier

Precision high-side measurement of microamp currents requires a small value sense resistor and a low offset voltage amplifier. The LTC2063 zero-drift amplifier has a maximum input offset voltage of just 5 µV and draws just 1.4 µA, making it a great choice for building a complete ultra low power, precision high-side current sense circuit, as shown in Figure 1.

This circuit uses only 2.3 µA to 280 µA of supply current to sense currents over a wide 100 µA to 250 mA dynamic range. The exceptionally low offset of the LTC2063 allows this circuit to work with only 100 mΩ of shunt resistance, limiting the maximum shunt voltage to only 25 mV. This minimizes power loss on the shunt resistor and maximizes power available to the load. The LTC2063’s rail-to-rail input allows this circuit to operate with very small load current where input common mode is almost at the rail. The integrated EMI filter of the LTC2063 protects it from RF interference in noisy conditions.

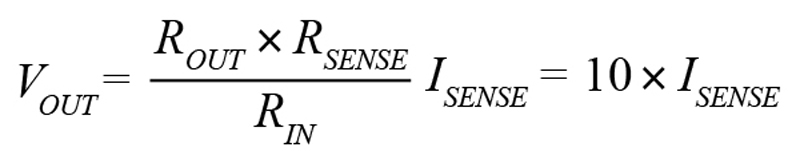

The voltage output of this circuit for a given sense current is:

Zero Point

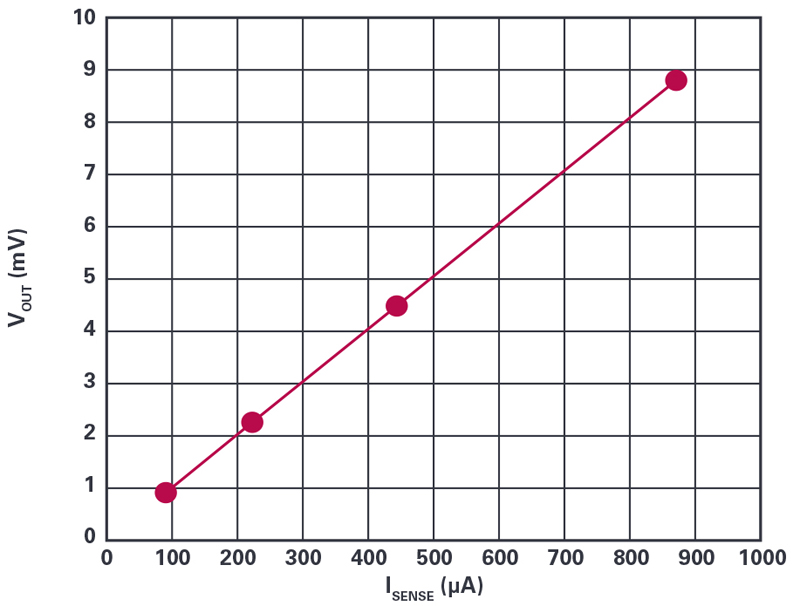

A critical specification for a current sense solution is the zero point, or equivalent error current, at the input for the output produced when no sense current is present. The zero point is generally determined by the input offset voltage of the amplifier divided by RSENSE. The LTC2063’s low input offset voltage of typical 1 µV, maximum 5 µV, and low typical input bias and offset currents of 1pA to 3pA, allow for a zero point input-referred error current of only 10µA (1µV/0.1Ω) typically, or 50µA (5µV/0.1Ω) maximum. This low error allows the sense circuit to maintain its linearity down to the lowest current in its specified range (100µA), without plateauing due to loss of resolution, as seen in Figure 2. The resulting input current to output voltage plot is linear over the entire current sense range.

Click image to enlarge

Figure 2. No plateau at the low end, down to 100 µA ISENSE

Another source of zero-point error is the output PMOS’s zero-gate voltage drain current, or IDSS, a parasitic current that is present for nonzero VDS when the PMOS is nominally turned off (|VGS|=0). A MOSFET with high IDSS leakage will produce a nonzero positive VOUT with no ISENSE.

The transistor used in this design, Infineon’s BSP322P, has an upper-bound IDSS of 1 µA at |VDS| = 100 V. As a good estimate for the typical IDSS of the BSP322P in this application, at room temperature, with VDS = –7.6 V, IDSS is only 0.2 nA, resulting in just 1 µV error output, or equivalent 100 nA input current error, when measuring 0 A input current.

Architecture

The LT1389-4.096 reference, along with the bootstrap circuit composed of M2, R2, and D1, establishes a very low power isolated 3V rail (4.096V+VTH of M2, typically –1 V) that protects the LTC2063 from seeing its absolute maximum supply voltage of 5.5V. Although a series resistance could suffice for establishing bias current, using transistor M2 allows for much higher overall supply voltages while also limiting current consumption to a mere 280 µA at the high end of the supply range.

Precision

The LTC2063’s input offset voltage contributes a fixed input-referred current error of 10 µA typical. Out of 250 mA full-scale input, the offset results in only 0.004% error. At the low end, 10 µA out of 100 µA is 10% error. Since the offset is constant, it can be calibrated out. Figure 3 shows that total offset from LTC2063, unmatched parasitic thermocouples, and any parasitic series input resistances is only 2 µV.

Click image to enlarge

Figure 3. VIN to VOUT conversion on minimum supply 4.5 V for the entire ISENSE range. An output offset of 200.7 μV, when divided by 100.05 V/V voltage gain, implies an RTI input offset of 2 μV

The gain shown in Figure 3, 100.05V/V is 1.28V/V greater than the expected gain given by the actual values of ROUT and RIN when built, or 4.978kΩ/50.4 Ω = 98.77 V/V. This error may be due to parasitic series resistance of around 500 mΩ between the LTC2063’s inputs and RSENSE.

The main source of uncertainty in the output of this circuit is noise, so filtering with large parallel capacitors is crucial to reduce noise bandwidth and thus the total integrated noise. With a 1.5Hz output filter, the LTC2063 adds about 2 µV p-p low frequency, input-referred noise. Averaging the output over the longest possible duration further reduces error due to noise.

Other sources of error in this current sense circuit are parasitic board resistance in series with the RSENSE at the LTC2063 input, tolerance in resistance values of the gain-setting resistors RIN and ROUT, mismatched temperature coefficients in the gain-setting resistors, and error voltage at the op amp inputs due to parasitic thermocouples. The first three sources of error can be minimized by using Kelvin sense, 4-lead sense resistors for RSENSE, and using 0.1% resistance with similar or low temperature coefficients for the critical gain-set path of RIN and ROUT. To cancel out the parasitic thermocouples at the op amp inputs, R1 should have the same metal terminals as RIN. Asymmetric thermal gradients should also be avoided as much as possible at the inputs.

The overall contribution of all the error sources discussed in this section is at most 1.4% when referenced against full-scale 2.5 V output, as shown in Figure 4.

Click image to enlarge

Figure 4. The percent error remains below 1.4% for the entire range of readings

Supply

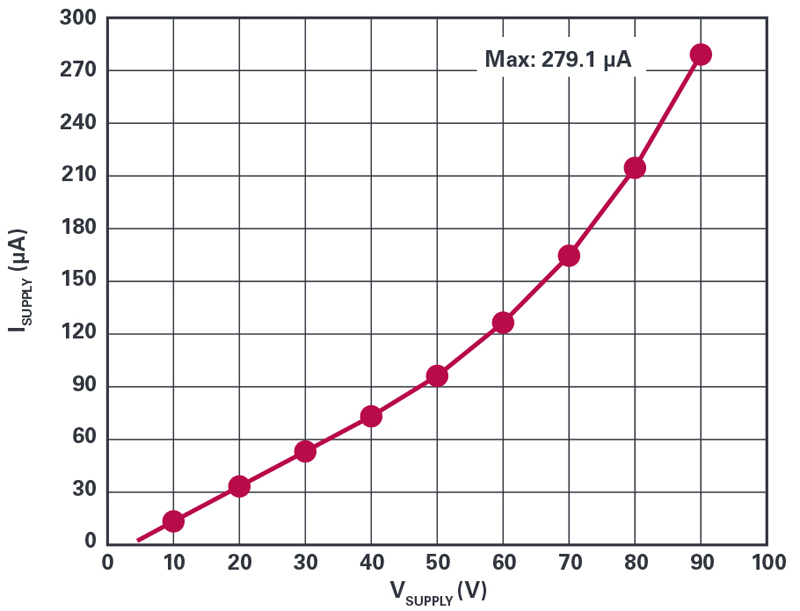

The minimum supply current required by the LT1389-4.096 and LTC2063 is 2.3µA at the minimum VSUPPLY and ISENSE (4.5 V and 100 µA), up to 280 µA at maximum VSUPPLY and ISENSE (90 V and 250 mA), as shown in Figure 5. In addition to the current consumed by the active components, an output current IDRIVE through M1 also supplied by VSUPPLY is required, proportional to the output voltage, ranging from 200nA for a 1.0mV output (for 100µA ISENSE) to 500µA for a 2.5V output (for 250mA ISENSE). Thus, the total supply current in addition to ISENSE ranges from 2.5 µA to 780 µA. ROUT is set at 5 kΩ for a reasonable ADC drive value. In this architecture, the maximum supply is set by the maximum |VDS| that the PMOS output can withstand. The BSP322P is rated for 100 V, so 90 V is an appropriate operating limit.

Click image to enlarge

Figure 5. Supply current increases with supply voltage but never surpasses 280 μA

Output Range

This design can drive a 5kΩ load, which makes it a suitable stage for driving many ADCs. The output voltage range is 0 V to 2.5 V. Since the LTC2063 has rail-to-rail output, the maximum gate drive is only limited by the LTC2063’s headroom. It is 3V typically in this design, set by the LT1389-4.096’s 4.096V plus the –1 V typical VTH of M2.

Since the output of this circuit is a current, not a voltage, ground or lead offset does not affect accuracy. Thus, long leads can be used between the output PMOS M1 and ROUT, allowing RSENSE to be located near the current being sensed while ROUT is near an ADC and other subsequent signal chain stages. The drawback of long leads is increased EMI susceptibility. 100nFC3 across ROUT shunts away harmful EMI before it reaches the next stage’s input.

Speed Limits

Since the LTC2063’s gain-bandwidth product is 20 kHz, it is recommended to use this circuit to measure signals 20 Hz or slower. The 22 µF C2, in parallel with the load, filters the output noise to 1.5 Hz for improved accuracy and protects the subsequent stage from sudden current surges.