The right cabling is critical to enhancing both throughput and quality

In Part 1 of this article we had a short overview of some of the challenges associated with high-volume testing of power semiconductors, and the test throughput advantages that source measure unit (SMU) instruments offer for these applications. Test systems of this type must be optimized for high throughput without sacrificing measurement integrity, which includes selecting appropriate cabling and minimizing the impact of communication time between instruments on overall test time.

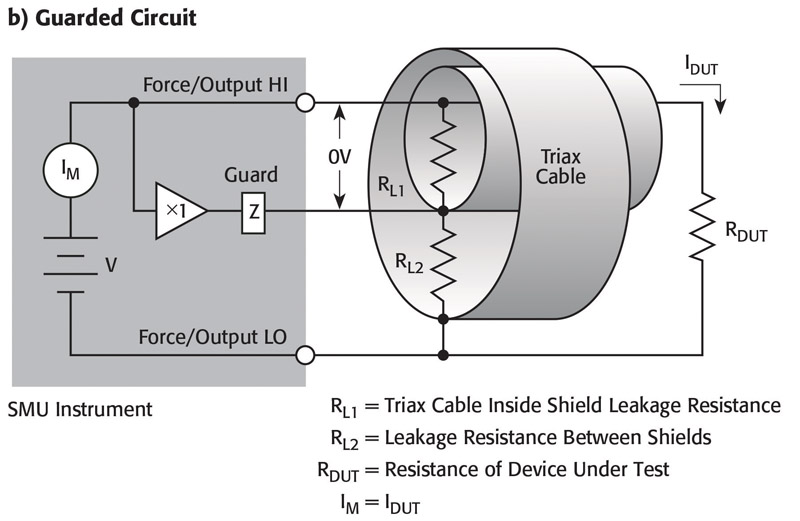

Choosing the right cabling is critical to enhancing both test throughput (by allowing fast charge and discharge times) and overall measurement quality. Traditional high voltage test systems have used coaxial or SHV cabling. However, triaxial or high voltage triaxial cabling offer superior performance. In Figure 1a, the coaxial cable has some resistance from the signal line to ground. This causes a parallel current path, which has an impact on the RC time constant of the circuit. This slows down settling times, thereby slowing down overall test times. In addition, this parallel leakage path limits the low current measurement resolution of the system. In contrast, the triaxial cable in Figure 1b has an extra inner shield that connects to the driven guard of the SMU instrument. This driven guard will force the voltage between the signal line and the inner shield to zero, thereby eliminating all but a tiny amount of leakage current. This enables better RC time constant response, faster settling times, lower current leakage, and better measurement resolution.

Click image to enblarge

Figure 1a: Coaxial cabling vs. triaxial cabling

Click image to enlarge

Figure 1b: Coaxial cabling vs. triaxial cabling

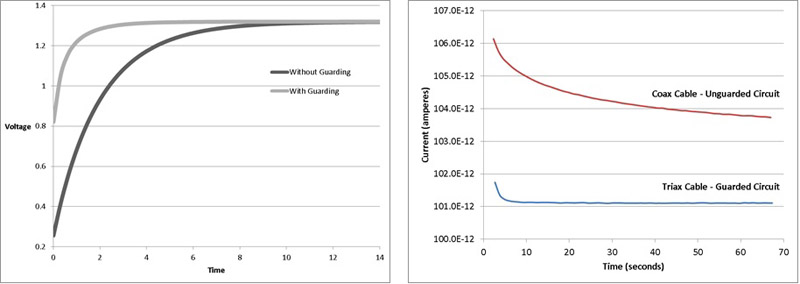

Figure 2 illustrates the advantage of triaxial cabling over coaxial cabling for high throughput applications. The left diagram compares settling times when sourcing voltage without guarding (with coaxial cabling) and with guarding (with triaxial cabling). The right diagram compares settling results when measuring current. Note that in both cases, settling time can be greatly reduced (over 5x better) by using the SMU instrument’s driven guard and triax cabling.

Click image to enlarge

Figure 2: The impact on settling time of triax cabling vs. coaxial cabling

Optimizing speed

Enhancing system-level throughput requires considering and optimizing all elements of speed. This includes program execution time, controller communication time, trigger in time, range change time, function change time, source settling time, A/D converter (NPLC) measurement speed, discharge time, measurement communication and storage time, Hi/Lo limits, and trigger out time.

Often, however, the largest contributor to test time is the time it takes for the test instrument to communicate with the PC controller. Whenever a measurement setup or a parameter changes, it typically adds some communication time to the overall test time and this communication time adds up with each device tested. Fortunately, a technique known as embedded test scripting offers a way to minimize the impact of this communication time on overall test time.

In this technique, the test program is stored in and executed from the instrument rather than from the PC controller. The embedded test script controls sourcing, measuring, math calculations, test sequence flow, branching, limit testing, measurement storage, etc. This eliminates most of the traffic between the instrument and the controller, dramatically improving test throughout.

Embedded test scripting is also useful for creating custom functions specific to an application, such as binary search or sweeping with power compliance, as well as other device specific parameters. This approach can reduce the average test time per part by more than 2x.

Implementing parallel test (i.e., testing multiple devices simultaneously) can optimize test times still further by multiplying the number of parts tested per prober touchdown. The key, however, is to minimize any idle times and data transfer times for all of the SMU instruments in the systems. This requires the use of distributed control.

In a traditional test system, the test program resides on the PC controller and its CPU controls multiple SMU instruments via GPIB or another communications bus. This concept is similar to how an SMU card/mainframe system operates, except that in that case, the GPIB is replaced with a proprietary backplane.

In a distributed test system, the SMU instrument’s embedded test script processor capability is taken one step further and is distributed and synchronized across multiple instruments through an inter-unit communication and triggering bus. This approach offers the triggering and timing of a mainframe-based system but without the plug-in slot limitations, output power limitations, or throughput delays that come with sharing a single CPU’s processing power.

In the distributed scenario, there is one CPU per SMU instrument, so there is no need for one SMU instrument to sit idle while the other SMU instrument communicates with the host CPU. All the SMU instruments work together as a coordinated system to optimize throughput, configurability/modularity, and power capabilities.

Distributed control

Distributed control is necessary in parallel test to minimize any idle times and data transfer times of all SMU instruments in the system. All the data from all the SMU instruments can be transferred back to the host computer at once, further boosting throughput. Transferring data at the end of the full test sequence (during prober indexing or wafer indexing) is possible because the embedded test script processor can perform high-low limit analysis and communicate with the prober via digital I/O after each measurement is complete. Data need not be transferred back to the host CPU for this decision-making and control.

The technology behind optimizing high volume power semiconductor testing is still evolving, but test approaches that combine distributed control capabilities with embedded test scripting show the greatest promise in slashing test times. When used intelligently, these techniques can slash per-part test times to roughly one-quarter of the times possible using traditional testing approaches.

Optimizing high-volume power semiconductor test (Part 1)