Ultra-Low-Power Edge Processing: Redefining What's Possible in Always-On Intelligence

From wearables to drones, how milliwatt-scale intelligent processing is reshaping performance, endurance, and design freedom

Figure 1: Side-by-side comparison of cloud-based vision processing vs the instant result of an Edge AI camera

Since the global mainstreaming of generative AI in late 2022, AI now curates TikTok and Instagram, personalizes shopping on Amazon, helps us navigate in Google Maps, powers real-time translation, enables biometric authentication, and flags fraud in financial systems. AI is a daily utility, silently shaping our choices, habits, and behaviours. For researchers, it enables breakthroughs across physics, biology and climate science.

This massive growth has largely been powered by systems that rely on sending data from edge devices (phones, sensors, wearables, cameras, vehicles) to distant servers for processing, and then returning the results. Centralized cloud AI has served us well so far, but it carries increasing costs: latency, energy consumption, bandwidth limitations, privacy concerns, and dependence on constant connectivity.

That’s where edge AI comes in — bringing AI closer to the data source itself and empowering devices to ‘think’ where the data is born. This technology is already moving toward “always-on” operation where devices listen, sense or perceive continuously. However, doing so within micro- to milliwatt power envelopes is a major design challenge. Engineers face a dilemma when real-time AI at the edge butts up against power budgets that demand sub-milliwatt operation.

Traditional solutions rely on either high-power system-on-chips (SoCs), bulky batteries, external memory, shared accelerators or cloud offload which create bottlenecks in latency, risk privacy and drain energy. A decentralized, efficient and context-aware form of intelligence that lives on the device; enabling fast, private, low-power decision-making (with minimal dependence on the cloud) is the goal.

In this article, we explore how next-generation system-on-chip (SoC) architectures are overcoming those barriers through efficient deep-learning accelerators and fine-grained power management. By running inference locally on specialized cores that can move from ‘asleep to awake’ in microseconds, and using on-chip memory intelligently, these designs minimize data movement and wasted cycles. The result is sustained, real-time AI with consistent latency — even on small batteries.

Challenges of always-on AI in edge devices

Today, AI mostly lives in the cloud. Data is captured by sensors on edge devices like drones, hearable technology, or wearables and transmitted to remote data centers. AI models then process it and send the results back to the device. This works well when speed isn’t critical and connectivity is stable, or where significant AI capabilities are required (as in the case of Generative AI). However, we live in a world where immediacy is more and more essential for real-time sensing, recognition, and control under strict power and latency limits, the time delay of cloud processing isn’t going to cut it.

Edge AI exists because the real world doesn’t tolerate the delays, costs and privacy risks of streaming every bit of sensor data off to a distant cloud. By incorporating AI processing on-chip, devices can bypass these issues by processing data directly locally rather than sending it to remote data centers.

The edge AI advantage

Efficient accelerators drive ultra-low power, which we can see clearly with a comparison of cloud-based and edge AI for a vision-based AI application like real-time security camera doing person detection.

For example, a typical cloud-based solution captures high-resolution 1080p or 4K resolution images and transmits them to cloud servers. This requires megabytes-per-second of bandwidth to achieve ~92% accuracy. Unfortunately, it comes with the cost of latency (150–300 ms, but usually amortized by pipelining to increase the frames per second), high energy consumption (~2–3 joules per inference), and potential privacy risks, especially in regulated environments like healthcare or smart homes.

By deploying significantly smaller and highly-optimized AI models (e.g., quantized MobileNet-SSD) directly onto specialized low-power chips, edge AI addresses these challenges. While these models trade off some accuracy (82–88%), they drastically reduce latency (<10 ms) and reduce energy consumption to a few millijoules per inference. Plus, they eliminate the need for data transfer to achieve real-time, energy-efficient and privacy-preserving inference.

Speed efficiency with edge AI

It boils down to distance. Traditional processing methods ship out and process data before results come back to the device. By managing data locally, milliwatt-scale intelligent system-on-chip devices dramatically reduce latency and power consumption. Made possible by advances in model compression, quantization and hardware-software co-design, we no longer experience constraints by power, latency or privacy. This increased efficiency opens the door for always-on intelligence in wearables, drones and predictive maintenance-dependent systems.

Edge AI runs on stacks with smaller, specialized models. Their architectures are optimized for energy, memory and latency. They feature co-ordinated hardware that can operate within tight constraints, often without active cooling or constant power.

Efficiency with on-board memory

Certain inferences within edge devices rely so heavily on processing and AI that efficiency increases when computed locally. This philosophy is the fuel behind design objectives that pursue the goal of exploiting locality and reducing data footprint — energy spent moving bytes is minimized so it can prioritize doing arithmetic.

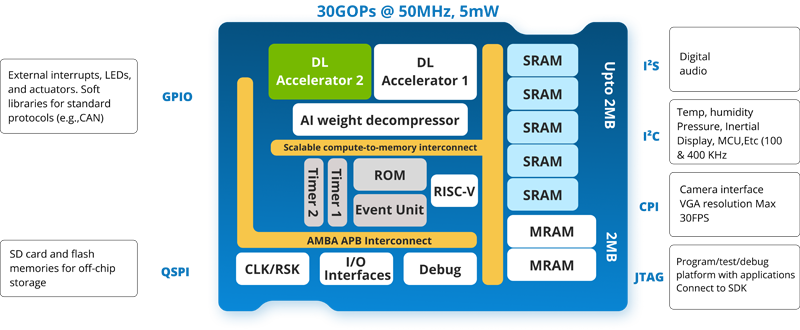

EMASS adopted a memory-centric microarchitecture where compute and memory are interwoven. This gave way to a very efficient AI acceleration module that exists as a compact, optimized, acceleration fabric purpose-built for micro-edge workloads. This allows functions to run locally where they are compressed to avoid negating the energy gains from near-memory or CIM approaches. Device non-idealises are managed as part of the architecture, not as an afterthought.

Architectural foundations of SoC

Bringing the entire necessary system on chip enables always-on, milliwatt-scale intelligence for edge devices that eliminates the need for cloud-based computation. With this design, devices will be able to bring more speed and security to the extreme edge, an area currently occupied by compact and lightweight connected devices powered by small batteries. It fuels products that need more efficiency, not more battery.

Click image to enlarge

Figure 2: ECS-DoT system-on-chip block diagram

Some key Edge AI use cases

These applications also operate within regulatory and commercial constraints, such as healthcare privacy requirements or the uptime demands of industrial IoT, making efficient, always-on edge AI particularly valuable.

Wearables and Healthcare

From smart watches with gesture recognition biometric monitoring to patient monitoring devices that continually track vital signs, better edge AI can deliver better quality of life. In the different environments where these battery constrained devices live, it’s essential to produce enough power over long durations to deliver true constant sensing with skin-safe temperatures. Bringing the processing on-board adds efficiency to arrhythmia detection, gait monitoring, sleep stage classification, and more, while on-chip computing reduces data costs.

Click image to enlarge

Figure 3: Power consumption vs. latency comparison chart

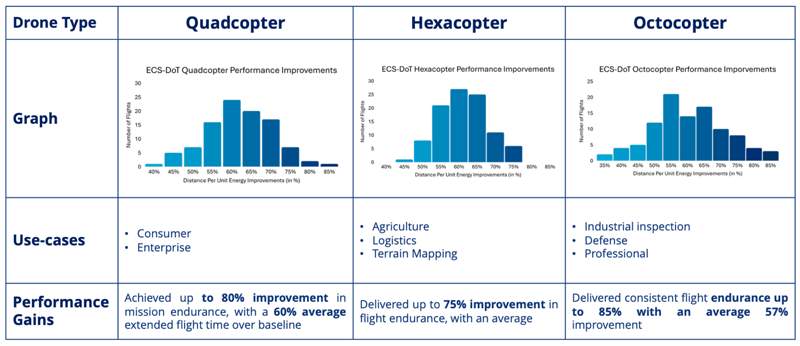

Drones and Robotics

Improving drone flight time is key to tapping into greater capabilities for these revolutionary devices. When drone flight duration can be directly correlated to drone weight and how it affects battery life, the use for better edge AI power is clear. By improving SoC technology, drones can feature lighter, smaller power systems to reduce their thermal footprint. This lower battery weight opens payload or cost-saving options, and can deliver a 60% increase in flight endurance, plus 20% more distance per watt. Not to mention that making drones more self-sufficient with SoC power and processing can reduce connectivity and latency issues. The possibilities for drones and robots increases drastically when the chip’s design and power gating fuels better power management.

Click image to enlarge

Figure 4: Endurance vs. power trade-off for drones

Predictive Maintenance

In the field, deployed sensors need to run for years on constrained batteries. More efficient power usage ensures these devices need less maintenance. By enabling always-on anomaly detection, vibration analysis, and motion classification without cloud dependency, designers can ensure reliable local inference even in environments without connectivity. Plus, you can detect faults early to prevent costly downtime.

What’s next for edge AI

It’s not just about smaller models or lower power chips. The future of edge AI’s depends on architectures built intentionally for the micro edge. By extending design principles into a chip that delivers real benefits in the field, it begs the question: What becomes possible when intelligence can run continuously at sub-milliwatt levels?

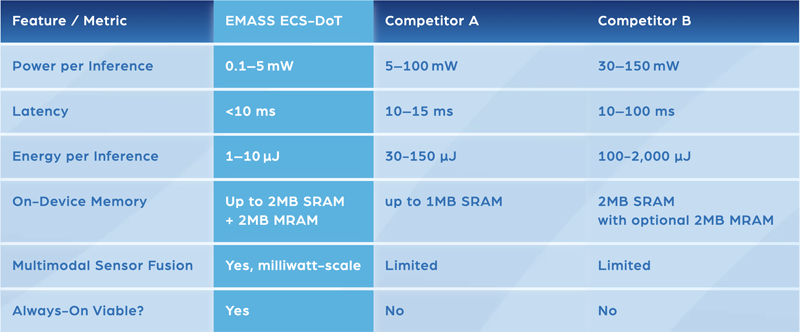

To answer a question with a question: What can you imagine? ECS-DoT is the architecture that ushers forth a future where engineers no longer need to compromise between performance and power, they can design for power-first, latency-aware AI systems. It operates up to 93% faster while consuming 90% less energy while eliminating the need for cloud processing by supporting true multimodal sensor fusion on-device. With the freedom to build smaller, faster, and smarter systems under strict energy constraints, the possibilities for wearable healthcare, industrial IoT, smart cities, and much more are nearly limitless.

In a simple, radically efficient package, ECS-DoT not only redefines what’s possible today but is a proof point for what’s achievable when architectures are designed for always-on, ultra-low-power AI.